#### Departamento de Engenharia Elétrica e de Computação - EESC-USP

#### SEL-0415 Introdução à Organização de Computadores

# Aula de Exercícios 2a Prova : 1º Parte Lógica de Seleção

Profa. Luiza Maria Romeiro Codá

#### Exercício 1:

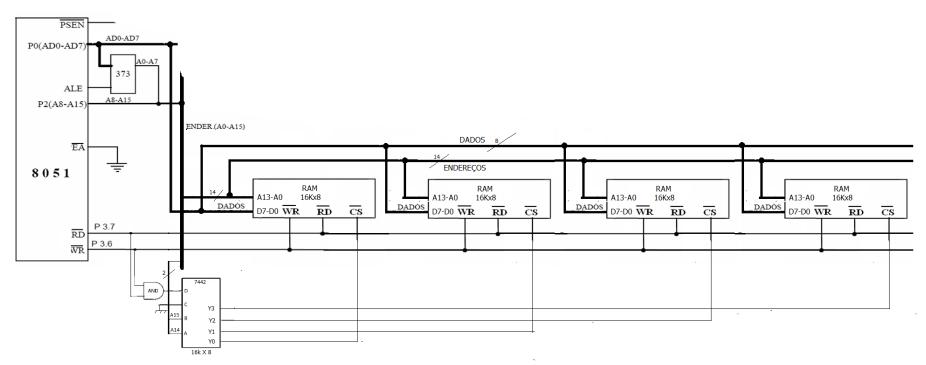

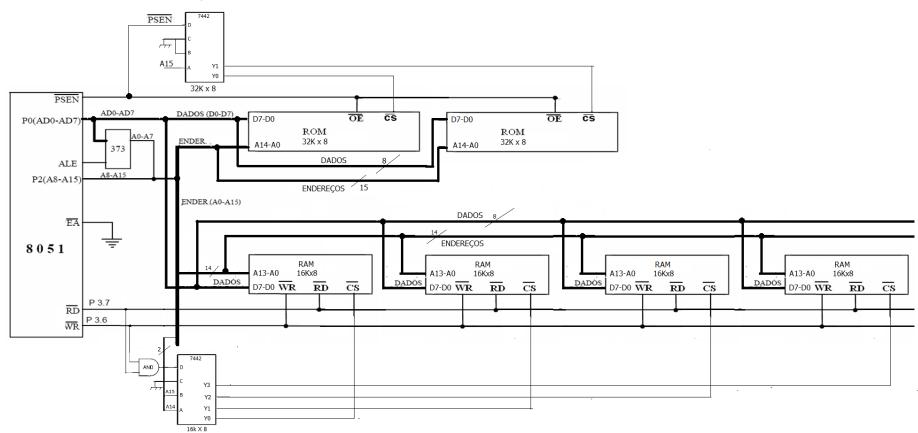

Faça um projeto completo da lógica de seleção absoluta para o espaço de memória para interligar o microcontrolador 8051 com memórias RAM (externas) de 16Kx8, de forma a preencher todo o espaço de endereços para memória de dados (RAM).

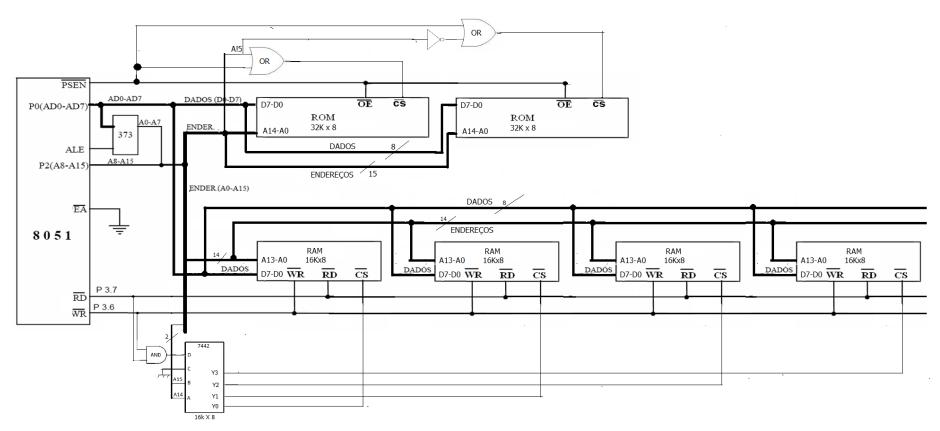

E, com CIs de memórias do tipo EPROM de 32Kx8, preencha todo o espaço de endereços para mapeamento de memória de programa, utilizando apenas EPROM externa.

Utilize qualquer um dos decodificadores 74138, 7442 ou 74154.

Obs: Lembrar que a porta paralela P0 é utilizada como duto multiplexado para os 8 bits menos significativos do endereço (A7 a A0) e os 8 bits de dados(D7 a D0). O sinal ALE enviado pelo micro define se a porta contém endereços ou dados (ALE = 1 endereços e ALE = 0 dados).

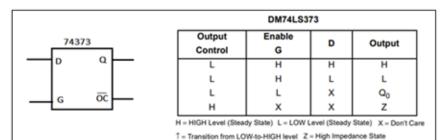

# Exercício 1: Informações sobre os Cls

Q<sub>0</sub> = The level of the output before steady-state input conditions were established.

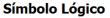

**Decodificador 74138**

|    |                | INP            | UTS            |                |                |                |    |    | OU. | TPUTS |    |    |    |

|----|----------------|----------------|----------------|----------------|----------------|----------------|----|----|-----|-------|----|----|----|

| E, | E <sub>2</sub> | E <sub>3</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | O <sub>0</sub> | ō, | Ö2 | Ö3  | Ö4    | Ŏς | O6 | Ŏ, |

| н  | х              | X              | Х              | Х              | Х              | н              | н  | н  | н   | н     | н  | н  | Н  |

| ×  | н              | X              | X              | X              | X              | н              | н  | н  | н   | Н     | Н  | н  | н  |

| ×  | X              | L              | X              | X              | X              | н              | н  | н  | н   | н     | н  | н  | н  |

| L  | L              | н              | L              | L              | L              | L              | Н  | н  | Н   | Н     | Н  | н  | Н  |

| L  | L              | н              | н              | L              | L              | н              | L  | н  | Н   | Н     | Н  | H  | н  |

| L  | L              | н              | L              | н              | L              | н              | н  | L  | н   | н     | н  | н  | н  |

| L  | L              | н              | н              | н              | L              | н              | н  | н  | L   | Н     | H  | H  | н  |

| L  | L              | н              | L              | L              | н              | н              | н  | н  | н   | L     | н  | н  | н  |

| L  | L              | н              | н              | L              | н              | н              | н  | н  | н   | н     | L  | н  | н  |

| L  | L              | н              | L              | н              | н              | н              | н  | н  | н   | н     | н  | L  | н  |

| L  | L              | н              | н              | н              | н              | н              | н  | н  | н   | н     | н  | н  | L  |

#### Exercício 1:

#### Microcontrolador 80C51

#### Organização das Memórias na família MCS-51

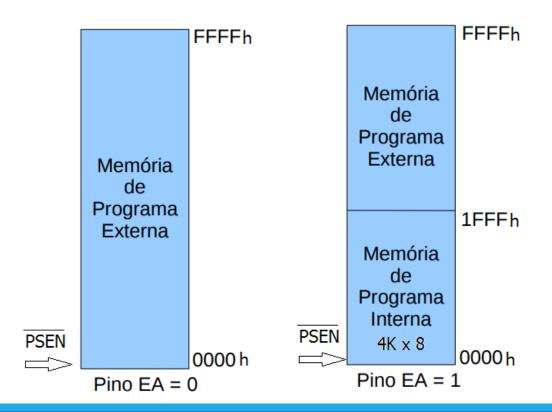

#### MEMÓRIA DE PROGRAMA

#### Endereço das Memórias de Programa interna e externa

| Rom Interna<br>EA = Vcc | Endereçamento Interno | Endereçamento<br>Externo |

|-------------------------|-----------------------|--------------------------|

| 4 K                     | 0000h a 0FFFh         | 1000h a FFFFh            |

| 8 K                     | 0000h a 1FFFh         | 2000h a FFFFh            |

| 16 K                    | 0000h a 3FFFh         | 4000h a FFFFh            |

| 32 K                    | 0000h a 7FFFh         | 8000h a FFFFh            |

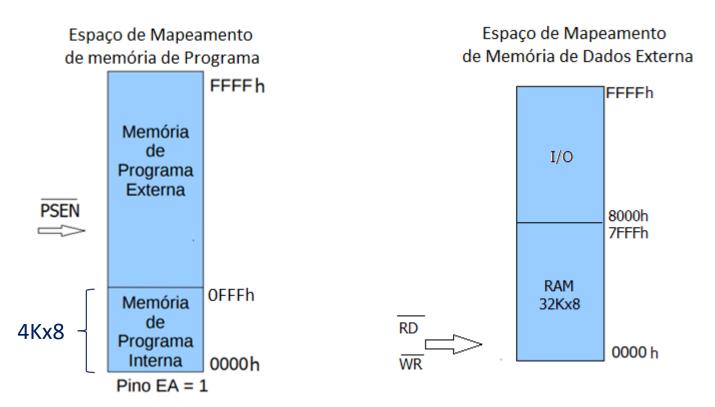

Se EA = 0 → toda a memória de programa é externa : 0000H a FFFFH

Mapeamento EEPROM externa:

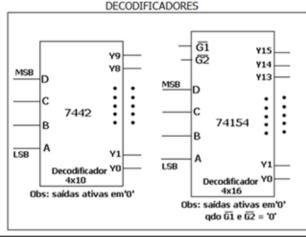

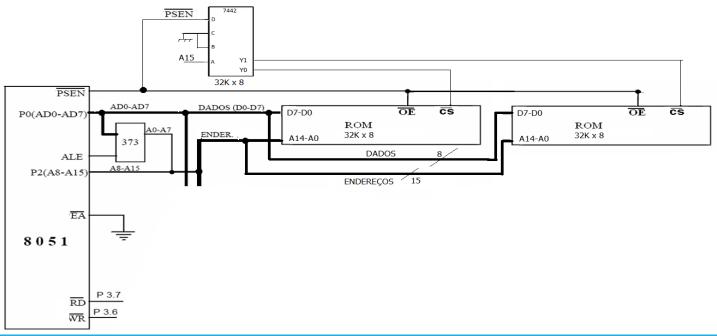

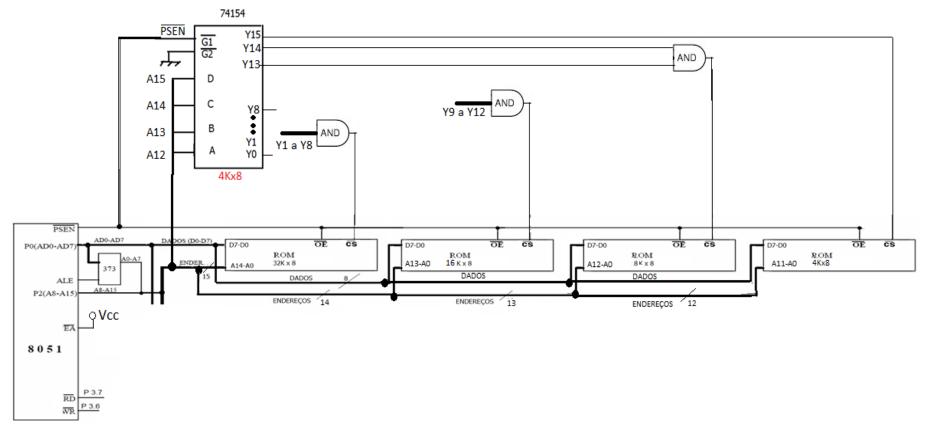

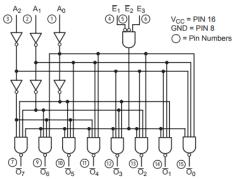

Para utilizar apenas EPROM externa a entrada EA do microcontrolador 8051 deve ser ligada ao terra (EA =0). E o sinal de controle que seleciona esse espaço é PSEN

Para preencher todo espaço de endereçamento de memória de Programa do 8051 que é de  $64Kx8 = 2^{16} = 2^6 x 2^{10}$ , deve-se utilizar 2 chips de EEPROM de 32Kx8, utilizando apenas EPROM externa.

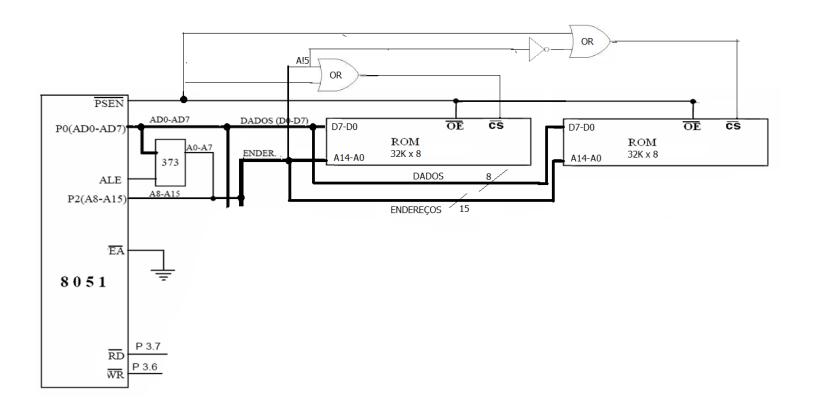

Pode-se utilizar um decodificador (7442) ou apenas portas OR para ligar o bit de seleção A15 (que não entra no endereçamento da memória), sendo de 32K =2  $^{15}$  = 2  $^{5}$  x 2  $^{10}$  apresenta enderecamento de A0 a A14. ou seia. 15 linhas de enderecos .

2ª maneira: Seleção de EEPROM usando portas OR

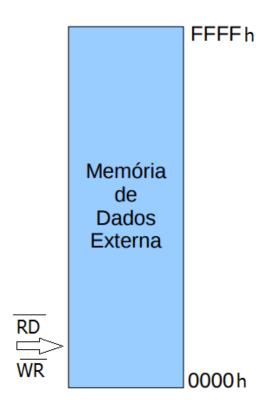

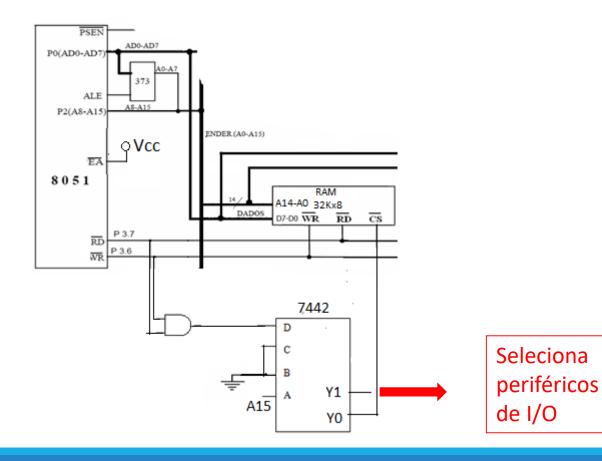

O espaço de RAM externa do 8051 é de 64Kx8 selecionado pelos sinais de controles RD e WR.

Para preencher todo o espaço de endereçamento de RAM externa de 64Kx8 usando Chips de RAM de 16Kx8 são necessárias 4 Chips.

Utiliza-se um decodificador 7442 para dividir o espaço que seleciona a RAM externa em 16Kx8.

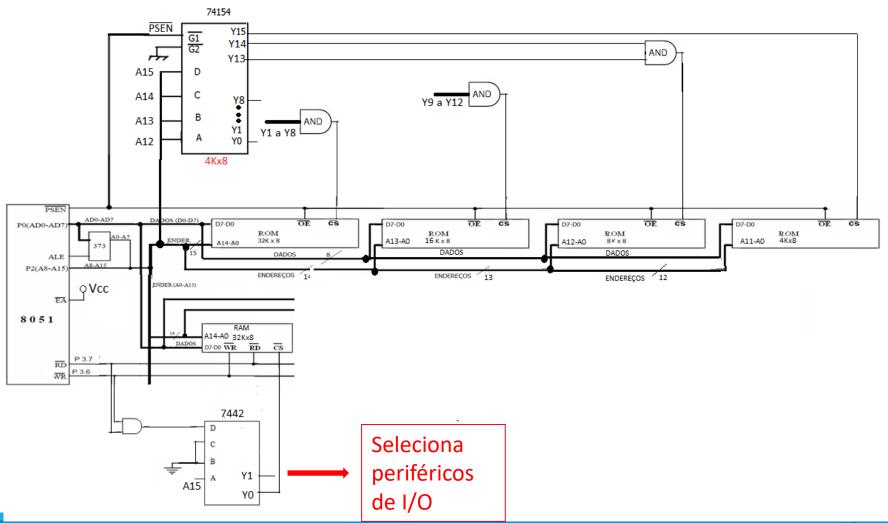

#### Circuito 1 completo:

#### Circuito 2 completo:

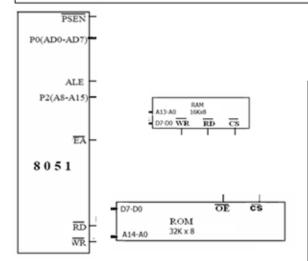

#### Exercício 2:

- Faça um projeto de lógica de seleção NÃO ABSOLUTA completo interligando o microcontrolador 8051 à memórias externas do tipo EPROM, de forma a preencher todo o espaço de endereços que o 8051 reserva para memória de programa, incluindo a EPROM interna de 4Kx8. Utilize organizações de memória EEPROM apropriadas

- Preencha todo o espaço do 8051 de 64Kx8, reservado para mapeamento de memória de dados externa (RAM) de tal maneira que posicione uma RAM de 32Kx8 nos endereços mais baixos, e no espaço restante reserve para mapear PERIFÉRICOS(I/O).

Utilize qualquer um dos decodificadores 74138, 7442 ou 74154.

Obs: . Lembrar que a porta paralela P0 é utilizada como duto multiplexado para os 8 bits menos significativos do endereço (A7 a A0) e os 8 bits de dados(D7 a D0). O sinal ALE enviado pelo micro define se a porta contém endereços ou dados (ALE = 1) endereços ou dados (ALE=0).

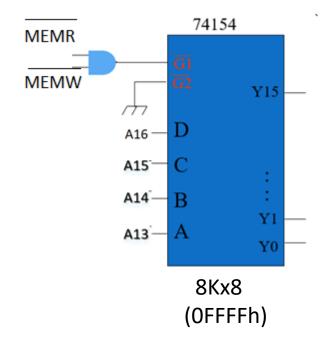

#### Exercício 2:

#### Espaços de mapeamento de memóriado 8051

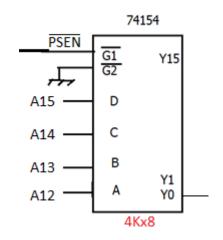

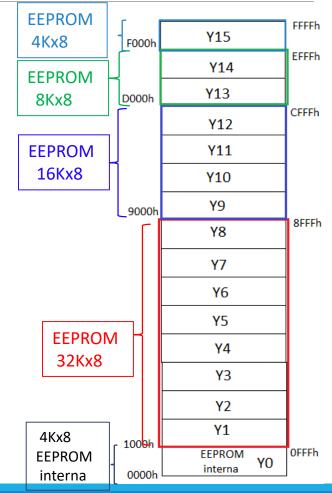

Utiliza-se o decodificador 74154 para dividir o espaço de memória de Programa de 64Kx8 em espaços de 4Kx8

| Y15        |

|------------|

| Y14        |

| Y13        |

| Y12        |

| Y11        |

| Y10        |

| <b>Y</b> 9 |

| Y8         |

| Y7         |

| <b>Y</b> 6 |

| <b>Y</b> 5 |

| Y4         |

| Y3         |

| Y2         |

| Y1         |

| Y0         |

|            |

Para preencher todo o espaço de mapeamento de memória de programa externa do 8051, que é 60Kbytes, pois 4Kbytes são preenchidos pela memória EEPROM interna, utiliza-se 4 chips de memória de: 32Kx8, 16Kx8, 8Kx8 e de 4Kx8, cujo total dá 60Kx8. E o mapeamento fica:

#### Circuito Mapeamento de Memória de Programa:

Circuito Mapeamento de Memória de Dados:

Lógica de Seleção completa:

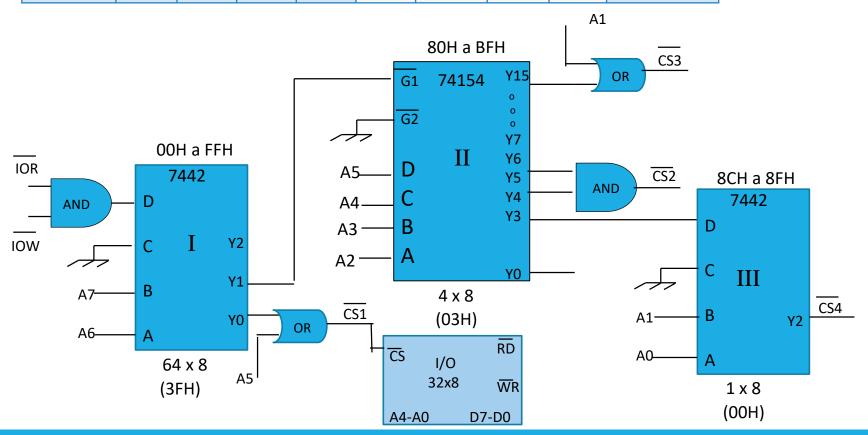

#### Exercício 3:

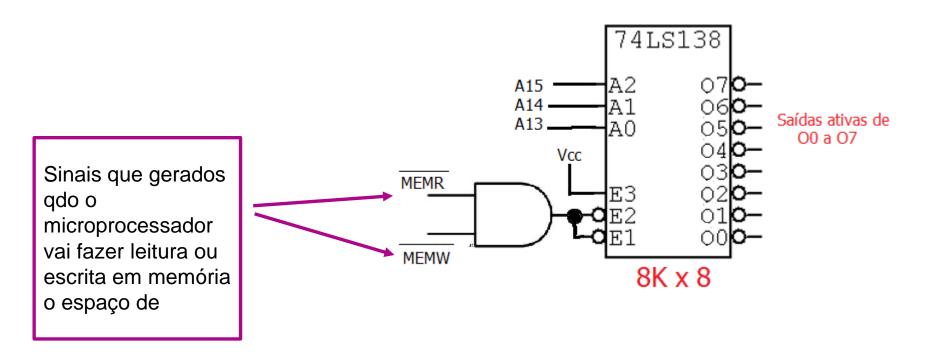

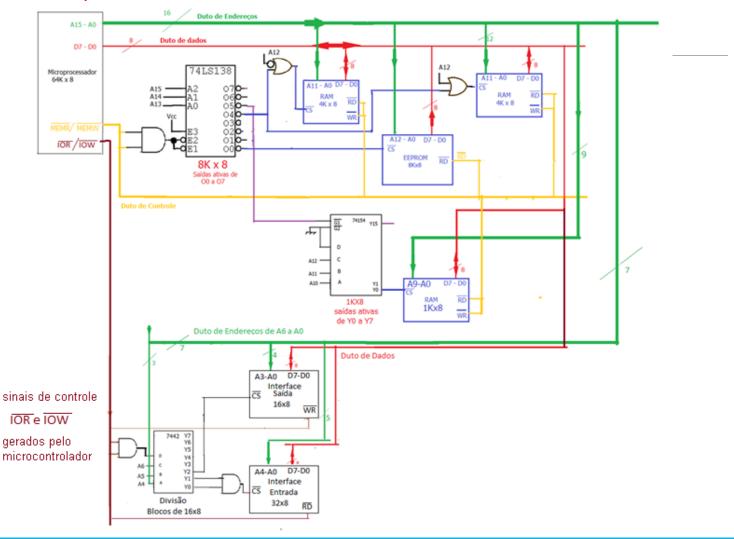

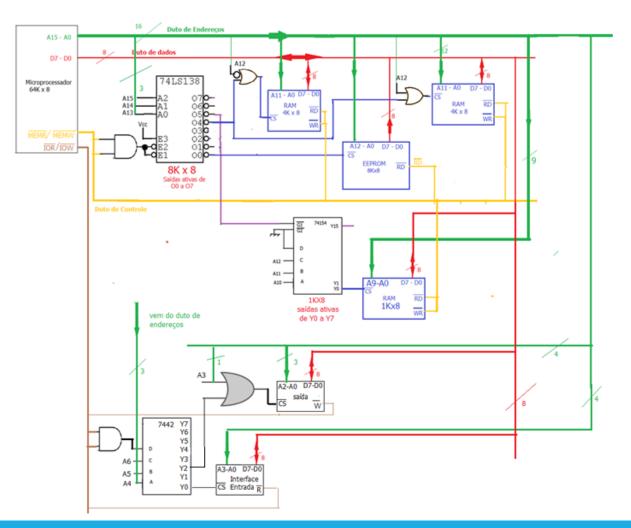

Considerando um microprocessador de 16bits de linhas de endereço e 8 bits no duto de dados e com mapeamento em I/O isolado, onde os sinais MEMR e MEMW selecionam o espaço de mapeamento de memória de 64K x 8 e os sinais IOR e IOW selecionam o espaço de mapeamento de I/O de 128 x 8 :

- **3.1** Faça o projeto da lógica de seleção para dividir o espaço de endereçamento desse microprocessador reservado apenas para **mapeamento de memória**, em blocos de 8Kbytes, utilizando o decodificador 74138; Esse espaço é selecionado com os sinais de controle MEMR e MEMW, qdo o microprocessador for fazer uma leitura ou escrita, respectivamente em memória;

- 3. 2. Desenhe o mapa dos endereços especificando endereço inicial e final de cada bloco de saída do 74138;

- **3.3** utilizando decodificadores 7442 ou 74154, desenhe o projeto da lógica de seleção para o espaço de endereçamento de memórias que divide o espaço que contém o endereço A7BFH em espaços de 1Kx8;

- **3.4**.No espaço de endereçamento de memórias externa do microprocessador posicione as memórias indicando faixa de endereços que ocupam (seguindo as regras corretas) para ligar três memórias RAMs, duas de 4Kx8 e outra de 1Kx8, uma memória EEPROM de 8Kx8, de tal maneira a fazer lógica de seleção absoluta.

- 3.5. Desenhe o circuito lógica de seleção Absoluta para o espaço de mapeamento em memória do item 3.4

### Exercício 3 (continuação):

Considerando um microproces<u>sador</u> de <u>16bits</u> de linhas de endereço e 8 bits no duto de dados e com mapea<u>me</u>nto e<u>m</u> I/O isolado , onde os sinais MEMR e MEMW selecionam o espaço de mapeamento de memória e os sinais IOR e IOW selecionam o espaço de mapeamento de I/O:

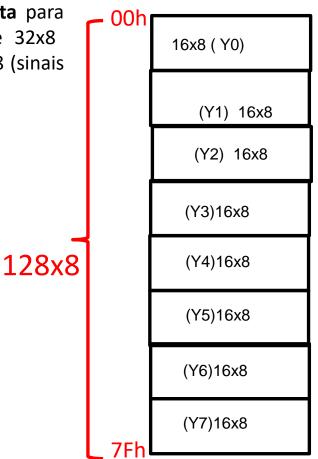

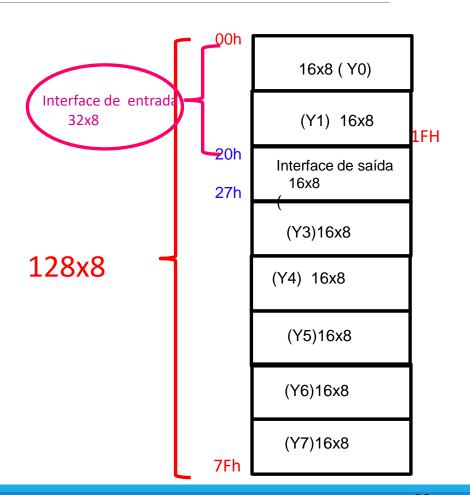

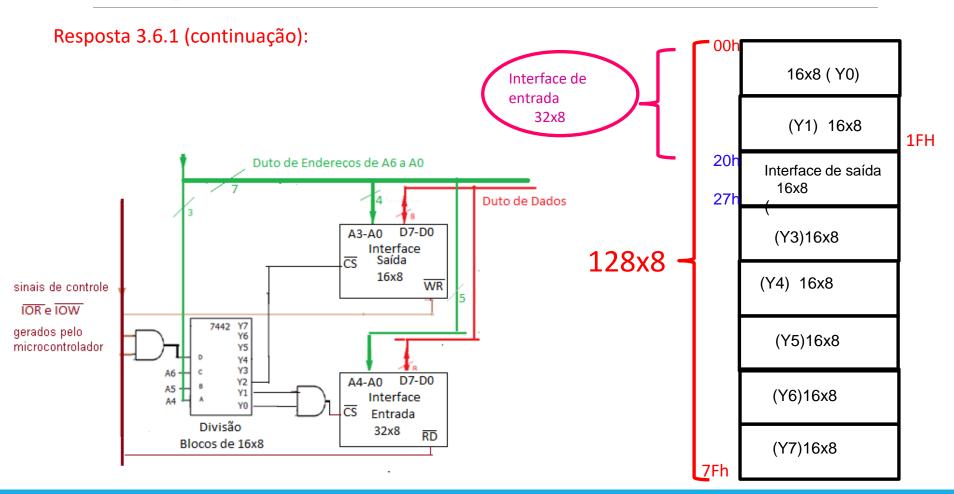

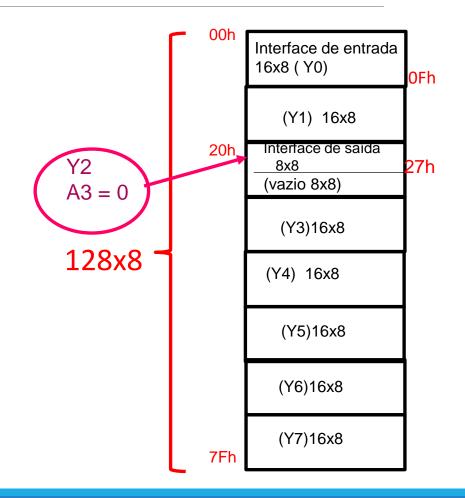

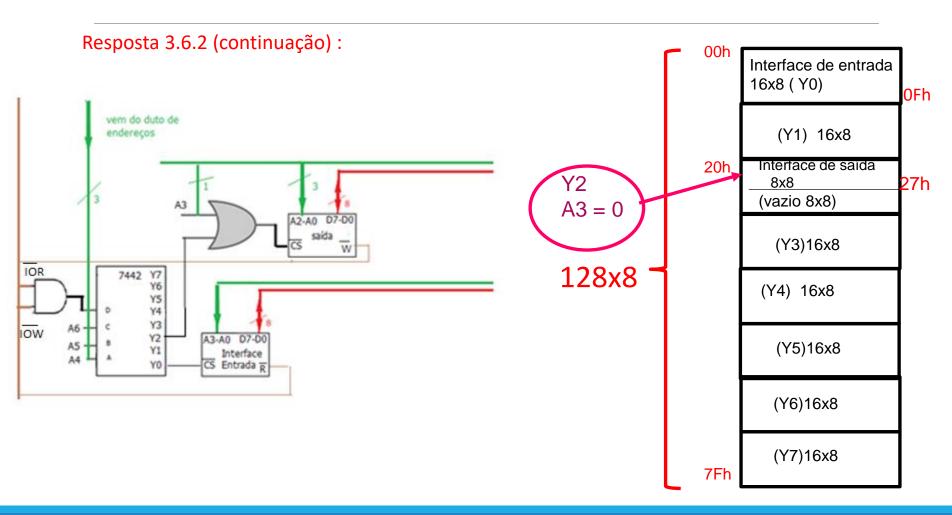

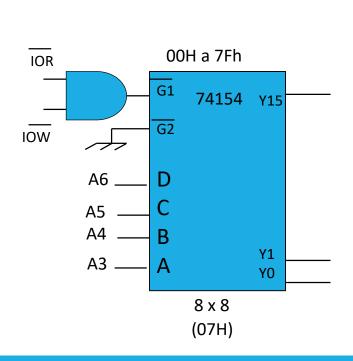

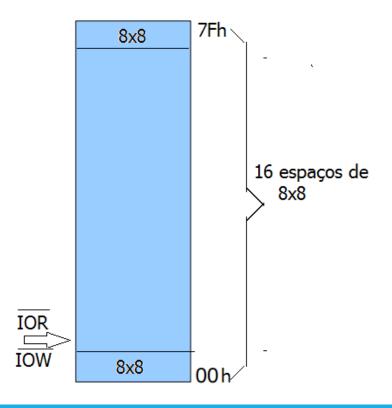

- **3.6** Esse microprocessador reserva um **espaço de 128x8** <u>para endereçar</u> dispositivos de I/O. Os sinais que o microprocessador gera para selecionar esses dispositivos é IOR (para leitura) e IOW (para escrita):

- **3.6.1** Faça a lógica de seleção **absoluta** para selecionar 1 interface cujo dispositivo de entrada tem tamanho de 32x8 e uma outra interface cujo dispositivo de saída tem tamanho 16x8

Conecte o dispositivo de entrada nos endereços mais baixos do mapeamento

A interface do dispositivo de saída deve ser conectada na faixa de endereço que contém o endereço 23h

- **3.6.2** Faça a lógica de seleção **absoluta** para selecionar uma interface cujo dispositivo de entrada tem tamanho de 16x8 e uma outra interface cujo dispositivo de saída tem tamanho 8x8.

- O dispositivo de entrada deve ser posicionado nos endereços mais baixos do mapeamento.

- E a interface do dispositivo de saída deve ser conectada na faixa de endereço que contém o endereço 23h.

#### Exercício 3 (continuação):

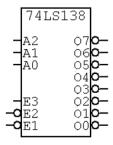

#### Informações sobre o decodificador

#### **Decodificador 74138**

Circuito Elétrico

Tabela verdade

|                |                | INP            | UTS            |                |                |                |                |                | OU.            | TPUTS          |                |                |            |

|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|------------|

| E <sub>1</sub> | E <sub>2</sub> | E <sub>3</sub> | A <sub>0</sub> | A <sub>1</sub> | A <sub>2</sub> | Ō <sub>0</sub> | Ō <sub>1</sub> | Ō <sub>2</sub> | O <sub>3</sub> | O <sub>4</sub> | O <sub>5</sub> | O <sub>6</sub> | <u>0</u> 7 |

| Н              | X              | X              | Х              | Х              | Х              | Н              | н              | н              | Н              | н              | Н              | Н              | Н          |

| X              | Н              | X              | X              | X              | X              | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н          |

| X              | X              | L              | X              | X              | X              | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н          |

| L              | L              | H              | L              | L              | L              | L              | Н              | Н              | H              | Н              | Н              | Н              | Н          |

| L              | L              | Н              | н              | L              | L              | Н              | L              | Н              | Н              | Н              | Н              | Н              | Н          |

| L              | L              | Н              | L              | Н              | L              | Н              | Н              | L              | Н              | Н              | Н              | Н              | Н          |

| L              | L              | H              | н              | Н              | L              | Н              | Н              | Н              | L              | Н              | Н              | Н              | Н          |

| L              | L              | Н              | L              | L              | Н              | Н              | Н              | Н              | Н              | L              | Н              | Н              | Н          |

| L              | L              | Н              | н              | L              | Н              | Н              | Н              | Н              | H              | Н              | L              | Н              | Н          |

| L              | L              | Н              | L              | Н              | Н              | Н              | Н              | Н              | Н              | Н              | Н              | L              | Н          |

| L              | L              | н              | н              | Н              | Н              | Н              | н              | Н              | Н              | Н              | Н              | Н              | L          |

H = HIGH Voltage Level L = LOW Voltage Level

3.1 Para implementar a lógica de seleção para dividir o **espaço de endereçamento em memória** desse microprocessador de 16bits de linhas de endereços e 8 bits de linhas de dados, em blocos de 8Kbytes, utiliza-se 3 linhas de endereços na entrada do 74138

**3. 2.** Desenhe o mapa dos endereços especificando endereço inicial e final de cada bloco de saída do 74138.

Resposta:

| Saidas   | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ENDEREÇOS |

|----------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

| do 74138 |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

|          | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0000H     |

| 00       | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1FFFH     |

| 01       | 0   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 2000H     |

|          | 0   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 3FFFH     |

| O2       | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     |

|          | 0   | 1   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 5FFFH     |

| 03       | 0   | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 6000H     |

|          | 0   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 7FFFH     |

| 04       | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 8000H     |

|          | 1   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 9FFFH     |

| O5       | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | A000H     |

|          | 1   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | BFFFH     |

| 06       | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | C000H     |

|          | 1   | 1   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | DFFFH     |

| 07       | 1   | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | E000H     |

|          | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | FFFFH     |

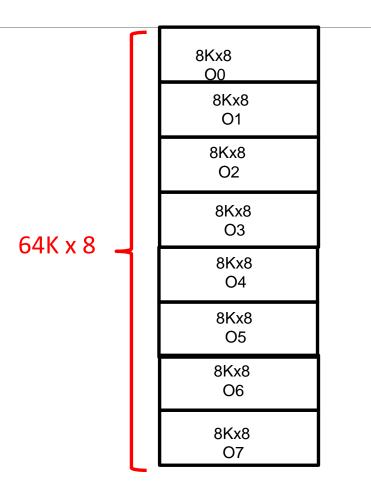

**3.2. Resposta (cont):** Desenhe o mapa dos endereços para a área das memórias especificando endereço inicial e final de cada bloco de saída do 74138.

| Saída do 74138 | Faixa de endereços |

|----------------|--------------------|

| 00             | 0000Н а 1FFFH      |

| 01             | 2000H a 3FFFH      |

| 02             | 4000H a 5FFFH      |

| О3             | 6000H a 7FFFH      |

| 04             | 8000H a 9FFFH      |

| O5             | A000H a BFFFH      |

| 06             | C000H a DFFFH      |

| 07             | E000H a FFFFH      |

com os sinais MEMR e MEMW

Espaço de mapeamento de memória de programa e memória de Dados selecionados

64K x 8

| 8Kx8<br>O0 |

|------------|

| 8Kx8<br>O1 |

| 8Kx8<br>O2 |

| 8Kx8<br>O3 |

| 8Kx8<br>O4 |

| 8Kx8<br>O5 |

| 8Kx8<br>O6 |

| 8Kx8<br>O7 |

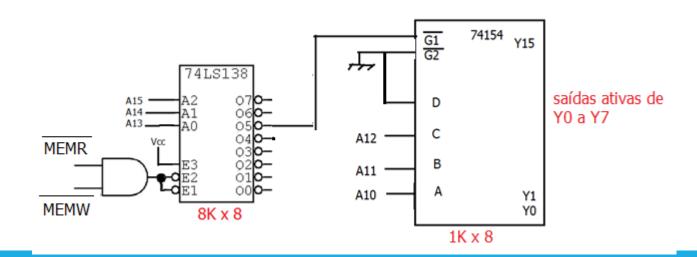

**3.3 U**tilizando decodificadores 7442 ou 74154, desenhe o projeto da lógica de seleção para o espaço de endereçamento de memórias que divide o espaço que contém o endereço A7BFH em espaços de 1Kx8 ;

| Saidas        | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 | ENDEREÇOS |

|---------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

| do 74138      |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

|               | 1   | 0   | 1   | 0   | 0   | 1   | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | A7BFH     |

| O5            |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

| $1K = 2^{10}$ |     |     |     |     |     |     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 03FFH     |

| Ao a A9       |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

**3.3. Resposta(cont):** Projeto da lógica de seleção para o espaço de endereçamento de memórias que divide o espaço que contém o endereço A7BFH em espaços de 1Kx8;

| Saidas<br>do 74138   | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 | ENDEREÇOS |

|----------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

|                      | 1   | 0   | 1   | 0   | 0   | 1   | 1  | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | A7BFH     |

| 05                   |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

| 1K = 2 <sup>10</sup> |     |     |     |     |     |     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 03FFH     |

| Ao a A9              |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

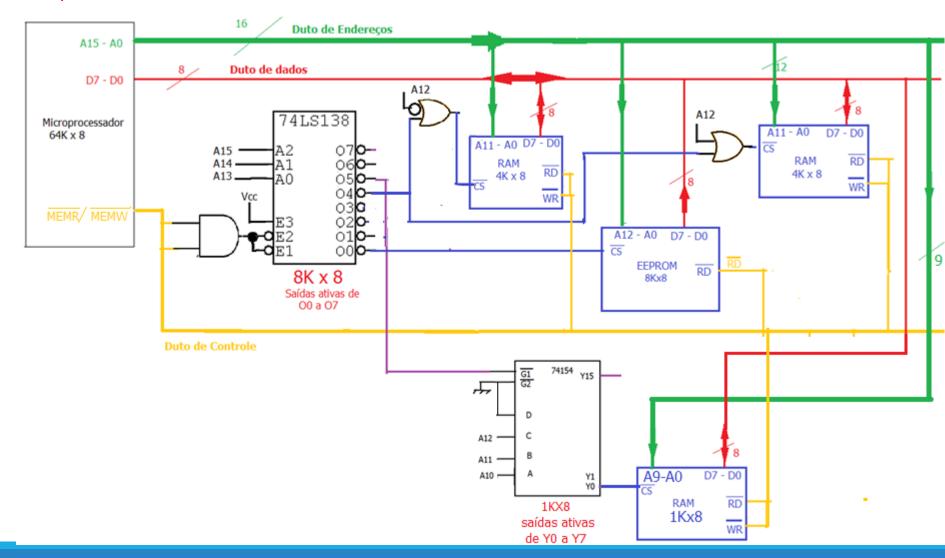

3.4.No espaço de endereçamento de memórias externa do microprocessador posicione as memórias indicando faixa de endereços que ocupam (seguindo as regras corretas) para ligar três memórias RAMs, duas de 4Kx8 e outra de 1Kx8, uma memória EEPROM de 8Kx8, de tal maneira a fazer **lógica de seleção absoluta.**

- 3.4 Resposta: A EEPROM de 8Kx8 é posicionada no endereço 0000H do espaço de mapeamento de memória, pois ao energizar o microprocessador o PC é inicializado com o valor 0000H e irá buscar neste endereço a 1ª. Instrução a ser executada. Na seleção da memória EEPROM não são gerados espaços fantasmas (lógica de seleção absoluta), pois a saída O0 do decodificador 74138 gera um espaço de endereçamento (8Kx8) que é igual ao tamanho da memória(8Kx8);

- O espaço de endereçamento que ativa a saída O4 seleciona as duas memórias RAM de 4Kx8. Como deve ser lógica de seleção absoluta, no circuito da lógica de seleção foi introduzida a linha de endereço A12 ( a qual não entra no decodificador, mas deveria constar para gerar faixas de 4Kx8). A12 é introduzida através de portas OR, para gerar espaços de 4Kx8, onde A12 = 0 seleciona a RAM de 4Kx8 e A12=1 seleciona a outra RAM de 4Kx8.

- No espaço que ativa a saída O5 é ligado um decodificador para gerar espaços de 1Kx8, desta forma a RAM de 1Kx8 foi ligada à saída Y0 do decodificador 74154 para que as memórias RAMs sejam ligadas em sequência e não exista espaço vazios entre elas, e também não sejam gerados espaços fantasmas, pois é lógica de

seleção absoluta

|                     |     |     |     |     |     | ,   | U  |    |    | •  | -  |    |    |    | •  |    | O         |

|---------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

| Saidas<br>do 74138  | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ENDEREÇOS |

|                     | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 8000H     |

| O4<br>(A12= 0)      | 1   | 0   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 8FFFH     |

| RAM<br>4Kx8         |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

| O4<br>(A12 = 1)     | 1   | 0   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 9000H     |

| RAM<br>4Kx8         | 1   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 9FFFH     |

| Bloco de<br>1Kx x 8 |     |     |     |     |     |     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 03FFH     |

|                     |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |

Resolução Exercício 3:

3.4.RESP: No espaço de endereçamento de memórias externa do microprocessador ligar EEPROM nas primeiras posições da memória porque o microprocessador ao ser ressetado o PC é inicializado com a posição 0000h. As duas RAMs de 4Kx8 são ligadas à saída O4 e a RAM de

1KvQ na saída O5 nara manter as RAMs em enderecos seguenciais

| Saidas      | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Endereços | Dispositivo |   | EEPROM                |

|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|-------------|---|-----------------------|

| lo 74138    |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |             |   | 8Kx8 ( 00)            |

|             | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0000H     | EEPROM      |   |                       |

| 00          | 0   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1FFFH     | 8K x8       |   |                       |

| 01          | 0   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 2000H     | Vazio       |   | O1 (vazio)            |

|             | 0   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 3FFFH     | 8K x 8      |   | 0 / (10.2.0)          |

| O2          | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     | Vazio       |   | 00 ( )                |

|             | 0   | 1   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 5FFFH     | 8K x 8      |   | O2 (vazio)            |

| О3          | 0   | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 6000H     | Vazio       |   |                       |

|             | 0   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 7FFFH     | 8K x 8      |   |                       |

| O4 (A12 =0) | 1   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 8000H     | RAM         |   | O3 (vazio)            |

|             | 1   | 0   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 8FFFH     | 4K x 8      |   |                       |

|             |     |     |     |     |     |     |    |    |    |    |    |    |    |    |    |    |           |             |   | RAM 4Kx8( 04, A12 =0) |

| O4(A12=1)   | 1   | 0   | 0   | 1   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 9000H     | RAM         |   |                       |

|             | 1   | 0   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 9FFFH     | 4K x 8      |   | RAM 4Kx8(04, A12 =1)  |

| O5          | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | A000H     | Decoder     |   | ♠ RAM 1Kx8( 04, A12 = |

|             | 1   | 0   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | BFFFH     | 74154       |   | O5(74154)             |

| O5          | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | A000H     | RAM         |   | 00(/ 1101)            |

| Y0 do 74154 | 1   | 0   | 1   | 0   | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | A3FFH     | 1Kx8        |   |                       |

| 06          | 1   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | C000H     | azio        |   | O6(vazio)             |

|             | 1   | 1   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | DFFFH     | 8K x 8      | / | 5 5 (1 5)             |

| 07          | 1   | 1   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | E000H     | azio        |   | O7(vazio)             |

| -           | 1   | 1   | 1   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | FFFFH     | 8K x 8      |   | 8Kx8                  |

O5 é dividido em 8 espaços de 1K x 8 pelo decodificador 74154:

Na saída Y0 é conectada a RAM de 1Kx8

3.5 circuito lógica de **seleção Absoluta** para o espaço de mapeamento em memória do item 3.4. Resposta:

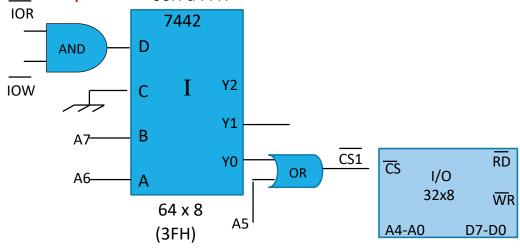

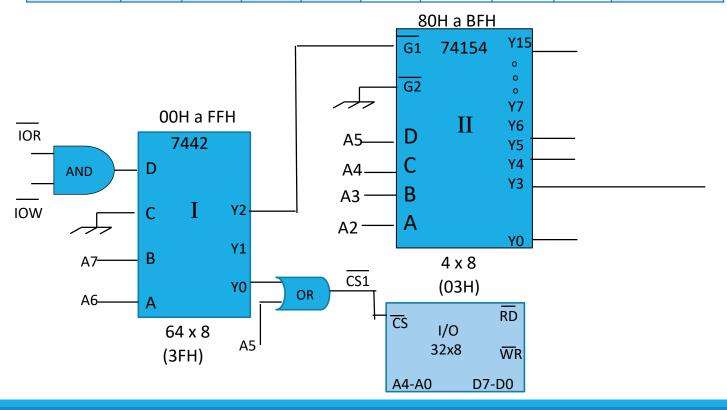

**3.6.1** Para o espaço de 128x8, Faça a lógica de seleção **absoluta** para selecionar 1 interface cujo dispositivo de entrada tem tamanho de 32x8 e uma outra interface cujo dispositivo de saída tem tamanho 16x8 (sinais de controle: IOR e IOW

#### **RESPOSTA:**

A capacidade de endereçamento para dispositivo de I/O é de 128x8, que é 2<sup>7</sup> x 8, ou seja, tem 7 bits de endereços de A0 a A6, e varia do endereço 00h a 7Fh Utilizando o decodificador 7442 pode-se dividir o espaço total em 8 espaços de 16x8

|                         | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ENDEREÇOS |

|-------------------------|----|----|----|----|----|----|----|-----------|

| Espaço de endereçamento | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00H       |

| de I/O                  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 7FH       |

#### Resposta 3.6.1 (continuação):

| Saidas<br>do 7442                            | A6 | A5 | A4 | А3 | A2 | A1 | A0 | ENDEREÇOS |

|----------------------------------------------|----|----|----|----|----|----|----|-----------|

| VO - V4                                      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00h       |

| Y0 e Y1<br>Interface<br>de entrada<br>(32x8) | 0  | 0  | 1  | 1  | 1  | 1  | 1  | 1Fh       |

|                                              | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 23h       |

| Y2<br>Interface                              | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 20H       |

| de saída<br>(8x8)                            | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 27hH      |

#### 3.6.1 Circuito Completo:

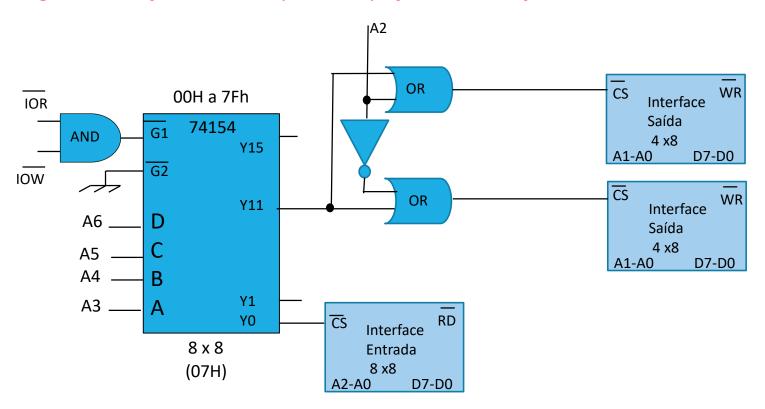

**3.6.2** Faça a lógica de seleção **absoluta** para selecionar uma interface cujo dispositivo de entrada tem tamanho de 16x8 e uma outra interface cujo dispositivo de saída tem tamanho 8x8.

O dispositivo de entrada deve ser posicionado nos endereços mais baixos do mapeamento.

E a interface do dispositivo de saída deve ser conectada na faixa de endereço que contém o

128x8

endereço 23h.

#### **RESPOSTA:**

A capacidade de endereçamento para dispositivo de I/O é de 128x8, tem 7 bits de endereços de A0 a A6, e varia do endereço 00h a 7Fh

Utilizando o decodificador 7442 pode-se dividir o espaço total em 8 espaços de 16x8

|                          | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ENDEREÇOS |

|--------------------------|----|----|----|----|----|----|----|-----------|

| Espaço de                | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00H       |

| endereçame<br>nto de I/O | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 7FH       |

| O   | o que contém o |  |  |  |  |  |  |  |  |

|-----|----------------|--|--|--|--|--|--|--|--|

| h   | (Y0)16x8       |  |  |  |  |  |  |  |  |

|     | (Y1) 16x8      |  |  |  |  |  |  |  |  |

|     | (Y2) 16x8      |  |  |  |  |  |  |  |  |

|     | (Y3)16x8       |  |  |  |  |  |  |  |  |

|     | (Y4)16x8       |  |  |  |  |  |  |  |  |

|     | (Y5)16x8       |  |  |  |  |  |  |  |  |

|     | (Y6)16x8       |  |  |  |  |  |  |  |  |

|     | (Y7)16x8       |  |  |  |  |  |  |  |  |

| n ' |                |  |  |  |  |  |  |  |  |

#### Resposta 3.6.2:

| Saidas<br>do 7442                       | A6 | A5 | A4 | A3 | A2 | A1 | A0 | ENDEREÇOS |

|-----------------------------------------|----|----|----|----|----|----|----|-----------|

| \ <u>\</u>                              | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00h       |

| Y0<br>Interface<br>de entrada<br>(16x8) | 0  | 0  | 0  | 1  | 1  | 1  | 1  | OFh       |

|                                         | 0  | 1  | 0  | 0  | 0  | 1  | 1  | 23h       |

| Y2<br>Interface                         | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 20H       |

| de saída<br>(8x8)                       | 0  | 1  | 0  | 0  | 1  | 1  | 1  | 27hH      |

3.6.2 Circuito Completo:

#### Exercício 4:

Considerando um microprocessador de 17 bits de linhas de endereço e 8 bits de linhas de dados para mapeamento em memória e espaço de 128 bytes para mapeamento de dispositivos de I/O:

- 4.1. Indique o endereço inicial e final do espaço <u>de mapeamento</u> apenas para memória, sabendo que os sinais de controle para esse mapeamento <u>é</u> MEMR e MEMW

- 4.2 Faça o projeto da lógica de seleção para dividir o espaço de endereçamento do item 4.1 em blocos de 8Kbytes. Para tal, utilize os decodificadores 74154, 7442 ou 74138

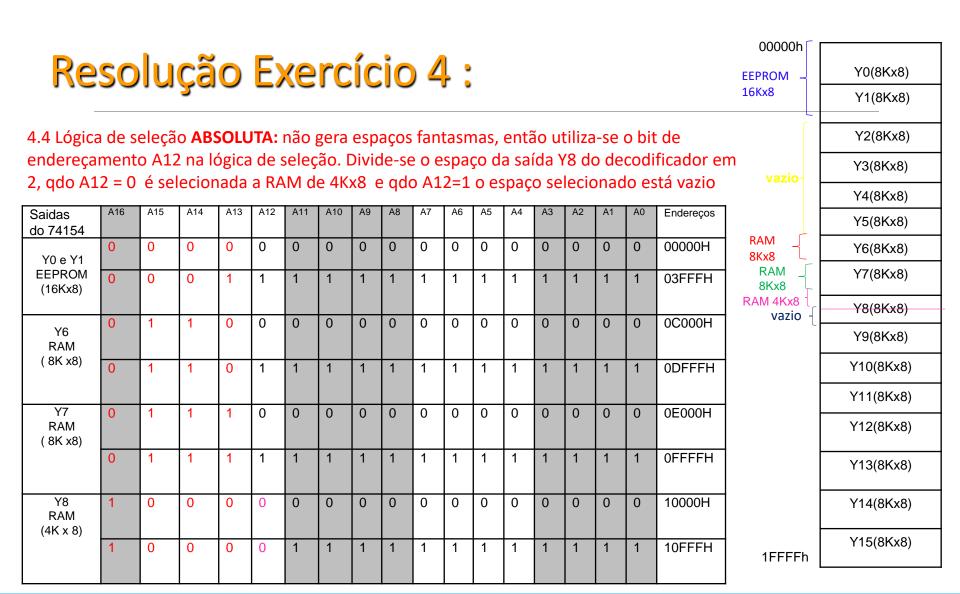

- 4.3 Complete a lógica de Seleção do item 4.1 com lógica de seleção NÁO absoluta ligando uma EEPROM de 16Kx8, outra EEPROM de 8Kx8 e 2 RAMs de 8Kx8 e outra RAM de 4Kx8. Apresente o mapa de endereços com as memórias posicionadas e a faixa de endereços que as selecionam.

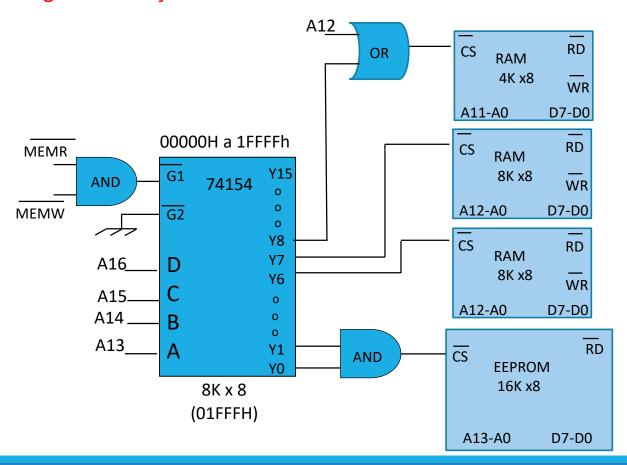

- 4.4 Faça a lógica de seleção Absoluta para o mesmo espaço de endereçamento do item 4.1 e para as mesmas memórias do item 4.3

- 4.5 Esse microprocessador apresenta um espaço de mapeamento de I/O isolado de 128bytes, o qual é selecionado pelos controles IOR ( para leitura) e IOW (para escrita). Apresente os circuitos para lógica de seleção de seleção Absoluta e para Lógica de seleção NÃO Absoluta para este espaço, que selecione uma interface de entrada de tamanho 8x8 que contém a posição 03h e 2 interfaces de saída de tamanho 4x8 cujo endereço 5Ah faz parte da seleção de uma dessas interfaces.

Indique as faixas dos dispositivos e faixas fantasma se houverem.

- 4.1 Capacidade de endereçamento do microprocessador:  $2^{17} \times 8 = 128 \times 8$  Endereço Inicial: 00000H e Endereço final: 1FFFFH

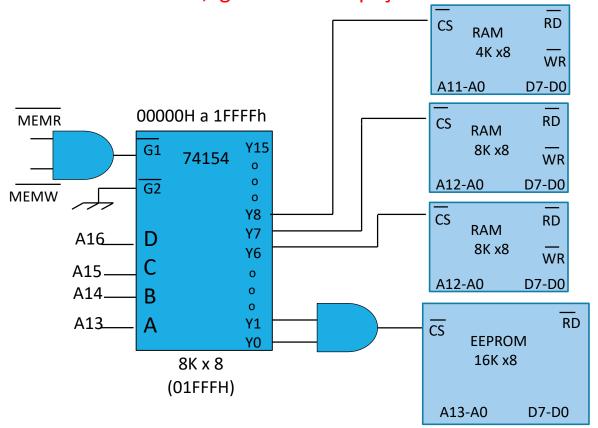

- 4. 2 Divisão do espaço de endereçamento em blocos de 8Kx8 Circuito da Lógica de Seleção

1FFFFh

00000h

Y0(8Kx8) Y1(8Kx8) Y2(8Kx8) Y3(8Kx8) Y4(8Kx8) Y5(8Kx8) Y6(8Kx8) Y7(8Kx8) Y8(8Kx8) Y9(8Kx8) Y10(8Kx8) Y11(8Kx8) Y12(8Kx8) Y13(8Kx8) Y14(8Kx8) Y15(8Kx8)

| Saidas             | A16  | A15  | A14 | A13  | A12 | A11  | A10  | A9  | A8  | A7  | A6  | A5  | A4    | A3  | A2  | A1 | A0  | Endereços  | TEEPROM -    | Y0(8Kx8)                               |

|--------------------|------|------|-----|------|-----|------|------|-----|-----|-----|-----|-----|-------|-----|-----|----|-----|------------|--------------|----------------------------------------|

| do 74154           | 7110 | 7110 | /   | 7110 | /   | 7111 | 7110 | 7.0 | 7.0 | 7.0 | 7.0 | 7.0 | , , , | 710 | 712 |    | 7.0 | Lildereços | 16Kx8        | Y1(8Kx8)                               |

| Y0 e Y1            | 0    | 0    | 0   | 0    | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0  | 0   | 00000H     |              | \\0\(\0\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |

| EEPROM             | 0    | 0    | 0   | 1    | 1   | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1  | 1   | 03FFFH     | †   <u> </u> | Y2(8Kx8)                               |

| (16Kx8)            |      |      |     |      |     |      |      |     |     |     |     |     |       |     |     |    |     |            | vazio-       | Y3(8Kx8)                               |

| Y6                 | 0    | 1    | 1   | 0    | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0  | 0   | 0C000H     |              | Y4(8Kx8)                               |

| RAM<br>( 8K x8)    |      |      |     |      |     |      |      |     |     |     |     |     |       |     |     |    |     |            |              | Y5(8Kx8)                               |

| ( or xo)           | 0    | 1    | 1   | 0    | 1   | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1  | 1   | 0DFFFH     | RAM<br>8Kx8  | Y6(8Kx8)                               |

| Y7                 | 0    |      | 1   | 1    |     | 0    | 0    |     |     |     |     |     |       |     |     |    |     | 0E000H     | RAM _        | Y7(8Kx8)                               |

| RAM<br>( 8K x8)    | 0    | 1    | 1   |      | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0  | 0   | DEUUUH     | 8Kx8 RAM     | Y8(8Kx8)                               |

| ( 01( 10)          | 0    | 1    | 1   | 1    | 1   | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1  | 1   | 0FFFFH     | 4Kx8 L       | Y9(8Kx8)                               |

|                    |      |      |     |      |     |      |      |     |     |     |     |     |       |     |     |    |     |            |              | . ,                                    |

| Y8<br>RAM          | 1    | 0    | 0   | 0    | 0   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0  | 0   | 10000H     | ]            | Y10(8Kx8)                              |

| (4K x 8)           |      |      |     |      |     |      |      |     |     |     |     |     |       |     |     |    |     |            |              | Y11(8Kx8)                              |

|                    | 1    | 0    | 0   | 0    | 1   | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1  | 1   | 11FFFH     |              | Y12(8Kx8)                              |

| 4Kx8               |      |      |     |      |     | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   | 1   | 1  | 1   | 00FFFh     |              | Y13(8Kx8)                              |

|                    |      |      |     |      |     |      |      |     |     |     |     |     |       |     |     |    |     | 440001     |              | Y14(8Kx8)                              |

| Espaço<br>fantasma | 1    | 0    | 0   | 0    | 1   | 0    | 0    | 0   | 0   | 0   | 0   | 0   | 0     | 0   | 0   | 0  | 0   | 11000h     | -            |                                        |

| da RAM<br>(4Kx8)   | 1    | 0    | 0   | 0    | 1   | 1    | 1    | 1   | 1   | 1   | 1   | 1   | 1     | 1   |     | 1  | 1   | 11FFFH     | l<br>1FFFFh  | Y15(8Kx8)                              |

4.3 Circuito da Lógica de seleção NÃO ABSOLUTA para o espaço de mapeamento de memória de 128 K x8

Resposta: Pode ser gerada espaços fantasmas na última RAM ( de 4Kx8) e o programador do software vai saber que existe memória RAM DE 20kx8 que ocupa a posição de 0C000H a 10FFFH, ignorando o espaço fantasma

4.4 Circuito da Lógica de seleção ABSOLUTA

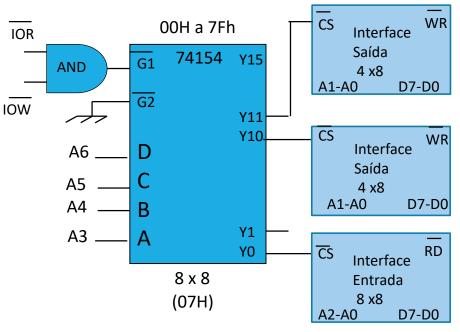

4.5 Espaço para mapeamento de I/O é de 128 bytes, portanto apresenta 7 linhas de endereços de A6 a A0. Utilizando o decodificador 74154 o espaço de 128x8 é dividido em espaços de 8x8.

4.5 Liga-se a interface de entrada de tamanho 8x8 na saída Y0 que contém o endereço 03H e 2 interfaces de saída de tamanho 4x8 onde uma delas é ligada à saída Y11 que contém o endereço 5AH

| Saidas<br>do 74154      | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Endereços |

|-------------------------|----|----|----|----|----|----|----|-----------|

| Bloco de saída<br>(8x8) | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 7FH       |

| Interface entrada<br>Y0 | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 03h       |

| YO                      | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 00H       |

|                         | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 08H       |

| Interface Saída<br>Y11  | 1  | 0  | 1  | 1  | 0  | 1  | 0  | 5Ah       |

| Y11                     | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 58H       |

| ( 8 x8)                 | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 5FH       |

| Interface<br>Saida 1    | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 58H       |

| A3 = 0                  | 1  | 0  | 1  | 1  | 0  | 1  | 1  | 5BH       |

| Interface<br>Saida 1    | 1  | 0  | 1  | 1  | 1  | 0  | 0  | 5CH       |

| A3 = 1                  | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 5FH       |

4.5 Lógica se seleção **Absoluta** para o espaço de endereçamento de I/O de 128 x 8.

#### 4.5 lógica se seleção Não Absoluta para o espaço de endereçamento de I/O de 128x8.

|                                  | 1 4 0 | Τ  | 1 4 4 | 1 40 | 1 40 | <b>1 A 4</b> | 1.0 | ι         |

|----------------------------------|-------|----|-------|------|------|--------------|-----|-----------|

| Saidas<br>do 74154               | A6    | A5 | A4    | A3   | A2   | A1           | A0  | Endereços |

| Interface entrada                | 0     | 0  | 0     | 0    | 0    | 0            | 0   | 00H       |

| Y0<br>8x8                        | 0     | 0  | 0     | 0    | 1    | 1            | 1   | 08H       |

| Interface<br>Saída 1             | 1     | 0  | 1     | 1    | 0    | 0            | 0   | 58H       |

| Y11                              | 1     | 0  | 1     | 1    | 1    | 1            | 1   | 5BH       |

| Fantasma                         | 1     | 0  | 1     | 1    | 1    | 0            | 0   | 5CH       |

| Interface<br>Saida 1             | 1     | 0  | 1     | 1    | 1    | 1            | 1   | 5FH       |

| Interface<br>Saida 2             | 1     | 0  | 1     | 0    | 0    | 0            | 0   | 50H       |

| Y10                              | 1     | 0  | 1     | 0    | 1    | 1            | 1   | 57H       |

| Fantasma<br>Interface<br>Saida 2 | 1     | 0  | 1     | 0    | 1    | 0            | 0   | 54H       |

| 24.44                            | 1     | 0  | 1     | 0    | 1    | 1            | 1   | 57H       |

#### Exercício 5:

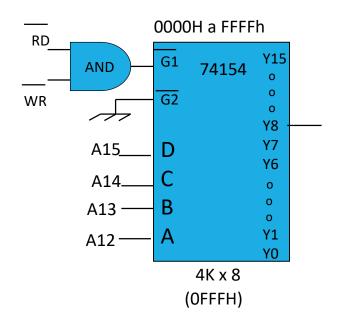

- **5.1.** Um microprocessador reserva um <u>espaço</u> de 64Kx8 para endereçamento de memórias e I/Os. Esse espaço é selecionado pelos sinais RD e WR.

- Faça o projeto da lógica de seleção para dividir esse espaço de endereçamento em espaços de 4Kbytes, especificando endereço inicial e final de cada bloco.

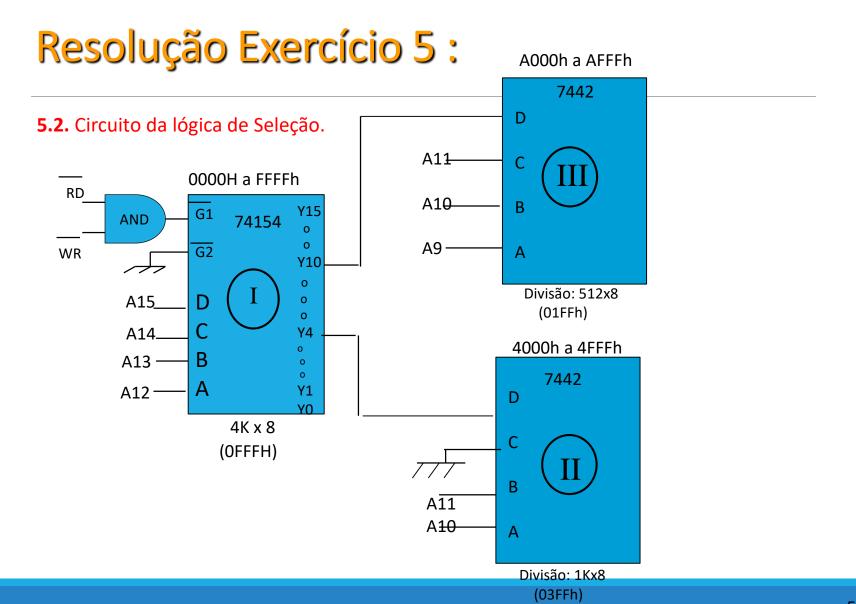

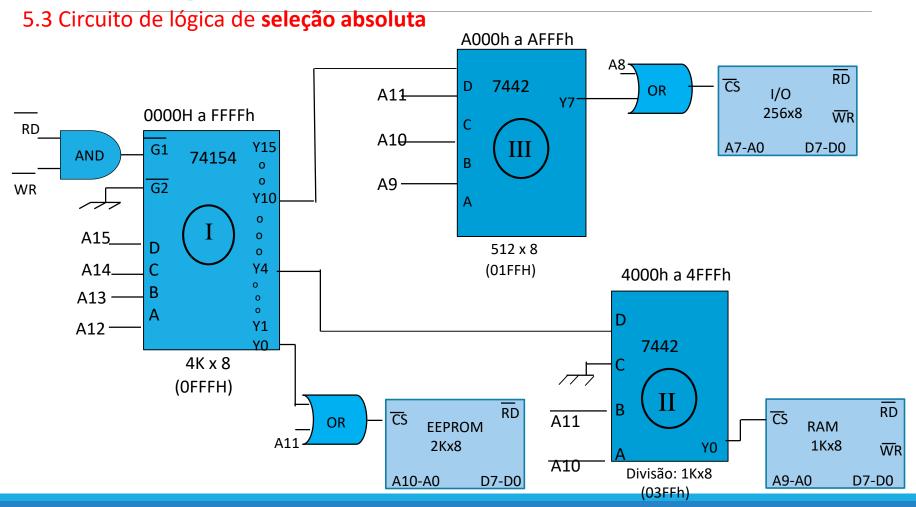

- 5.2 Divida o bloco que inicia no endereço 4000H, em blocos de 1Kbytes e o bloco que inicia no endereço A000H em blocos de 512 bytes.

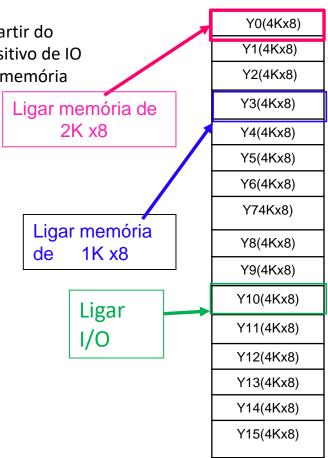

- 5.3 Usando lógica de **seleção absoluta** ligue uma memória de 2kbytes, a partir do endereço 0000H, outra de 1Kbyte a partir do endereço 4000H, e um dispositivo de IO de 256x8 a partir do endereço AE03H. Determine o endereço final de cada memória e do dispositivo ligado.

- 5.4 Implemente a lógica de seleção **NÃO absoluta** para os mesmos dispositivos e memórias como solicitado no item 5.3

- 5.5 Encontre a faixa de endereços que seleciona cada memória e dispositivo de I/O indicando a faixa de endereços fantasmas quando houverem e calculando o número de faixas fantasmas geradas por cada um deles

**5.1.** Dividir 64K/4K = 16, portanto, é necessário dividir o espaço em 16 partes de 4Kx8. então utiliza-se um

decodificador de 4x16, o 74154 com 4 entradas, cujas faixas de saídas estão mostradas abaixo

| Saída do 74154 | Faixa do endereços |

|----------------|--------------------|

| YO             | 0000H a 0FFFH      |

| Y1             | 1000H a 1FFFH      |

| Y2             | 2000H a 2FFFH      |

| Y3             | 3000H a 3FFFH      |

| Y4             | 4000H a 4FFFH      |

| Y5             | 5000H a 5FFFH      |

| Y6             | 6000H a63FFFH      |

| Y7             | 7000H a 7FFFH      |

| Y8             | 8000H a 8FFFH      |

| Y9             | 9000H a 9FFFH      |

| Y10            | A000H a AFFFH      |

| Y11            | B000H a BFFFH      |

| Y12            | C000H a CFFFH      |

| Y13            | D000H a DFFFH      |

| Y14            | E000H a EFFFH      |

| Y15            | F000H a FFFFH      |

|                |                    |

Espaço de endereçamento em memória do microprocessador 64Kx8

| Y0(4Kx8)  |

|-----------|

| Y1(4Kx8)  |

| Y2(4Kx8)  |

| Y3(4Kx8)  |

| Y4(4Kx8)  |

| Y5(4Kx8)  |

| Y6(4Kx8)  |

| Y74Kx8)   |

| Y8(4Kx8)  |

| Y9(4Kx8)  |

| Y10(4Kx8) |

| Y11(4Kx8) |

| Y12(4Kx8) |

| Y13(4Kx8) |

| Y14(4Kx8) |

| Y15(4Kx8) |

|           |

5.1. Decodificador para dividir o espaço de 64K x 8 para mapeamento de memórias e dispositivos de I/O em blocos de 4K x8

| Y0(4Kx8)  |

|-----------|

| Y1(4Kx8)  |

| Y2(4Kx8)  |

| Y3(4Kx8)  |

| Y4(4Kx8)  |

| Y5(4Kx8)  |

| Y6(4Kx8)  |

| Y74Kx8)   |

| Y8(4Kx8)  |

| Y9(4Kx8)  |

| Y10(4Kx8) |

| Y11(4Kx8) |

| Y12(4Kx8) |

| Y13(4Kx8) |

| Y14(4Kx8) |

| Y15(4Kx8) |

5.2 Dividir o bloco que inicia no endereço 4000H, em blocos de 1Kbytes e o bloco que inicia no endereço A000H em blocos de 512 bytes.

O bloco que e inicia no endereço 4000H pertence à saída Y4 do decodificador 74154 e deve ser dividido em espaços de 1Kx8, portanto em 4 . Para isto, necessita-se de um decodificador com 2 entradas de endereços (A11 e A10).

O bloco que inicia no endereço A000h é o bloco da saída Y10 do decodificador

Para dividi-lo em espaços de 512 bytes deve-se ligar à esta saída um decodificador com 3 entradas, obtendo assim 3 espaços. De tal maneira, que 4Kx8 dividido por 8 gera espaços de 512x8

| Saidas<br>do 74154 | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | А3 | A2 | A1 | A0 | Endereços |

|--------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

|                    | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     |

| Y4                 | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     |

| 14                 | 0   | 1   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 4FFFH     |

|                    | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | A000H     |

| Y10                | 1   | 0   | 1   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 01 | A000H     |

|                    | 1   | 1   | 0   | 1   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | DFFFH     |

**5.3** Usando lógica de **seleção absoluta** ligue uma memória de 2kbytes, a partir do endereço 0000H, outra de 1Kbyte a partir do endereço 4000H, e um dispositivo de IO de 256x8 a partir do endereço AE03H. Determine o endereço final de cada memória e do dispositivo ligado.

Resp: Na lógica de seleção absoluta não podem existir espaços fantasmas (espelhos), o tamanho do espaço selecionado pelos decodificadores, através do endereço enviado pelo microprocessador, deve ser do mesmo tamanho do dispositivo ou memória acessados.

E, mapeamento em memória o microprocessador endereça no mesmo espaço de endereçamento memórias e dispositivos de I/O.

No caso do microprocessador deste exercício o espaço é de 64K x 8

5.3 A memória de 2Kbytes deve ser ligada a partir do endereço 0000h, ou seja, na saída Y0 do decodificador I, Mas, a memória de 2Kbytes tem linhas de enderços de A10-A0, portanto, a linha de endereço A11 não está na entrada do decodificador, mas como é lógica de seleção absoluta a linha de endereço A11 deve entrar na seleção. Desta forma, inclui-se ela A11=0 com uma porta OR .

A memória de 1Kx8 deve ser ligada ao endereço 4000h, , ou seja, saída Yo do decodificador II que é selecionado pela saída Y4 do decodificador. O decodificador II seleciona blocos de 1Kx8.

que é a saída Y4 do decodificador I que seleciona o decodificador II tem endereços de A10 a A7, portanto deve ser ligada ao endereço 4000h, ou seja, saída Yo do decodificador II que é selecionado pela saída Y4 do decodificador I . O dispositivo de I/O de 256x8 (A7-A0) deve ser ligado à saída Y7 do decoder III e deve ser inserida na seleção a linha de endereço A8 que não entra no decodificador III

| Saidas<br>do 74154            | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Endereços |

|-------------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

| MEM<br>2Kx8                   | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0000H     |

| Y0 de I                       | 0   | 0   | 0   | 0   | 0   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 07FFH     |

| MEM<br>1Kx8                   | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     |

| Yo de II                      | 0   | 1   | 0   | 0   | 0   | 0   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 43FFH     |

| Saida Y10 de I<br>e Y7 de III | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | AE03h     |

| I/O                           | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AE00h     |

| De<br>256x8                   | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | AEFFh     |

5.3 Circuito de lógica de seleção NÃO absoluta A000h a AFFFh 7442 RD A11-<del>C</del>S **Y7** 1/0 0000H a FFFFh 256x8 RD  $\overline{W}R$ A10-G1 **Y15 AND** 74154 A7-A0 D7-D0 В A9 G2 WR Y10 0 A15\_ 0 D 512 x 8 0 A14. **Y4** (01FFH) 4000h a 4FFFh В A13 Y1 A12 Y0 7442 4K x 8 (OFFFH) RD <del>C</del>S RD **EEPROM** A11 RAM 2Kx8 1Kx8 Y0 WR A10 A10-A0 D7-D0 Divisão: 1Kx8 A9-A0 D7-D0 (03FFh)

#### 5..5 Usando lógica de seleção NÃO absoluta, faixas das memórias e dispositivos

| Saidas<br>do 74154               | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A1 | A0 | Endereços |

|----------------------------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|----|----|----|----|----|-----------|

| 2Kx8                             |     |     |     |     |     | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 07FFh     |

| Faixa MEM<br>2Kx8                | 0   | 0   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0000H     |

| Y0 de I                          | 0   | 0   | 0   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 0FFFH     |

| 1Kx8                             |     |     |     |     |     |     | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 03FFh     |

| Faixa MEM<br>1Kx8<br>Yo de II    | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 4000H     |

| 10 00 11                         | 0   | 1   | 0   | 0   | 0   | 0   | 0  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 41FFH     |

| Saida Y10<br>de I e Y7<br>de III | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | AE03h     |

| 256x8                            |     |     |     |     |     |     |    |    | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 00FFh     |

| I/O<br>De                        | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | AE00h     |

| 256x8                            | 1   | 0   | 1   | 0   | 1   | 1   | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | AFFFh     |

# **5.5 F**aixas das memórias e dispositivo, faixas fantasmas e quantidade de faixas fantasmas

| Dispositivo     | Faixa de<br>seleção | Tamanho<br>do<br>dispositiv<br>o | Faixa que<br>dispositivo pode<br>ocupar | Faixa fantasma | Quanti//de blocos<br>fantasmas gerados |

|-----------------|---------------------|----------------------------------|-----------------------------------------|----------------|----------------------------------------|

| Mem 2Kx8        | 0000h a 0FFFh       | 07FFH                            | 0000Н а 07FFH                           | 0800h a 0FFFh  | 1                                      |

| Mem de 1Kx8     | 4000h a 43FFh       | 03FFH                            | 4000h a 43FFh                           | Não existe     | 0                                      |

| Dispositivo I/O | AE00h AFFFh         | 00FFH                            | AE00H a AEFFH                           | AF00h a AFFFh  | 1                                      |

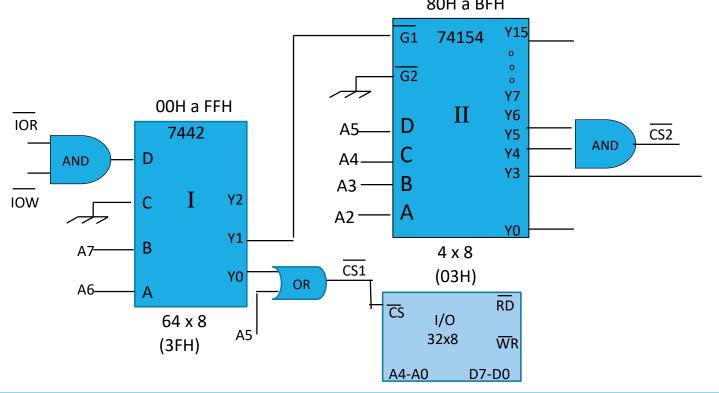

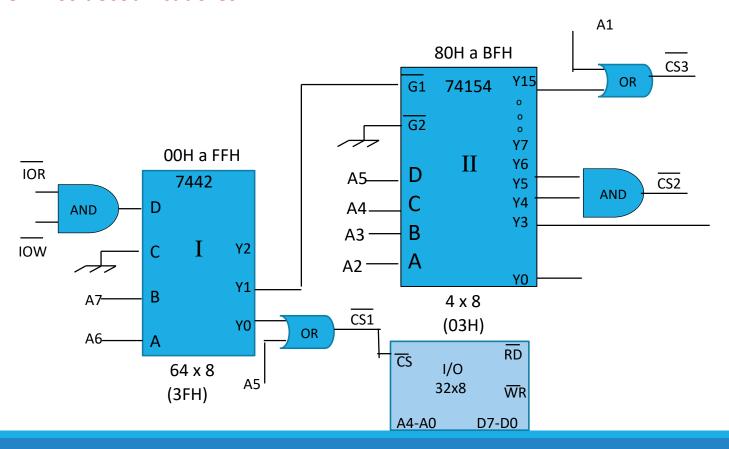

#### Exercício 6:

6. Faça a lógica de seleção **Absoluta** com mapeamento em I/O isolado considerando que um microprocessador tem a capacidade de endereçar um espaço de 256x8 para dispositivos de I/O.

Os sinais de controle que acessam essa região são IOR e IOW, respectivamente, para leitura e escrita em dispositivos de I/O.

- ✓ Utilizando o decodificador 7442(4X10), decodificador I, divida o espaço de endereçamento em espaços de 64 x 8 e ligue um dispositivo de I/O de tamanho 32 x8 na saída /CS1 que contém o endereço 00H;

- ✓ Utilizando o decodificador 74154(4X16), decodificador II, divida a saída que contém o endereço 8DH em faixas de tamanho 4 x 8.

- ✓ Com as saídas do decodificador II, gere uma saída /CS2 que possibilite a ligação de dispositivos de 8 x 8 que contenha os endereços 92H e 95H.

- ✓ Utilizando a saída Y7 do decodificador II gere uma saída /CS3 que possibilite ligar dispositivos de 2 x 8

- ✓ Utilizando um decodificador III, crie uma saída /CS4 que selecione dispositivos de 1x8 no endereço 8EH

|            | А7 | А6 | A5 | A4 | А3 | A2 | A1 | A0 | Faixa da<br>saída | Tamanho<br>do bloco | Faixa das saídas em<br>hexadecimal |

|------------|----|----|----|----|----|----|----|----|-------------------|---------------------|------------------------------------|

|            |    |    | 1  | 1  | 1  | 1  | 1  | 1  | 3FH               | 64 x8               |                                    |

| Decoder I  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |                   |                     | 00H a FFH                          |

|            | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  |                   |                     |                                    |

| /CS1       | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 1FH               | 32 x 8              | 00H a 1FH                          |

|            | 0  | 0  | 0  | 1  | 1  | 1  | 1  | 1  |                   |                     |                                    |

| Decoder II | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  | 92H               |                     | Saída Y4 do Decoder II             |

| /CS2       | 1  | 0  | 0  | 1  | 0  | 1  | 0  | 1  | 95H               |                     | Saída Y5 do Decoder II             |

| /CS3       | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 0  | 9CH               | 2x8                 | 9CH a 9DH                          |

|            | 1  | 0  | 0  | 1  | 1  | 1  | 0  | 1  | 9DH               |                     |                                    |

| /CS4       | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 8EH               | 1x8                 | Saída Y2 do decoder III            |

✓ Utilizando o decodificador 7442(4X10), decodificador I, divida o espaço de endereçamento em espaços de 64 x 8 e ligue um dispositivo de I/O de tamanho 32 x8 na saída /CS1 que contém o endereço 00H;

Resposta: 256/64 = 4, portanto ligar 2 entradas no decodificador, e como é lógica de seleção absoluta o dispositivo de 32x8 deve ser ligado à saída Y0 com uma porta OR acrescentando o bit A5 que não consta nem na entrada do decodificador nem no endereçamento do dispositivo<sub>00H a FFH</sub>

Resolução Exercício 6 : ✓ Utilizando o decodificador 74154(4X16), decodificador II, divida a saída que contém o endereço 8DH em faixas de tamanho 4 x 8.

|          | A7 | A6 | A5 | A4 | А3 | A2 | A1 | Α0 | Faixa da saída |

|----------|----|----|----|----|----|----|----|----|----------------|

| Saída Y1 | 1  | 0  | 0  | 0  | 1  | 1  | 0  | 1  | 8DH            |

✓ Com as saídas do decodificador II, gere uma saída /CS2 que possibilite a ligação de dispositivos de 8 x 8 que contenha os endereços 92H e 95H.

Resposta : saídas Y4 e Y5 do decoder II ligadas por porta AND

|                   | A7 | A6 | A5 | A4 | А3 | A2 | A1            | Α0 | Faixa da saída |

|-------------------|----|----|----|----|----|----|---------------|----|----------------|

| Saída Y4<br>De II | 1  | 0  | 0  | 1  | 0  | 0  | 1             | 0  | 92H            |

| Saída Y5 de<br>II | 1  | 0  | 0  | 1  | 0  | 1  | 0<br>20H a BI | 1  | 95H            |

✓ Utilizando a saída Y7 do decodificador II gere uma saída /CS3 que possibilite ligar dispositivos de 2 x 8.

Resposta: incluir a entrada A1 que não está no endereçamento de organizações de 2x8 e nem nos decodificadores

✓ Utilizando um decodificador III, crie uma saída /CS4 que selecione dispositivos de 1x8 no endereço 8EH

|                    | A7 | A6 | A5 | A4 | А3 | A2 | A1 | Α0 | Faixa da saída |

|--------------------|----|----|----|----|----|----|----|----|----------------|

| Saída Y2<br>de III | 1  | 0  | 0  | 0  | 1  | 1  | 1  | 0  | 8EH            |