## PMR3303 Eletrônica Digital para Mecatrônica

Prof. Dr. Celso M. Furukawa

Lista de Exercícios 11 (P2)

Entrega até 17/05/2019

(Os autores das melhores respostas, elaboradas de forma **comentada**, correta e clara, serão convidados a publicá-las na página de PMR3303 e receberão o número de Digis indicados nas questões.)

- Q1. (+4 Digis) Efetue as operações aritméticas a seguir representando as parcelas em complemento de 2 e com o número de bits indicado em cada item. Converta os resultados finais em decimal com sinal.

- a) Usando o menor número necessário de bits, efetue: 54 28.

- b) Usando 7 bits, efetue: -54 28.

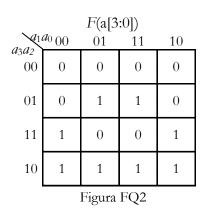

- Q2. (+4 Digis) Construa a função F representada no mapa de Karnaugh da figura FQ2 usando um multiplexador 8:1. Use as entradas  $a_3$ ,  $a_2$  e  $a_1$  como bits de seleção do multiplexador, e  $a_0$  para compor os bits de entrada.

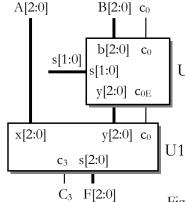

- Q3. (+8 Digis) A figura FQ3 mostra uma unidade aritmética e a tabela das operações que ela é capaz de efetuar. O bloco U1 é um somador completo de 3 bits e o bloco U2 é um extensor aritmético. Determine as expressões booleanas dos circuitos das saídas y[2:0] e  $a_{0E}$  do bloco U2, simplificadas na forma de soma de produtos. Não é necessário desenhar o diagrama lógico.

| S <sub>1</sub> S <sub>0</sub> | F              |

|-------------------------------|----------------|

| 0.0                           | $A + B + c_0$  |

| 0.1                           | A + 1          |

| 1 0                           | $(A - B)_{C2}$ |

| 1 1                           | $(A-1)_{C2}$   |

Figura FQ3

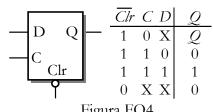

Q4. (+4 Digis) A figura FQ4 apresenta o símbolo e a tabela característica de um latch com *clear* assíncrono ativa em zero. Mostre como construí-lo usando um latch SR positivo ou SR negativo, a sua escolha. Desenhe o circuito e a tabela característica do latch SR escolhido.

- Q5. (+8 Digis) Considere que o mapa de Karnaugh da figura FQ2 represente um circuito combinacional de entrada a[3:0] formada por um barramento de 4 bits e saída F de um bit. Em linguagem Verilog, faça:

- a) Um módulo de nome MQ2 que implemente a função F.

- b) Um módulo *testbench* para executar a simulação do módulo MQ2. A simulação deve testar todas as combinações de entrada e imprimir os valores de entrada e saída.

## Algumas Respostas

- Q1a) 7bits: 001 1010 (+26); b) 010 1110 (+46, overflow)

- Q2) Entradas de dados do mux:  $I[7:0] = \{a0', a0', 1, 1, a0, a0, 0, 0\}$

- Q3) yi = bi'.s1 + s1.s0 + bi.s1'.s0' (i = 0, 1, 2);  $c0E = s1'.s0 + s1.s0' + {c0.s0' ou c0.s1'}$

- Q4) Latch positivo: S = Clr'.C.D, R = Clr + C.D'. Latch negativo: S' = Clr + C' + D', R' = Clr'.(C' + D).