# Open Source BDM-JM60 Users Guide

Revised: 16 November

Freescale, the Freescale logo, and CodeWarrior are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners.

© 2009-2011 Freescale Semiconductor, Inc. All rights reserved.

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

This product may be subject to special disposal requirements. For product disposal instructions, please refer to http://www.freescale.com/productdisposal.

| Corporate Headquarters | Freescale Semiconductor, Inc.        |  |  |  |

|------------------------|--------------------------------------|--|--|--|

|                        | 6501 William Cannon Drive West       |  |  |  |

|                        | Austin, Texas 78735                  |  |  |  |

|                        | U.S.A.                               |  |  |  |

| World Wide Web         | http://www.freescale.com/codewarrior |  |  |  |

| Technical Support      | http://www.freescale.com/support     |  |  |  |

## How to Contact Us

# **Table of Contents**

| 1 | Introduction to Open Source BDM          | 5  |

|---|------------------------------------------|----|

|   | About the Open Source BDM Interface      | 5  |

|   | History                                  |    |

|   | Open Source BDM Overview                 | 7  |

|   | JM60 Controller Application              | 7  |

|   | Open Source BDM Block Diagram            | 7  |

|   | OSBDM-JM60 Features                      | 9  |

|   | Open Source BDM Package                  | 10 |

|   | Support and Licensing                    | 12 |

| 2 | OSBDM-JM60 Hardware Reference Design     | 13 |

|   | OSBDM Options and Connections            | 13 |

|   | Options                                  | 14 |

|   | Connectors                               | 16 |

|   | Hardware Schematic Design                | 19 |

|   | Signal Chart                             |    |

|   | OSBDM Hardware Application               |    |

|   | OSBDM and JM60 Internal Support Circuits |    |

|   | OSBDM Target Support Circuits            |    |

|   | OSBDM Development Port Interfaces        |    |

| 3 | JM60 Firmware Application                | 31 |

|   | Firmware Block Diagram                   |    |

|   | Firmware Source Table                    |    |

|   | OSBDM-JM60 Specifications                |    |

| 4 | OSBDM PC Software Application            | 35 |

|   | Overview                                 |    |

|   | Open Source BDM GDI DLL                  |    |

|   | Open Source BDM DLL and LIBUSB           |    |

|   | OSBDM USB Base Driver API                |    |

|   | OSBDM USB Driver API                     | 40 |

|   |                                          |    |

## **Table of Contents**

|     | Target Specific Header Files                                  |     |

|-----|---------------------------------------------------------------|-----|

|     | Common Headers                                                | 41  |

|     | Update OSBDM-JM60 Firmware with Freescale JM60 GUI Applicatio | n45 |

| 5   | Installation and Operation of the OSBDM                       | 47  |

|     | Configuration of the Open Source BDM PCB                      | 47  |

|     | Open Source BDM PCB HCS08 Configuration                       | 47  |

|     | Installing Windows Open Source BDM DLL and USB Drivers        | 48  |

| Α   | Hardware Components List                                      | 51  |

| в   | OSBDM-JM60 Firmware Testing Criteria                          | 71  |

|     | Prerequisite                                                  | 71  |

|     | Connectivity Acceptance Criteria                              |     |

|     | Basic Debug Operation Testing Criteria                        | 72  |

|     | Combined Debug Operation Acceptance Criteria.                 | 72  |

|     | OSBDM-JM60 USB Driver Testing Criteria                        | 73  |

| Ind | dex                                                           | 75  |

1

# Introduction to Open Source BDM

This document describes an Open Source programming and debugging development tool designed to work with Freescale HCS08, RS08, Coldfire V1,V2, V3 and V4, and DSC56800E microcontrollers.

This chapter contains the following sections:

- <u>About the Open Source BDM Interface</u>

- <u>Open Source BDM Overview</u>

- Open Source BDM Block Diagram

- OSBDM-JM60 Features

- Open Source BDM Package

- Support and Licensing

# About the Open Source BDM Interface

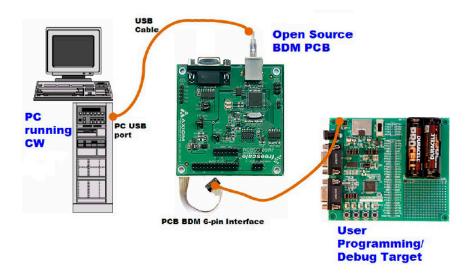

There is no support for Open Source BDM from Freescale, the Open Source BDM is provided with all required source code for both hardware and software components. Because it is open source, the source code can be used and/or modified from its original design free of charge. Figure 1.1 provides a pictorial overview of the typical connections required for programming and debugging using the Open Source BDM interface. A PC connects to the Open Source BDM PCB, in turn the PCB is connected to a Programming/ Debug target. In this example, the GB60 demonstration board is being programmed and debugged.

#### Introduction to Open Source BDM

About the Open Source BDM Interface

#### Figure 1.1 Debugging with OSBDM Interface

Open Source BDM (OSBDM), with its hardware and software components, provides a transparent connection between a computer running CodeWarrior Development Studio for MCU version to a Freescale HCS08, RS08, or Coldfire V1, V2, V3 and V4 microcontroller using BKGD pin. With a connection to the BKGD pin, the Open Source BDM enables debugger and other software tools to communicate with the microcontroller including downloading your code into the microcontroller's on-chip flash. Programming and debugger functionality is made possible by the microcontroller's Background Debug Controller (BDC) and its on-chip In-Circuit Emulation (ICE) system, if applicable.

## **History**

- TBDML Turbo BDM Light It is a low cost, open source debugging interface compatible with the CodeWarrior environment for the HCS12 of MCU family. It is based on the MC908JB08 MCU and updated to the MC908JB16 device.

- TBLCF Turbo BDM Light Coldfire It provides interface for the open source BDM project and also to the Coldfire V2, V3, and V4 microprocessors and microcontrollers and is based on the MC908JB16 MCU.

- OSBDM Open Source BDM It provides interface to 9S08, 9RS08, and Coldfire V1 type of target devices and also to the MC908JB16 MCU.

- OSBDM-JM60 9S08JM60 Based OSBDM It includes interfaces and firmware applied to all the targets supported by the previous open source BDMs. It includes new features and JTAG operations. It provides interface to 9S08, 9RS08, Coldfire

V1, V2, V3 and V4 target devices. It also includes JTAG connections for DSP56800E.

# **Open Source BDM Overview**

The OSBDM-JM60 provides a USB 2.0 compliant host interface and three BDM to target interface types. With the supporting modular software projects, BDM may be generated for any of the supported target interfaces. Additional review of the software for the interface type applied is necessary if any changes are made to the defined hardware interfaces. The software drivers associated with each interface will be identified.

## **JM60 Controller Application**

The Open Source BDM (OSBDM) is based on the MC9S08JM60 microcontroller with embedded USB port. All communication and control for BDM operation is performed by the JM60. The USB port provides the host communication and power source for the JM60 and BDM internal circuits. Peripheral devices and JM60 I/O ports provide the interface to target device, control and communication. JM60 internal flash memory contains all operating firmware for the BDM application. The JM60 firmware requires support by host PC USB drivers and software.

## **Open Source BDM Block Diagram**

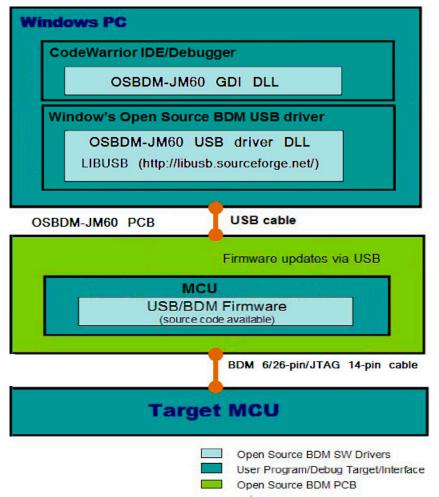

To better understand the implementation of the Open Source BDM, Figure 1.2 delineates the Open Source BDM solution into its most basic components. The diagram illustrates part of the Open Source BDM IP resides on the PC host for the debugging software and some resides on the Open Source BDM PCB.

At the time of release, the Open Source BDM is supported by the release of CodeWarrior Development Studio for Microcontrollers. The CodeWarrior provides both a software development IDE and a debugger.

#### Introduction to Open Source BDM

Open Source BDM Block Diagram

#### Figure 1.2 Block Diagram

Figure 1.2 illustrates five primary components, four components are software (shown in light blue color) and one component is hardware. All the software components are intended to be used as binaries. The source code of the JM60 firmware and the Open Source BDM interface DLL is explained in Table 1.1.

# **OSBDM-JM60** Features

The open source BDM is implemented with the following features:

- USB 2.0 compliant communication port with standard B or mini B type connector

- The target power is determined by the MCU when OSBDM is included on a target board. Target power option of 5V or 3.3V output. Power limited to USB requirements. Adjustable voltage output optional. Embedded OSBDM does not have the target power option

- Coldfire V2, V3, and V4 interface with port options

- BGND interface with options to support 9S08, 9RS08, and Coldfire V1 targets

- JTAG interface to support DSC targets and JTAG option operation on Coldfire V2, V3, V4 targets

- +12Vpp generation provided for 9RS08 target

- Status and Target Power Indicators

- Boot load option to update firmware using USB connection

- Debug port for the JM60 BDM controller

- · Low cost design, easy to embed on target boards requiring only one interface type

- Optional USB serial port application to pass target serial data to host Program Counter (PC) with USB connection

Open Source BDM Package

# **Open Source BDM Package**

## Table 1.1 Open Source BDM IP Components

| Component                     | Description/<br>Interfaces                                                                                                                                                                                                                                                                 | Available/Comments                                                                                                                                                                                                                                              |  |

|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Open Source BDM GDI<br>driver | File -<br>OpenSourceBDM_gdi.dll<br>Software interfacing with<br>the CW MCU debugger<br>GDI interface, providing<br>function call to the Open<br>Source BDM USB driver                                                                                                                      | This software is available<br>only as object code in the<br>form of a DLL                                                                                                                                                                                       |  |

| Open Source BDM USB<br>driver | File - OpenSourceBDM.dll<br>Software interfacing with<br>the Open Source BDM<br>GDI driver, providing<br>function calls to the<br>Windows USB drivers.<br>This file is also required<br>for the PC when it detects<br>the Open Source BDM<br>PCB as a new USB device<br>on the PC USB port | This software is available<br>as both object (DLL) and<br>source code. The DLL is<br>provided in an Open<br>Source BDM USB install<br>package. Point the PC<br>Hardware Wizard to the<br>USB install package when<br>the PC detected the Open<br>Source BDM PCB |  |

| Windows USB drivers           | File - libusb.lib Software<br>used by the Open Source<br>BDM USB driver it<br>interfaces to PC USB<br>ports                                                                                                                                                                                | This USB library is<br>compiled with the Open<br>Source BDM USB driver<br>and is also part of the<br>Open Source BDM USB<br>install package. The<br>source code for libusb can<br>be found at <i>http://</i><br><i>libusb.sourceforge.net/</i>                  |  |

## Introduction to Open Source BDM

Open Source BDM Package

| Component                                                  | Description/<br>Interfaces                                                                                                                                                                                                                                                                                               | Available/Comments                                                                                                                                                                                                        |  |

|------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| JM60 USB/BDM firmware                                      | File -<br>OpenSourceBDM.s19<br>Software running on the<br>JM60 that receives<br>commands via USB from<br>the PC and converts them<br>into commands as defined<br>by the BDC. These<br>commands are serial<br>outputted - "bit -banged" -<br>by the JM60 using port<br>pins to drive the BKGD pin<br>on the user's target | This file is provided as a<br>S-recorded and need to<br>be programmed JM60 on-<br>chip flash                                                                                                                              |  |

| Open Source BDM<br>Printed Circuit Board<br>(PCB) hardware | PCB: OpenSourceBDM<br>Pod ver 1.0, this hardware<br>contains the JM60 and<br>circuitry, clock, and power<br>to provide the interface to<br>the program or debug<br>target                                                                                                                                                | All schematics and gerber<br>files for the Open Source<br>BDM PCB is provided<br>along with a Bill Of<br>Materials (BOM). Also<br>included is a complete<br>HW description which<br>enables you to build the<br>interface |  |

## Table 1.1 Open Source BDM IP Components

This section describes the content of the Open Source BDM package. The package is distributed in zip file and includes development folders. The unzipped directory structure of the Open Source BDM package is shown in Figure 1.3.

#### Introduction to Open Source BDM

Support and Licensing

#### 🖃 🚞 osbdm-JM60\_b19Eng\_07112009 🚞 doc 🖃 🧰 qdi 🗉 🚞 bin 🚞 Classic-CW 🚞 Edipse-CW 🖃 🚞 osbdm-hw Component\_Data osbdm-sw Image: Second 🚞 doc 🚞 src 🖃 🚞 osbdm-JM60 🗉 🚞 bin 🚞 doc 🗄 🚞 src 🗉 🚞 tools 🖃 🧰 osbdm-pc 🗄 🚞 osbdmusb 🚞 osbdmusb\_api 🖃 🚞 osbdm-tester Source

#### Figure 1.3 Unzipped Open Source BDM Package

## Support and Licensing

Open Source BDM is not supported by Freescale; it is open source. Any bugs, enhancements, or support questions should be addressed through the Open Source BDM forum. Open Source BDM has been thoroughly tested, but there is no guarantee about error-free operation. All the source files, except GDI DLL, is available to anyone under the GNU LESSER GENERAL PUBLIC LICENSE. For more information on license, refer *COPYING\_LGPL.txt* file located at the root directory of the OSBDM-JM60 package. The Open Source BDM is a derivative project of the TBMDL project.

This chapter explains about OSBDM-JM60 hardware and its connections. It explains only standalone OSBDM board and not the circuits that are embedded onto an MCU board.

**NOTE** The testing criteria should be met while porting the Open Source BDM Reference Design (JM60) to an embedded OSBDM-JM60. For information on testing criteria, refer <u>OSBDM-JM60 Firmware Testing Criteria</u> appendix.

This chapter contains the following sections:

- OSBDM Options and Connections

- Hardware Schematic Design

- Signal Chart

- OSBDM Hardware Application

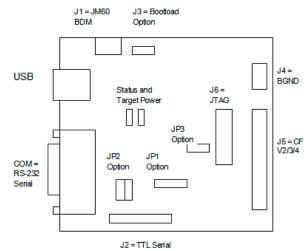

# **OSBDM Options and Connections**

The OSBDM reference design provides jumper options for feature and target settings. Jumper shunts are applied to enable a feature or option when installed on 2 pins. Option is disabled when the jumper shunt is placed on one pin or it is removed. In some cases, shunt is placed between two pins of a 3 pin header i.e. between pins 1 and 2 or between pins 2 and 3. This allows selection between two different functions. Ribbon cables are placed on the respective interface type pin headers to connect to the various supported target development ports. Only one target type is connected at a time.

OSBDM Options and Connections

#### Figure 2.1 Option and Connector Diagram

#### Figure 2.2 Connection Diagram

# Options

## JP1 — VOUT Select

JP1 allows the OSBDM to provide target power and apply the voltage level that is selected. The default option is shown in the idle position or no target power is applied. You must verify the target board's voltage level requirement, current requirement, and regulator type or other options prior to applying this option. You should avoid powering a target board voltage regulator's output or hardware failure could occur to the OSBDM, target board, and/or host PC USB port.

OSBDM Options and Connections

#### Figure 2.3 JP1 Option

## JP2 — 232 Enable

JP2 provides options to connect the OSBDM COM RS232 level serial port to the JM60 SCI0 serial port signals. J2 connection should not be applied, if this option is enabled. JM60 application supports the serial port operation. For information on input and output ports, refer to the <u>Signal Chart</u> section.

#### Figure 2.4 JP2 Option

**NOTE** The CTS signal operation is optional for flow control. The serial port of the target board may be connected to the OSBDM COM port and the COM port is connected to host PC with the USB cable.

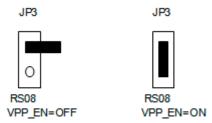

## JP3 — RS08 VPP Enable

JP3 provides Flash programming voltage (VPP) support for RS08 type targets. This option should not be enabled with any other target type. Otherwise, the OSBDM board and/or the target board may be damaged. When enabled, the OSBDM will provide the VPP voltage on the J4 pin 4 RESET\* signal under the application control. For information on power supply, refer to the <u>VPP Generator and Control</u> section.

OSBDM Options and Connections

#### Figure 2.5 JP3 Option

## J3 — IRQ/Bootload Mode Enable

J3 provides an option to enable the JM60 USB bootloader application. This application should reside in the JM60 flash firmware. Bootloader application is included in the OSBDM projects by default. J3 must be opted prior to connecting the OSBDM USB connector to the host PC. USB drivers must be installed on the host PC for proper operation. Refer *Application Note AN3561* for more information.

#### Figure 2.6 J3 Option

**NOTE** An option shunt is not provided for use on J3. When using the Boot load function, use the shunt from JP1, JP2, or JP3 and then return the shunt to the original position after boot load is complete.

## Connectors

## J1 — Debug JM60

J1 provides the development connection for the OSBDM JM60 controller. This connection is applied with an external BDM to support OSBDM development or JM60 flash programming. The USB connector or external BDM must power the OSBDM board

OSBDM Options and Connections

during development or flashing operations. It is possible to apply another external JM60 OSBDM to flash or debug the JM60 as a target on the OSBDM.

#### Figure 2.7 J1 Connector

| (JM60) BGND | 1 | 2 | GND         |

|-------------|---|---|-------------|

|             | 3 | 4 | RST* (JM60) |

|             | 5 | 6 | +5V         |

J1

## J2 — Serial Port (TTL)

J2 provides access to the JM60 SCI0 serial port signals and flow control I/O ports. The connection provides direct I/O port access to the JM60 and operates at 5V levels under application control. JP2 options should be OFF to apply this port connector. For information on input and output ports, refer to the <u>Signal Chart</u> section.

### Figure 2.8 J2 Connector

J2

| (Output) TXD | 1 |

|--------------|---|

| (Input) RXD  | 2 |

| (Input) CTS  | 3 |

| (Output) RTS | 4 |

| GND          | 5 |

## +5V Serial Port

## J4 — Target BGND Connector

J4 provides a 6 position ribbon cable connection to a BGND type target devices S08, RS08, and CF\_V1.

Before applying power, you must verify pin 1 alignment between the OSBDM and target BDM connector. Review JP1 and JP3 options. OSBDM JM60 application firmware must support the connected target type. Length of the ribbon cable should not exceed 8 inches.

OSBDM Options and Connections

#### Figure 2.9 J4 Connector

J4

| TBGND | 1 | 2 | GND      |

|-------|---|---|----------|

|       | 3 | 4 | TRG_RST* |

|       | 5 | 6 | +V_TRG   |

### RS08/S08/HC12/CF\_V1

## J5 — Target Coldfire V2/3/4 Connector

J5 provides the standard 26 pin ribbon cable connection for the Coldfire V2/3/4 type targets. Before applying power, you must verify pin 1 alignment between the OSBDM and target development connector. Review JP1 and JP3 options. OSBDM JM60 application firmware must support the connected target type. Length of the ribbon cable should not exceed 6 inches. This connection also supports the JTAG operation supported by Coldfire. Review target board options for BDM or JTAG operation support prior to application.

#### Figure 2.10 J5 Connector

| J5       |    |    |              |  |  |  |

|----------|----|----|--------------|--|--|--|

| NC       | 1  | 2  | BKPT* / TMS  |  |  |  |

| GND      | 3  | 4  | DSCLK / TRST |  |  |  |

| GND      | 5  | 6  | TCLK         |  |  |  |

| TRG_RST* | 7  | 8  | DSI/TDI      |  |  |  |

| +V_TRG   | 9  | 10 | DS0/TD0      |  |  |  |

| GND      | 11 | 12 | PST7 / DE*   |  |  |  |

| PST6     | 13 | 14 | PST5         |  |  |  |

| PST4     | 15 | 16 | NC           |  |  |  |

| NC       | 17 | 18 | NC           |  |  |  |

| NC       | 19 | 20 | GND          |  |  |  |

| NC       | 21 | 22 | NC           |  |  |  |

| GND      | 23 | 24 | NC           |  |  |  |

| NC       | 25 | 26 | TA*          |  |  |  |

CF\_V2/V3/V4

## J6 — Target DSC JTAG Connector

J6 provides the standard 14 pin ribbon cable connection for the DSC JTAG or OnCE type targets. Before applying power, you must verify pin 1 alignment between the OSBDM and target development connector. Review JP1 and JP3 options. JM60 OSBDM application firmware must support the connected target type. Length of the ribbon cable should not exceed 8 inches.

#### Figure 2.11 J6 Connector

| 50         |    |    |              |  |  |  |

|------------|----|----|--------------|--|--|--|

| DSI/TDI    | 1  | 2  | GND          |  |  |  |

| DS0/TD0    | 3  | 4  | GND          |  |  |  |

| TCLK       | 5  | 6  | GND          |  |  |  |

| NC         | 7  | 8  | KEY          |  |  |  |

| TRG_RST*   | 9  | 10 | BKPT* / TMS  |  |  |  |

| VDD        | 11 | 12 | NC           |  |  |  |

| PST7 / DE* | 13 | 14 | DSCLK / TRST |  |  |  |

16

## JTAG / OnCE

## **Power and Status Indicators**

A green Status and yellow Target Power (TPWR) indicators are provided. Both indicators operate under the application control and are not associated with any other hardware operation. Status indicator indicates OSBDM communication or operation with the host PC. TPWR indicator indicates target voltage is detected (target is powered) and the target should be operational.

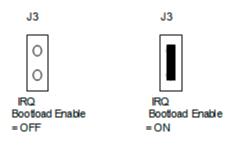

# Hardware Schematic Design

Figure 2.12 shows the schematic diagram of OSBDM-JM60.

Hardware Schematic Design

Figure 2.12 Schematic Design

# **Signal Chart**

Figure 2.13 shows the signal chart of the OSBDM-JM60.

## Figure 2.13 Signal Chart

| Pin           | MCU Signal       | PCB Signal            |          | Dir | LVL     | Notes | Comments                                             |

|---------------|------------------|-----------------------|----------|-----|---------|-------|------------------------------------------------------|

| $\rightarrow$ |                  |                       | Function | 2   |         |       |                                                      |

| 361           | BKGD/MS          |                       |          |     |         |       | Dedicated JM60 debug signal                          |

|               | IRQ/TPMCLK       | Bootload Enable       | GPIO     |     | low     | 1     | Update firmware Mode if Iow at Reset / power on      |

|               | PTB0/MISO2/ADP0  | +5VSW EN              | GPIO     | 0   | high    | 2     | Enable BDM interface power                           |

|               | PTB1/MISI2/ADP1  | +VTRG EN              | GPIO     | õ   | high    | 2     | Enable Target power out                              |

|               | PTB2/SPSCK2/ADP2 | TCLK CTL              | GPIO     | ŏ   | low     | 3     | Enable CF / JTAG TCLK output                         |

|               | PTB3/SS2*VADP3   | BRK TMS OUT           | GPIO     | Ō   | >>      | 3     | CF BRKPT* active low, JTAG TMS active high           |

|               | PTB4/KBIP4/ADP4  | TA OUT                | GPIO     | Ő   | high    | 3     | CF TA* output active high                            |

|               | PTB5/KBIP5/ADP5  | +VTRG IN              | ADC      | Ĭ   | .8-2.5v |       | Target power detection input, ADC measure            |

|               | PTC0/SCL         | P4 IN                 | GPIO     | i   | low     |       | CF PST4 input, halted detection                      |

|               | PTC1/SDA         | P5 IN                 | GPIO     | i   | low     |       | CF PST5 input, halted detection                      |

|               | PTC2             | P6 IN                 | GPIO     | -i- | low     |       | CF PST 6 input, halted detection                     |

|               | PTC3/TXD2        | P7 DE* IN             | GPIO     | ÷   | >>      |       | CF PST7 input, low halt detect, JTAG DE active high  |

|               | PTC4             | TRESET OUT            | GPIO     | 0   | high    |       | All target Reset* signal                             |

|               | PTC5/RXD2        | VPP ON                | GPIO     | ŏ   | high    |       | "+12V VPP supply enable                              |

|               | PTD0/ADP8/ACMP+  | PWR LED               | GPIO     | ŏ   | low     |       | Target power Status indicator                        |

|               | PTD1/ADP9/ACMP-  | STATUS LED            | GPIO     | ŏ   | low     |       | BDM status indicator                                 |

|               | PTD2/KBIP2/ACMP0 | TRESET IN             | GPIO     | Ť   | low     |       | S08/S12/V1 Target reset detect, add to CF port pin 1 |

|               | PTE0/TXD1        | TXD                   | СОМ      | 0   | >>      |       | COM port option TXD                                  |

|               | PTE1/RXD1        | RXD                   | COM      | -   | >>      |       | COM port option RXD                                  |

|               | PTE2/TPM1CH0     | TDSCLK EN             | GPIO     | 1/0 | >>      | 4     | CF DSCLK enable or JTAG TRST* signal                 |

|               | PTE3/TPM1CH1     | TCLK EN               | GPIO     | 1/0 | low     | -     | JTAG TCLK, tri state to clock, active to stop clock  |

|               | PTE4/MISO1       | DIN                   | SPI      | 1   | >>      |       | CF / JTAG data in                                    |

|               | PTE5/MOSI1       | DOUT                  | SPI      | 0   | >>      |       | CF / JTAG dtata out                                  |

|               | PTE6/SPSCK1      | SCLK OUT              | SPI      | ŏ   | ~~      |       | CF / JTAG serial clock out                           |

|               | PTE7/SS1*        | OUT EN*               | SPI      | ŏ   | low     |       | Enable Target interface outputs                      |

|               | PTF0/TPM1CH2     | VPP EN                | GPIO     | 0   | high    |       | VPP enable to RS08 target RESET signal               |

|               | PTF1/TPM1CH3     | TBGND IN              | GPIO     | ī   | >>      |       | S08/S12/V1 Target BGND input                         |

|               | PTF2/TPM2CH0     | TBGND OUT             | TPM      | 0   | >>      |       | S08/S12/V1 Target BGND output                        |

|               | PTF5/TPM2CH1     | TBGND EN              | TPM      | 0   | >>      |       | S08/S12/V1 Target BGND direction                     |

|               | PTG0/KBIP0       | +5VSW FAULT           | GPIO     | ī   | high    |       | BDM I/O power fault, disable on fault                |

|               | PTG1/KBIP1       | +VTRG FAULT           | GPIO     | i   | high    |       | Target Power fault, disable on fault                 |

|               | PTG2/KBIP6       | RTS                   | GPIO     | 0   | low     |       | COM port, transmit enable or RTS signal              |

|               | PTG3/KBIP7       | CTS                   | GPIO     | ī   | low     |       | COM port, CTS input                                  |

|               | PTG4/XTAL        | XTAL                  | XTAL     |     | 1011    |       | 4Mhz                                                 |

|               | PTG5/EXTAL       | XTAL                  | XTAL     |     |         |       | 4Mhz                                                 |

|               | RESET*           | RESET*                | XI/AL    | -   |         |       | JM60 input signal                                    |

|               | USBDN            | USBDN                 |          | 10  |         |       | USB                                                  |

|               | USBNP            | USBDP                 |          | 10  |         |       | USB                                                  |

|               | VDD              | +5V                   | PWR      |     |         |       |                                                      |

|               | VDDAD/VREFH      | +5V                   | PWR      |     |         |       |                                                      |

|               | VSS              | GND                   | PWR      |     |         |       |                                                      |

|               | VSSAD/VREFL      | GND                   | PWR      |     |         |       |                                                      |

|               | VSSAD/VREFL      | GND                   | PWR      |     |         |       |                                                      |

|               | VUSB33           |                       | PWR      |     |         |       | Decouple                                             |

| 20            | 100000           | internal regulator DP |          |     |         |       | Decoupie                                             |

2. Enables BDM Target output circuit power or Target power from USB source. Enable after USB power setting negotiated. Disable on USB Suspend detection.

3. This ouput to the target is enabled by the OUT\_EN\* signal.

TDSCLKEN provides the CF bit 17 clock signal and tristates or the JTAG TRST\* output active low.

OSBDM Hardware Application

# **OSBDM Hardware Application**

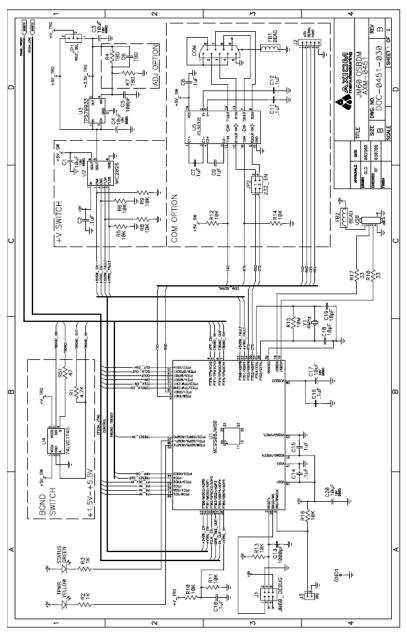

The OSBDM provide interfaces and controls supervised by the JM60 to operate different target devices and USB interface. Attempt has been made to provide a featured BDM connection with minimal cost. All development features of target device types are not supported to maintain a lower cost. The OSBDM-JM60 reference design provides multiple target device interfaces that may be applied separately in your designs or applications. The following sections describe the circuits and type of device supported. OSBDM-JM60 schematic diagram, materials list, and PCB layout files should be referred for application support. Figure 2.14 shows the block diagram of OSBDM-JM60.

#### Figure 2.14 OSBDM-JM60 Hardware Block Diagram

# OSBDM and JM60 Internal Support Circuits

The JM60 requires hardware support to operate the application. This section describes the common circuits for OSBDM operations.

## **Reference Clock**

The JM60 applies a 4.00MHz crystal reference (Y1) for USB communication timing on I/ O ports PTG4/XTAL and PTG5/EXTAL. The crystal applied is a standard parallel type with 50ppm maximum frequency tolerance. The value of load capacitors should be applied for the crystal selected in other designs.

JM60 initialization must configure the Multipurpose Clock Generator (MCG) to enable and apply the external crystal reference. MCG configuration sets the JM60 core and USB clocks to 48Mhz and the bus clock to 24Mhz for BDM operation. Time base for JM60 operation is 24Mhz or 41.67ns minimum time period.

Source code modules:

```

Main.c : MCG_Init function for initialization details and register settings.

```

## **USB** Connection

The JM60 USB connection is the primary host communication interface for application operation. The connection also powers the JM60 and OSBDM by default. The standard Freescale recommended hardware connection is applied with a USB type B connector. JM60 has dedicated I/O ports for the USB signal connections: USBDN and USBDP.

USB system operation is complex. For complete details of USB bus application and operation, refer to the *USB.org* specifications and documents. For basic details of JM60 USB application with a host PC, refer to the *JM60 USB GUI Application Note AN3561* The JM60\_OSBDM USB firmware application is a software port of the drivers.

Software Modules:

USB\_DRV Folder content USB\_User\_API.C

## **Power Control**

The OSBDM provides a dual power switch (U2/MIC2026) with current limit to power the OSBDM internally and the target, if enabled. Each switch provides an over current fault signal indication to the JM60 for the use of an application. At initial USB connection, the OSBDM is limited in power consumption by USB specifications and the power switches are OFF. After the USB connection with the host PC, additional power is applied and the JM60 will power the OSBDM internal circuits with switch A. During OSBDM application operation, the JM60 will power the target with power switch B. For information on the I/O ports applied for the switch and fault signals, refer to the <u>Signal Chart</u> section.

Power switch A provides +5V\_SW signal to power U4 (BGND transceiver), U5 (RS232 COM serial port transceiver), U8 (Coldfire V2/3/4 and JTAG input interface), and the VPP voltage generator. The VPP generator is OFF but power is applied by default.

OSBDM Hardware Application

Power switch B provides +V\_TRG output voltage to power the target using JP1 option. A 3.3V regulator (U3) is provided on the switch B output for target application. The regulator is a TPS79933 for a standard 3.3V output. Option is possible for other voltage outputs or an adjustable version of the regulator. Adjustable version is supported with resistor locations R4 and R7 to set the voltage level. +V\_TRG range of 1.8V to 4.5V when JP1 is set to the 3.3V position is possible with component options.

**NOTE** The OSBDM current should not exceed 500ma from the USB connection. This includes OSBDM power and target power if applied by JP1. Damage to the host PC USB port may occur if the current exceeds 500ma. Use caution while powering target boards from the OSBDM (JP1 ON). Verify that the target board voltage regulation output will not be powered again or conflict with the supplied OSBDM power. A power conflict could cause current limitations to be easily exceeded for a short duration of time.

## **OSBDM Target Support Circuits**

See the <u>Power Control</u> section for details on power control of the OSBDM and target power.

## +V Target Input

The JM60 ADC input channel 5 is applied to monitor the +V\_TRG voltage level. Input level to the ADC is set to 50% of the +V\_TRG level by resistors R10 and R11. Application should verify that the target is powered before attempting communication.

## **VPP Generator and Control**

VPP generation of +12V for RS08 flash programming support is provided by U6 and associated circuits. The JM60 enables the VPP generator with the VPP\_ON signal. Application of the VPP voltage to the target is enabled by the VPP\_EN signal. VPP application to the target is tightly integrated into the flashing commands for the RS08 target type. VPP voltage is applied to the TRG\_RST\* signal by JP3 option.

## Target Reset I/O

Target reset input and output is applied with discrete transistors Q1, Q3, Q5, and associated components. This circuit is used to provide a compliant interface to all of the supported target types. TRG\_RST\* signal output and input level is set by the +V\_TRG voltage level. The +12V VPP voltage appears on this signal, if applied.

TRG\_RST\* output is enabled by the TRESET\_OUT signal from the JM60. Target reset detection is provided on the TRESET\_IN signal to the JM60. The input provides the same logic level as the TRG\_RST\* signal level.

**NOTE** All the target types do not accept or provide a reset signal from this interface. In this case, an OSBDM command to the target is applied to produce a reset condition.

## **OSBDM Development Port Interfaces**

This section describes the individual development ports. Note that only one port type is applied to a target at any time.

## **BGND Interface**

The BGND interface provides the standard 6 pin connection for the single wire BGND signal type development port. Target types that apply this development port are the 9S08, RS08, and Coldfire V1. +V\_TRG, TBGND, TRG\_RST\*, and Ground are applied by this port type.

The BGND interface applies U4 as the signal transceiver. U4 is a 74LVC1T45 logic gate with voltage level shifting features. Operation on the target side (+V\_TRG) is 1.8V to 5.5V. The JM60 side is always +5V from the +5V\_SW signal. JM60 signals TBGND\_EN, TBGND\_IN, and TBGND\_OUT provide the communication and control for this interface. All these signals are associated with JM60 timer channels for precise timing capability to a 41.67ns time step period. For more information on the input and output ports, refer to the <u>Signal Chart</u> section.

TBGND\_ EN provides directional control for transmit or receive operations. The signal is logic high for transmit output and logic low to receive input. JM60 timer 2 channel 1 provides the primary signal direction control during the communication with the target. The idle condition is low so that the interface is not driven unless the communication is intended. During the communication, the direction is fixed to output the command to the target. During the reception, the signal is timed in edge aligned PWM mode to provide the BGND start pulse prior to the target reply input.

TBGND\_OUT provides the transmit signal output from the JM60 to the target. Timer 2 channel 0 controls this signal in edge aligned PWM mode. For data transmission, the timer channel will output an active low signal with a time period that represents a logic one bit value or logic 0 bit value. In receive mode, the timer channel will provide a low output for the start bit on the BGND signal and then provide timing internally for the reply signal input time window.

TBGND\_IN provides receive signal input from the target to the JM60. Timer 1 channel 3 is applied to measure the input signal duration in capture mode (25Mhz BDC clock

OSBDM Hardware Application

maximum). This operation provides the timing to determine a logic 1 or 0 bit value input from the target. RS08 type targets apply a lower speed communication technique that inputs the JM60 port value (sample mode) instead of using the timer capture. This is due to the RS08 will not provide a stable input signal after the start bit generation and creates false timer capture edges. Other undefined target types may exhibit the same issue and may apply sample mode, if required (10MHz BDC clock maximum).

**NOTE** The TBGND\_OUT and TBGND\_IN signals are connected with resistor R1. R1 provides isolation between the 2 timer channels.

## Coldfire V2/3/4 Interface

The Coldfire V2/3/4 interface provides the standard 26 pin interface for this target type. The interface is limited and does not support trace operations that require real time input of the development port PST and/or DAT signals. This interface applies these signals to the JM60.

Table 2.1 shows the signals and their operation notes of Coldfire interface.

Table 2.1 Signals and Operation Notes

| JM60 Signal | J5 Port Signal                       | Operation Notes                                    |

|-------------|--------------------------------------|----------------------------------------------------|

| TRESET_OUT  | TRG_RST*                             | Reset Target output                                |

| TCLK_CTL    | TCLK                                 | JTAG mode TCLK signal<br>output enable             |

| SCLK_OUT    | DSCLK_TRST*                          | Serial clock signal or<br>TRST control             |

| TCLK_EN     | TCLK                                 | Signal level override                              |

| OUT_EN      | DSCLK_TRST,<br>DSI_TDI,<br>BKPT*_TMS | Interface output enable for associated signals     |

| TDSCLK_EN   | DSCLK_TRST*                          | Signal level override                              |

| DOUT        | DSI_TDI                              | Serial Data output                                 |

| BRK_TMS_OUT | BKPT*_TMS                            | BDM Break signal or<br>JTAG TMS signal             |

| TA_OUT      | TA*                                  | Transfer acknowledge to target to clear Bus errors |

| DIN         | DSO_TDO                              | Serial data input                                  |

| JM60 Signal | J5 Port Signal | Operation Notes                               |

|-------------|----------------|-----------------------------------------------|

| P4_IN       | PST4           | Status bit 4                                  |

| P5_IN       | PST5           | Status bit 5                                  |

| P6_IN       | PST6           | Status bit 6                                  |

| P7_IN       | PST7_DE*       | Status bit 7 for BDM,<br>Debug event for JTAG |

Table 2.1 Signals and Operation Notes

Also applied is the +V\_TRG power signal. This interface operates from 2.5 to 5.5V target voltage levels.

Interface operation applies the JM60 Serial Peripheral Interface (SPI) for communication. Mode change from BDM (default) to JTAG is possible under the application control of the signals applied. For more information on JTAG mode of opeartion, refer to the <u>DSC</u> JTAG OnCE Interface section.

The SCLK\_OUT, DOUT, and DIN are the primary communication signals and are operated by the JM60 SPI. Maximum bit rate is 20% of the CPU bus speed of the Coldfire target device. The bit rate is fixed in the reference design to 125Khz for 500Khz minimum target clock. Due to the required shift between output and input bit clock edges, the first and last bit of the 17 bit transfer size is applied manually.

BRK\_TMS\_OUT is applied as the breakpoint or halt signal output in BDM mode. Assertion of this signal will stop target execution on the next instruction boundary.

TA\_OUT will assert the Coldfire target device Transfer Acknowledge (TA\*) or Transfer Error Acknowledge (TEA\*) signal, if connected. This signal may terminate a target bus cycle created in error or due to corrupt execution and prevent the need for a reset sequence.

P4\_IN to P7\_IN provide target core status signals. The OSBDM will apply these signals to detect that the core has halted execution. The reference design interface inverts the logic level of these signals from the target to the JM60. Target halts indication would be a logic high on all signals, input to the JM60 is a logic low on all signals to indicate a halt. Reduced pin package targets may provide a single ALLPST type output to indicate a run or halt condition. In this case, all PST\_IN signals should be connected to the ALLPST signal on the target development port and operation is transparent to the OSBDM. Embedded OSBDM designs may apply only the PST7/P7\_IN connection to the ALLPST target signal and adjust the application appropriately.

OSBDM Hardware Application

## DSC JTAG OnCE Interface

The DSC JTAG interface provides the standard 14 pin interface. Signal includes the JTAG mode of operation for the ColdIfire V2/3/4 targets. This interface applies these signals to the JM60.

Table 2.2 explain JM60 signals and operation notes of JTAG OnCE interface.

Table 2.2 Signals and Operation Notes of JTAG OnCE Interface

| JM60 Signal | J6 Port Signal                       | Operation Notes                                |

|-------------|--------------------------------------|------------------------------------------------|

| TRESET_OUT  | TRG_RST*                             | Reset Target output                            |

| TCLK_CTL    | TCLK                                 | TCLK signal output enable                      |

| SCLK_OUT    | DSCLK_TRST*                          | TRST control                                   |

| TCLK_EN     | TCLK                                 | Signal level override                          |

| OUT_EN      | DSCLK_TRST,<br>DSI_TDI,<br>BKPT*_TMS | Interface output enable for associated signals |

| TDSCLK_EN   | DSCLK_TRST*                          | Signal level override                          |

| DOUT        | DSI_TDI                              | Serial Data output                             |

| BRK_TMS_OUT | BKPT*_TMS                            | TMS signal                                     |

| DIN         | DSO_TDO                              | Serial data input                              |

| P7_IN       | PST7_DE*                             | Debug event input                              |

Also applied is the +V\_TRG power signal. This interface operates from 2.5 to 5.5V target voltage levels.

Interface operation applies JM60 I/O port manipulation. Serial Peripheral Interface (SPI) for communication may be possible in the future but is difficult to apply due to the random clock cycle to TMS signal level change requirements.

The TCLK\_EN, DOUT, and DIN provide the TCLK, TDI, and TDO JTAG signals. These signals are the primary communication signals for moving data to and from the target. Data bit count is variable on the transfers and may require sequence level changes of the TMS signal for correct operation of the interface with the target.

BRK\_TMS\_OUT is applied as the TMS signal output. This signal is sampled with clock changes to the target and must be modified during the data transfers for correct operation of the interface.

TDSCLK\_EN is applied as the TRST\* signal output. This signal is a test reset and does not reset the entire device.

TRESET\_OUT is applied as TRG\_RST\* signal. All DSC targets provide a RESET\* input pin that resets the DSC device, unless it is reconfigured as a GPIO.

P7\_IN is applied as the DE\* or Debug Event input signal. This signal is logic level inverted from the target. All the target do not support this signal output so it is treated as target specific.

# **JM60 Firmware Application**

The OSBDM-JM60 firmware application supports various target types, such as, HCS08, Coldfire V1, V2, V3, V4, and DSP56800E.

This chapter contains the following sections:

- Firmware Block Diagram

- Firmware Source Table

- OSBDM-JM60 Specifications

# **Firmware Block Diagram**

The JM60 BDM firmware application currently supports one target device type at a time. JM60 software for the BDM application is a CodeWarrior project that provides build target settings and software source modules corresponding to the BDM target device type. Correct target device type BDM interface hardware is required to support the firmware. Each CodeWarrior build target setting selects the associated software modules required to be included in the JM60 firmware to operate the BDM interface for the target device type.

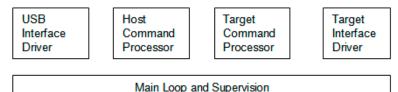

#### Figure 3.1 Firmware Block Diagram

A common USB interface driver and host command processor are applied for all target types. Target command processor and target interface driver are selected to support the specific target device. Common utility source files are also included.

# **Firmware Source Table**

Table 3.1 describes the association of various targets with the source files.

### Table 3.1 Description of Source Files

| Firmware Source File | Target Association | Function Summary                                                                                                              |

|----------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------|

| Start08.c            | JM60               | Reset Vector and start-up                                                                                                     |

| main.c               | All Targets        | Application start, main loop and management                                                                                   |

| cmd_processing.c     | All Targets        | Host command processor                                                                                                        |

| USB_User_API.c       | All Targets        | USB driver I/O, USB driver<br>is interrupt driven                                                                             |

| MCU.c                | JM60               | JM60 initialization and hardware support                                                                                      |

| bdm_9S08.c           | 9S08               | HCS08/9S08 target<br>specific command<br>processor                                                                            |

| bdm_cfv1.c           | Coldfire V1        | Coldfire V1/Flexis target<br>specific command<br>processor                                                                    |

| bdm_bgnd_driver.c    | S08                | Common BGND type<br>interface driver for higher<br>speed targets (Edge<br>capture type, 25Mhz<br>maximum target BDC<br>clock) |

| bdm_cf.c             | Coldfire V2/3/4    | Coldfire V2/3/4 Target<br>Specific Command<br>Processor and Interface<br>Driver                                               |

| jtag_dsc.c           | DSC JTAG           | DSC JTAG Target<br>Specific Command<br>Processor and Interface<br>Driver                                                      |

| timer.c              | All Targets        | Timer and timing support                                                                                                      |

### Table 3.1 Description of Source Files

| Firmware Source File | Target Association | Function Summary                           |

|----------------------|--------------------|--------------------------------------------|

| util.c               | All Targets        | Utility functions and<br>support           |

| serial_io.c          | All Targets        | Target Serial channel/<br>COM port support |

**NOTE** Main.c determines if the JM60 USB bootloader application or primary application starts. Each source file listed has one or more associated header files (.h extension) to provide the necessary definitions. Select the Header tab of the CodeWarrior project to edit these files.

# **OSBDM-JM60** Specifications

Table 3.2 describes the OSBDM-JM60 specification.

## Table 3.2 OSBDM-JM60 Specifications

| Specifications  |                                                                                                                 |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------|--|

| Input Voltage   | +5V from USB connection or JM60 BDM port, 40ma internal power                                                   |  |

| Output Voltages | +5V to target, 400ma maximum<br>+3.3V to target, 250ma maximum<br>+12V VPP programming voltage, 20ma<br>maximum |  |

| BGND Operation  | 200KHz to 25MHz target BDC clock, 1.8 to 5V signaling                                                           |  |

| Coldfire V2/3/4 | 500KHz minimum target clock, 2.5 to 5V signaling                                                                |  |

| JTAG            | 2.5 to 5V signaling                                                                                             |  |

NOTE BGND includes 9S08, and Coldfire V1 target type devices.

# JM60 Firmware Application OSBDM-JM60 Specifications

# OSBDM PC Software Application

This chapter describes the Open Source BDM solution PC software components.

This chapter contains the following sections:

- <u>Overview</u>

- Open Source BDM GDI DLL

- Open Source BDM DLL and LIBUSB

- <u>Update OSBDM-JM60 Firmware with Freescale JM60 GUI Application</u>

## **Overview**

This section describes the Open Source BDM solution PC software components. These components include:

- Open Source BDM Generic Debug Instrument (GDI) DLL plug-in for the CodeWarrior debugger

- Open Source BDM interface DLL

- USB driver (libusb.lib)

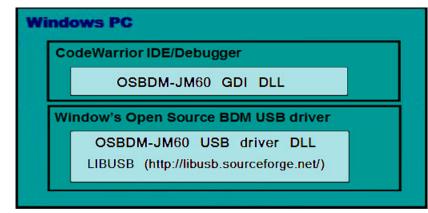

Figure 4.1 illustrates these software components and their interfaces.

### **OSBDM PC Software Application**

Open Source BDM GDI DLL

#### Figure 4.1 OSBDM Windows PC Software and Interfaces

# **Open Source BDM GDI DLL**

The Open Source BDM GDI DLL plug-in for the CodeWarrior debugger is only available as a binary file. No source code is provided. The GDI DLL for the CodeWarrior debugger is created partially based on information not available in the public domain. The license attached to these files does not allow disclosure of the file's source code.

The Open Source BDM takes advantage of the CodeWarrior Debugger's Generic Debug Instrument (GDI) protocol interface. For more information on GDI Open Interface Specification, see *http://www.tasking.com/resources/technologies/debuggers/gdikdi*.

# **Open Source BDM DLL and LIBUSB**

The Open Source BDM DLL provides an interface between the Open Source BDM GDI DLL and the Open Source BDM firmware. This section describes the API of the Open Source BDM DLL including a Windows Open Source USB drivers library, LIBUSB. The source code for the Open Source BDM DLL is available.

# **OSBDM USB Base Driver API**

Software applications interface to the OSBDM-JM60 firmware using the osbdm\_dll.h. The header files *commands*.h and *osbdm\_dll*.h contain all the definition used by these APIs that should be included in your project. The Open Source BDM DLL functions are listed and briefly described below:

#### unsigned char osbdm\_dll\_version(void)

Returns the version number of the osbdm\_dll.h in BCD format (major in upper nibble and minor in lower nibble).

### OsbdmErrT osbdm\_get\_version(unsigned char \*version\_info)

Returns the hardware (MSB) and firmware (LSB) version of the open OSBDM-JM60 device.

#### unsigned char osbdm\_init()

Initializes a connection to the USB driver and returns the number of OSBDM-JM60 devices found. If there is a problem communicating with the USB driver or other error then -1 is returned.

This function must be called before a device can be opened.

#### OsbdmErrT osbdm\_open(unsigned char device\_no)

Opens communication with an OSBDM-JM60 specified by device\_no. The first device is number 0.

Returns 0 on success and non-zero on failure. This function must be called before any further communication with the device can take place.

#### void osbdm\_close()

Closes communication with currently opened device.

#### OsbdmErrT osbdm\_target\_reset(ResetT resetmode)

Resets the MCU target using the resetmode value. Returns 0 on success and non-zero on failure. For more information on ResetT type defined in osbdm\_def.h, refer <u>Common Headers</u> section.

#### OsbdmErrT osbdm\_target\_go()

Starts target code execution from current PC address. Returns 0 on success and non-zero on failure.

#### OsbdmErrT osbdm\_target\_step()

Steps over a single target instruction. Returns 0 on success and non-zero on failure.

## OsbdmErrT osbdm\_target\_halt(void)

Brings the target into active background (debug) mode with user code execution halted. Returns 0 on success and non-zero on failure.

## OsbdmErrT osbdm\_get\_speed(unsigned long \*speed)

Returns the crystal (or external source) frequency of the target in KHz.

## OsbdmErrT osbdm\_set\_speed(unsigned long speed)

## **OSBDM PC Software Application**

Open Source BDM DLL and LIBUSB

Sets the BDM communication speed which is the crystal or external source frequency in KHz. Returns osbdm\_error\_ok on success or the error is defined in OsbdmErrT.

#### OsbdmErrT osbdm\_init\_hardware(void)

Initialize the OSBDM-JM60 BDM hardware and establish a connection between the OSBDM-JM60 probe. Returns osbdm\_error\_ok on success or the error is defined in OsbdmErrT.

#### OsbdmErrT osbdm\_status(unsigned char \*data)

Retrieve the target BDM communication status information to data. Returns osbdm\_error\_ok on success or the error is defined in OsbdmErrT.

## OsbdmErrT osbdm\_config(unsigned char config\_type, unsigned char config\_param, unsigned long param\_value)

Configure the OSBDM-JM60 and target. The configuration type config\_type, defined in ConfigT selects the entity to be configured. The configuration parameter config\_param, is set to the value specified in param\_value. Returns osbdm\_error\_ok on success or the error is defined in OsbdmErrT.

## OsbdmErrT osbdm\_write\_fill(unsigned char type, unsigned char width, unsigned long addr, unsigned char \*data, unsigned long count)

Fill a single value to a contiguous section of target's memory with an amount of count. The value to fill is written to data and addr is starting address in memory, type specifies the memory type for fill operation, which is defined in OsbdmMemT and width is the number of bits for the memory access size. Returns osbdm\_error\_ok on success or the error is defined in OsbdmErrT.

## unsigned char osbdm\_write\_block(unsigned char type, unsigned char width, unsigned long addr, unsigned char \*data, unsigned long size)

Writes a block of memory to the target.

## unsigned char osbdm\_read\_block(unsigned char type, unsigned char width, unsigned long addr, unsigned char \*data, unsigned long size)

Reads a block of memory from the target. Both osbdm\_read\_block and osbdm\_write\_block share the same parameters. Some of these parameters are also used by other memory functions.

Open Source BDM DLL and LIBUSB

<u>Table 4.1</u> describes the parameters of read and write memory functions.

## Table 4.1 Description of Parameters

| Parameters | Description                                                  |

|------------|--------------------------------------------------------------|

| type       | Type of memory to be read or written:                        |

|            | MEM_RAM - Normal memory                                      |

|            | MEM_REG - Normal register                                    |

|            | MEM_CREG - Control register                                  |

|            | MEM_DREG - Debug register                                    |

|            | MEM_P - Special Program Memory                               |

|            | MEM_P_FLASH - Special Program Flash<br>Memory                |

|            | MEM_X - Special Data Memory                                  |

|            | MEM_X_FLASH - Special Data Flash<br>Memory                   |

| width      | Number of bits to be read or written at a time (8, 16 or 32) |

| addr       | Start address                                                |

| data       | Pointer to the data to be written or to hold the data read   |

| size       | Number of 8-bit data bytes to be written or read             |

unsigned char osbdm\_write32(unsigned char type, unsigned long address, unsigned long data)

Write a single 32-bit value to target memory. Returns 0 on success and 1 on error.

unsigned char osbdm\_write16(unsigned char type, unsigned long address, unsigned short data)

Write a single 16-bit value to target memory. Returns 0 on success and 1 on error.

## unsigned char osbdm\_write8(unsigned char type, unsigned long address, unsigned char data)

Write a single 8-bit value to target memory. Returns 0 on success and 1 on error.

## unsigned long osbdm\_read32(unsigned char type, unsigned long address)

Read a single 32-bit value from target memory.

## **OSBDM PC Software Application**

Open Source BDM DLL and LIBUSB

unsigned short osbdm\_read16(unsigned char type, unsigned long address)

Read a single 16-bit value from target memory.

#### unsigned char osbdm\_read8(unsigned char type, unsigned long address)

Read a single 8-bit value from target memory.

unsigned long osbdm\_read\_bd(unsigned int address)

Read from the BDM memory area.

#### unsigned char osbdm\_write\_bd(unsigned int address, unsigned long data)

Write to the BDM memory area, returns 0 on success and non-zero on failure.

## **OSBDM USB Driver API**

## OsbdmErrT osbdmAPI\_connect(CoreT core\_type)

Connect to the device specified by core\_type and collect the BDM communication status information. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_get\_status(ConnectStateT \*status)

Get the target BDM communication status information, which contains the target reset state, the target connection state, the OSBDM-JM60 version, and the flash state. The ConnectStateT is defined in a common header file, osbdm\_def.h. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_run(void)

Start the execution of a core. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_step(void)

Step over a single target instruction. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_read\_mem(unsigned char mem\_space, unsigned int addr, unsigned int byte\_count, SizeT access\_size, unsigned char \*buffer)

Read byte\_count of data from the memory. The data is read into buffer and addr is the starting address in memory to begin read. Memory access attribute can be specified with access\_size whose type is defined in SizeT. The memory space mem\_space, is an optional target dependent parameter and it is defined in the target specific header. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_write\_mem(unsigned char mem\_space, unsigned int addr, unsigned int byte\_count, SizeT access\_size, unsigned char \*buffer)

Write byte\_count of data to the memory. The data is written to buffer and address is the starting address in memory to begin write. Memory access attribute can be specified

with access\_size whose type is defined in SizeT. The memory space mem\_space, is an optional target dependent parameter and it is defined in the target specific header. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_config(ConfigT config\_type, unsigned char config\_param, unsigned long param\_value)

Configure the OSBDM-JM60 and target. The configuration type config\_type, defined in ConfigT selects the entity to be configured. The configuration parameter config\_param, is set to the value specified in param\_value. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_core\_mode(CoreModeT \*core\_mode)

Poll the execution mode of the core and returns the mode defined in CoreModeT. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## OsbdmErrT osbdmAPI\_secure\_mode(SecureModeT \*secure\_mode)

Poll the target secure mode and return the mode defined in SecureModeT. Returns osbdm\_error\_ok on success or the error defined in OsbdmErrT.

## **Target Specific Header Files**

## osbdm\_cfv1.h

The header file contains Coldfire V1 target specific definitions that are used in the OSBDM-JM60 API. Coldfire V1 register numbers are defined in this header file.

## osbdm\_cfv234.h

The header file contains Coldfire V2/3/4 target specific definitions that are used in the OSBDM-JM60 API. Coldfire V2/3/4 register numbers are defined in this header file.

## osbdm\_s08.h

The header file contains HCS08 target specific definitions that are used in the OSBDM-JM60 driver API. HCS08 register numbers are defined in this header file.

## osbdm\_dsc.h

The header file contains DSC target specific definitions that are used in the OSBDM-JM60 driver API. DSC register numbers are defined in this header file.

## **Common Headers**

## osbdm\_configparam.h

The header file contains the definition for the OSBDM-JM60 configuration parameters.

```

typedef enum {

osbdmcfg = 0x10, // osbdm-JM60 config

```

Open Source BDM DLL and LIBUSB

```

tgtcfg_generic = 0x40, // generic target config

tgtcfg_specific= 0x80 // target specific config

```

} configType;

#### osbdm\_def.h

The header file contains the definition that is used for both OSBDM-JM60 driver APIs and OSBDM-JM60 base driver APIs. It includes header files <code>osbdm\_configparam.h</code> and <code>osbdm\_memtype.h</code>. OsbdmErrT, ResetT, FlashStateT, CoreT, SizeT, CoreModeT, SecureModeT, TargetResetDetectT, TargetConnectStateT, ConnectStateT, OsbdmInfoT are defined in this header file.

```

typedef enum {

osbdm_error_ok,

osbdm_error_fail,

osbdm_error_invalid_parameter,

osbdm_error_not_supported,

osbdm_error_usb_transport,

osbdm_error_cmd_failed,

osbdm_error_bdm_not_enabled,

osbdm_error_undefined

}OsbdmErrT;

```

```

/* type of reset mode */

typedef enum {

eSoftReset_to_DebugMode,

eSoftReset_to_NormalMode,

eHardReset_to_DebugMode,

ePowerReset_to_DebugMode,

ePowerReset_to_NormalMode

} ResetT;

typedef enum {

eCFv234,

eCFv1,

```

## **OSBDM PC Software Application**

Open Source BDM DLL and LIBUSB

```

eRS08,

eS08,

eDSC,

eCoreTypeUnknown

} CoreT;

typedef enum {

eByte, // 1 byte

eWord, // 2 bytes

eLong // 4 bytes

} SizeT;

/* type of core run state */

typedef enum {

eDebug,

eRunning,

eWait,

eStopped,

eWaitOrStopped,

eBusy,

eCoreModeUndefined

} CoreModeT;

/* type of secure mode */

typedef enum {

eSecured,

eUnsecured,

eSecureModeUndefined,

} SecureModeT;

/* target reset detection state */

typedef enum {

```

Open Source BDM DLL and LIBUSB

```

RESET_INACTIVE,

RESET_DETECTED,

RESET_UNDEFINED

} TargetResetDetectT;

/* target connection state */

typedef enum {

NO_CONNECTION = 0,

SYNC = 1,

RESERVED = 2,

MANUAL\_SETUP = 3,

CONNECT_UNDEFINED

}TargetConnectStateT;

/* target BDM communication state */

typedef struct {

TargetResetDetectT reset_state;

TargetConnectStateT connect_state;

unsigned int

osbdmJM60_version;

FlashStateT

flash_state;

} ConnectStateT;

typedef struct {

```

```

ConnectStateT connect_state;

CoreT coreid;

} OsbdmInfoT;

```

#### osbdm\_memtype.h

The header file contains the memory type definitions that are used for both OSBDM-JM60 driver API and OSBDM-JM60 base driver API.

```

typedef enum {

MEM_RAM =0, // Memory

MEM_REG =1, // Register

```

## **OSBDM PC Software Application**

Update OSBDM-JM60 Firmware with Freescale JM60 GUI Application

```

MEM_CREG =2, // Control Register

MEM_DREG =3, // Debug Register

MEM_P =10, // Program Memory

MEM_P_FLASH =11, // Program Flash Memory

MEM_X =12, // Data Memory

MEM_X_FLASH =13 // Data Flash Memory

} OsbdmMemT;

```

#### osbdm\_utils.h

The header file contains utility functions that are used in both OSBDM-JM60 USB driver API and OSBDM-JM60 USB base driver API. Byte ordering utility functions is defined in this header file.

## Update OSBDM-JM60 Firmware with Freescale JM60 GUI Application

The Freescale JM60 GUI application includes a GUI version of the bootloader that can be used to program the OSBDM-JM60 firmware. You can download JM60 GUI installer from Freescale website using the following link: *http://www.freescale.com/webapp/sps/ download/license.jsp?colCode=JM60\_GUI\_INSTALLER\_V1.2&location=null&fsrch=1*

When OSBDM-JM60 firmware is installed with the bootloader library (by a debugger that can program the OSBDM-JM60 through the BDM connection), the firmware can be erased and reprogrammed with the JM60 GUI tool.

For the standalone (i.e. non-embedded version) OSBDM-JM60, when the jumper J3 is set to the ON position it activates the bootloader mode on connecting the USB cable to the OSBDM-JM60 board. When the JM60 GUI tool recognizes the OSBDM-JM60 in the bootloader mode, the color of the bottom right USB symbol of the JM60 GUI changes from red to green.

The following are the steps for updating OSBDM-JM60 firmware with Freescale JM60 GUI tool:

1. Install the JM60 GUI application.

```

NOTE You can download the JM60 GUI application from the Freescale website:

www.freescale.com/webapp/sps/download/

license.jsp?colCode=JM60 GUI_INSTALLER_V1.2&location=null&fsrch=1

```

2. Set the J3 jumper to the ON position.

Update OSBDM-JM60 Firmware with Freescale JM60 GUI Application

- 3. Connect the USB cable to the OSBDM-JM60 pod and this will launch the Found New Hardware Wizard for the Freescale JM60 Bootloader device.

- 4. Install the drivers.

- 5. Open the Freescale JM60 GUI. The USB symbol in the bottom right corner of the JM60 GUI should be green if the bootloader is activated.

- 6. Select the Bootloader from the JM60 Application menu.

- 7. Load the firmware SREC file located at: *(OSDMPackageDir)\osbdm-sw\osbdm-JM60\bin* from the JM60 USB Bootloader window.

- 8. Click Execute on the JM60 USB Bootloader window.

- 9. Do not interrupt the firmware update process until it is completed.

- 10. Close the Freescale JM60 GUI application.

- 11. Disconnect the USB cable.

- 12. Set the J3 jumper to the OFF position.

# Installation and Operation of the OSBDM

This chapter contains the following sections:

- <u>Configuration of the Open Source BDM PCB</u>

- Installing Windows Open Source BDM DLL and USB Drivers

## **Configuration of the Open Source BDM PCB**

This section describes that the Open Source BDM firmware is programmed on to the JM60.

## Open Source BDM PCB HCS08 Configuration

<u>Table 5.1</u> details the Open Source BDM PCB jumper configuration settings for Programming and debugging targets for the HCS08. Other types of target may require other settings.

## Table 5.1 OSBDM PCB HCS08 Configuration

| Jumper | Description            | Settings                                                                                                                   |

|--------|------------------------|----------------------------------------------------------------------------------------------------------------------------|

| JP1    | Target Power Selection | Short 1-2: Power target<br>externally via J1 or target<br>is self powered<br>Short 2-3: Power target<br>using 5V USB power |

| JP3    | Flash Program          | Off                                                                                                                        |

| JP4    | Flash Program          | Off                                                                                                                        |

| JP5    | Flash Erase            | Off                                                                                                                        |

Installing Windows Open Source BDM DLL and USB Drivers

# Installing Windows Open Source BDM DLL and USB Drivers

The following procedure specifies the installing of the Open Source BDM USB hardware drivers on the Windows operating system. In this procedure, it is assumed that Open Source BDM Windows USB driver package is unpacked onto the development PC, running the CodeWarrior Studio.

With the Open Source BDM PCB configured, the Open Source BDM PCB can be connected to the development PC USB port. When configured Open Source BDM PCB is connected to the PC for the first time, the Windows operating system recognizes a new USB device, the Open Source BDM PCB. Figure 5.1 illustrates that the initial connection starts the Windows driver installation and displays Windows New Hardware Wizard dialog box.

## Figure 5.1 Found New Hardware Wizard

| Found New Hardware Wiz | ard                                                                                                                               |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------|

|                        | Welcome to the Found New<br>Hardware Wizard                                                                                       |