# Departamento de Engenharia Elétrica e de Computação SEL 384 – Laboratório de Sistemas Digitais I

### PRÁTICA №07

"Dispositivos de Lógica Programável de Complexo (CPLD- "Complex Programable Logic Devices")- Circuitos Sequenciais: Aplicação de contadores"

## 1. Objetivos:

- Projeto e síntese de circuitos sequenciais em dispositivo FPGA utilizando o esquemático do Quartus II;

- Aplicação de contadores e decodificadores.

#### 2. Material utilizado:

- Configuração de Dispositivo Programável de Alta Complexidade HCPLD do tipo FPGA

Cyclone IV da Altera

- Módulo de desenvolvimento Mercúrio IV Macnica DWH

- Multímetro

## 3. Procedimento Experimental:

Utilizando o software QUARTUSII v.12.OSP2, escolha o dispositivo HCPLD Cyclone IV EP4CE30F23C7 e faça um projeto para acionamento da matriz de LEDs de 8 linhas x 5 colunas do módulo de desenvolvimento Mercúrio IV, que realize o seguinte procedimento: acenda todos os 5 LEDs da mesma linha simultaneamente e sequencialmente a cada 5Hz, de maneira a fazer a varredura nas 8 linhas de cima para baixo e, de baixo para cima.

As 5 colunas são nomeadas como LEDM\_C[0] até LEDM\_C[4], as 8 linhas como LEDM\_R[0] a LEDM\_R[7]. Ambas, linhas e colunas,são selecionadas com o nível '0'. O clock interno de 50MHz é nomeado como CLOCK\_50MHz.

- 3.1 Inicialmente implementar o divisor de frequência para gerar 5Hz a partir de 50MHz interno à placa(CLOCK\_50MHz.). Para isso utilize o projeto lpm\_counter da biblioteca Megafunction e verifique a frequência de 5Hz no LED RGB, criando uma saída LED\_R (ou LED\_G ou LED\_B). Obs: veja informações sobre o projeto lpm\_counter no final desse arquivo.

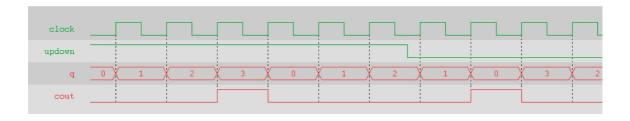

- 3.2 Utilize outro contador lpm\_counter para implementar um contador crescente/decrescente de 0 a 7. Criar entrada UP/DOWN e saída Cout.

- 3.3 Ligar as saídas binárias do contador do item 3.2 a um decodificador 3X8, 74138.

- 3.4 Utilizando a entrada UP/DOWN e saída Cout do contador do item 3.2 implemente o controle para contagem crescente e decrescente.

- 3.5 Ligar as saídas do decodificador às linhas da matriz de LEDs.

- 3.6 Para ativar as colunas da matriz criar pinos de saída (output) para cada coluna da matriz LEDM C[0] até LEDM C[4].

- 3.7 Configure o dispositivo no módulo de desenvolvimento Mercúrio IV e teste os circuitos projetados nos itens anteriores. Para programar a chave 1 do Kit deve estar na posição PROG FPGA e a chave 2 na posição ON. (como mostrado no Guia Rápido Mercúrio IV).

- 3.8 Mostre o funcionamento do circuito sintetizado no FPGA após a programação.

- 3.9 Como relatório entregue o circuito esquemático documentado.

Para criar um arquivo de projeto esquemático no software QuartusII siga os passos do arquivo "Manual QUARTUS" que se encontra no Moodle disciplinas Stoa USP.

# INFORMAÇÕES SOBRE O PROJETO LPM\_COUNTER:

# INPUT PORTS

| Port Name | Required | Description                                                                     | Comments                                                                                                                                                 |  |  |

|-----------|----------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| clock     | Yes      | Positive-edge-triggered clock.                                                  |                                                                                                                                                          |  |  |

| updown    | No       | Controls the direction of the count. High (1) = count up. Low (0) = count down. | Default = up (1). If the LPM_DIRECTION parameter is used, the updown port cannot be connected. If LPM_DIRECTION is not used, the updown port is optional |  |  |

#### **OUTPUT PORTS**

|   | Port Name | Required | Description                   | Comments                                                                                       |  |  |

|---|-----------|----------|-------------------------------|------------------------------------------------------------------------------------------------|--|--|

| q | (1)       | No       | Data output from the counter. | Output port LPM_WIDTH wide. Either q[] or at least one of the eq[150] ports must be connected. |  |  |

| c | out       | No       | Carry-out of the MSB.         |                                                                                                |  |  |

## Truth Table/Functionality:

|      | Inputs |       |        |       |      |      |       |        |        | Outputs         | Function                                           |

|------|--------|-------|--------|-------|------|------|-------|--------|--------|-----------------|----------------------------------------------------|

| aclr | aset   | aload | clk_en | clock | sclr | sset | sload | cnt_en | updown | q[LPM_WIDTH-10] |                                                    |

| 1    | х      | х     | х      | х     | х    | х    | х     | х      | х      | 000             |                                                    |

| 0    | 1      | х     | х      | х     | х    | х    | х     | х      | х      | 111             |                                                    |

| 0    | 1      | х     | х      | х     | х    | х    | х     | х      | х      | LPM_AVALUE      | Asynchronous set to value specified for LPM_AVALUE |

| 0    | 0      | 1     | х      | х     | х    | х    | х     | х      | х      | data[]          | Asynchronous load from data[] input                |

| 0    | 0      | 0     | 0      | x     | х    | х    | х     | х      | х      | ā[]             | Hold current count value                           |

| 0    | 0      | 0     | 1      | ı     | 1    | х    | х     | х      | х      | 000             | Synchronous clear                                  |

| 0    | 0      | 0     | 1      | ſ     | 0    | 1    | х     | х      | х      | 111             | Synchronous set                                    |

| 0    | 0      | 0     | 1      | l     | 0    | 1    | х     | х      | х      | LPM_SVALUE      | Synchronous set to value specified for LPM_SVALUE  |

| 0    | 0      | 0     | 1      | ſ     | 0    | 0    | 0     | 0      | 0      | ā[]             | Hold current count value                           |

| 0    | 0      | 0     | 1      | ı     | 0    | 0    | 1     | х      | х      | data[]          | Synchronous load from data [] input                |

| 0    | 0      | 0     | 1      | ſ     | 0    | 0    | 0     | 1      | 1      | q[]+1           | Count up                                           |

| 0    | 0      | 0     | 1      | ſ     | 0    | 0    | 0     | 1      | 0      | q[]-1           | Count down                                         |

# 4. Bibliografia:

- Site da ALTERA

- Fregni, E. & Saraiva, A.M., "Engenharia do Projeto Lógico Digital", Ed. Edgard Blücher Ltda.

- Tocci, J. R., "Sistemas Digitais- Princípios e Aplicações