## SUMÂRI O

- Introdução MEMS/MST

- Aplicações de MEMS/MST

- Encapsulamentos para MEMS

- Hierarquia do encapsulamento eletrônico

- Hierarquia do encapsulamento para MEMS

- Introdução ao Encapsulamento Eletrônico

- Mecanismos de falha em MEMS

- Encapsulamento a nível do Die

- Encapsulamento a nível do Dispositivo

- Encapsulamento a nível do Sistema

- Técnicas de encapsulamento 2D e 3D

- Micro-Sistemas Modulares

- Bibliografia

## QUE É MEMS OU "MI CROSYSTEM TECHNOLOGY" (MST)?

• É uma estratégia que utiliza os mesmos princípios e técnicas da microeletrônica para a miniaturização e integração de sistemas e componentes elétricos, mecânicos, acústicos, magnéticos, óticos, térmicos, químicos ou bio-tecnológicos

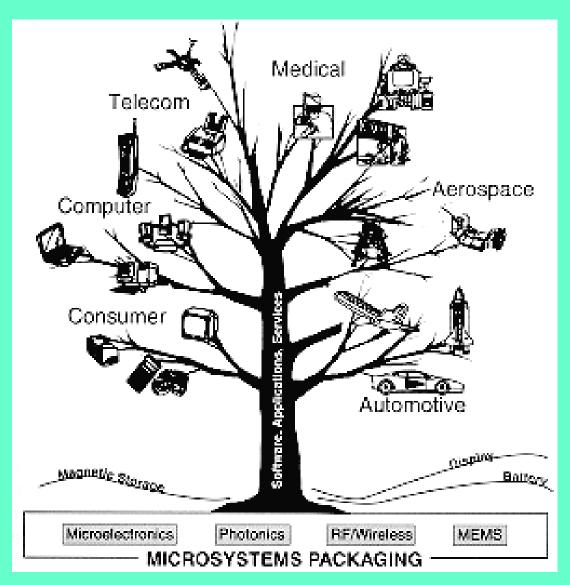

# APLICAÇÕES DOS MICROSSISTEMAS

- Automotiva /Transporte

- Tecnologia da Informação, Periféricos

- Telecomunicações

- Medicina / Biomedicina

- Meio ambiente / Processos industriais

- Artigos de consumo/ Entretenimento

- Outras Aplicações

(Defesa, Aeroespacial)

# APLICAÇÕES DE MEMS/MST

- O espectro de produtos onde a microtecnologia está presente é muito amplo:

- Tecnologia Médica

- Desenvolvimento de remédios

- Armazenamento de Informações

- Componentes para redes

- Displays planos

- Micro sensores na industria automotiva

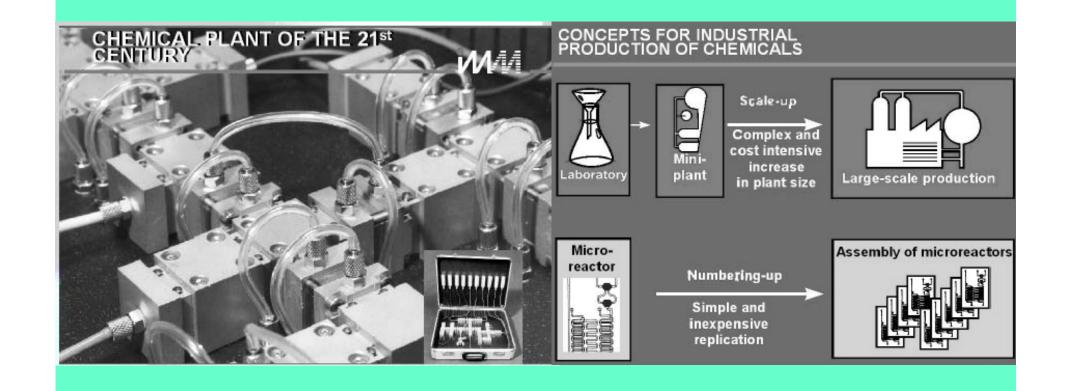

- Micro reatores para pesquisa de materiais e processos químicos

Aeroespacial Defesa Tecnologia de Informação

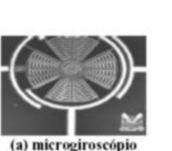

(b) micromotor

(e) microtips

**Química** Analítica Biotecnologia Farmacêutica Telecomunicações

(c) microfiltro para RF

(f) microturbina

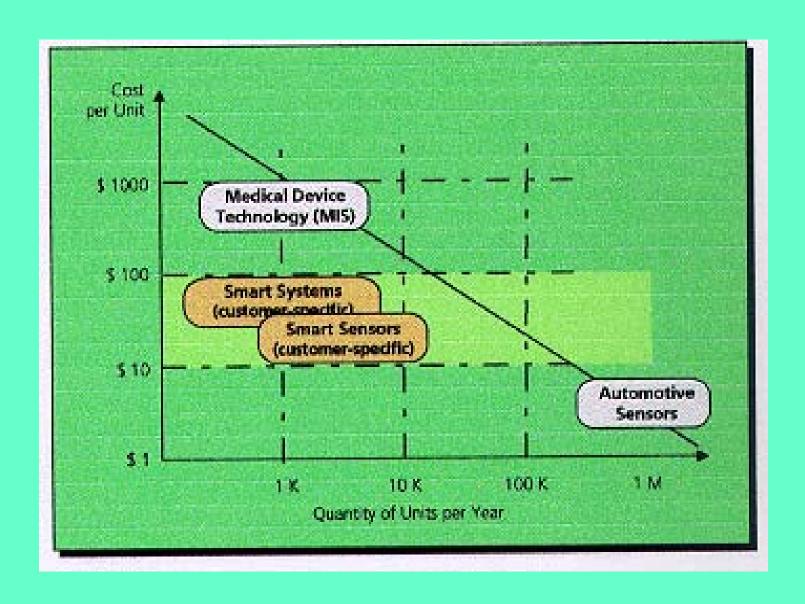

#### CUSTO ESPERADO PARA "SMART SYSTEMS"

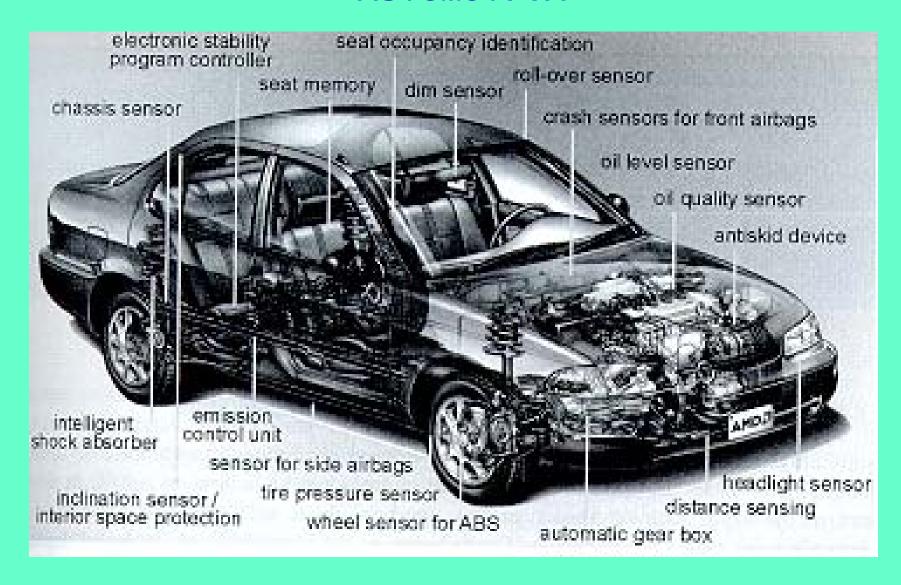

# APLICAÇÕES DE MST/MEMS NA INDUSTRIA AUTOMOTIVA

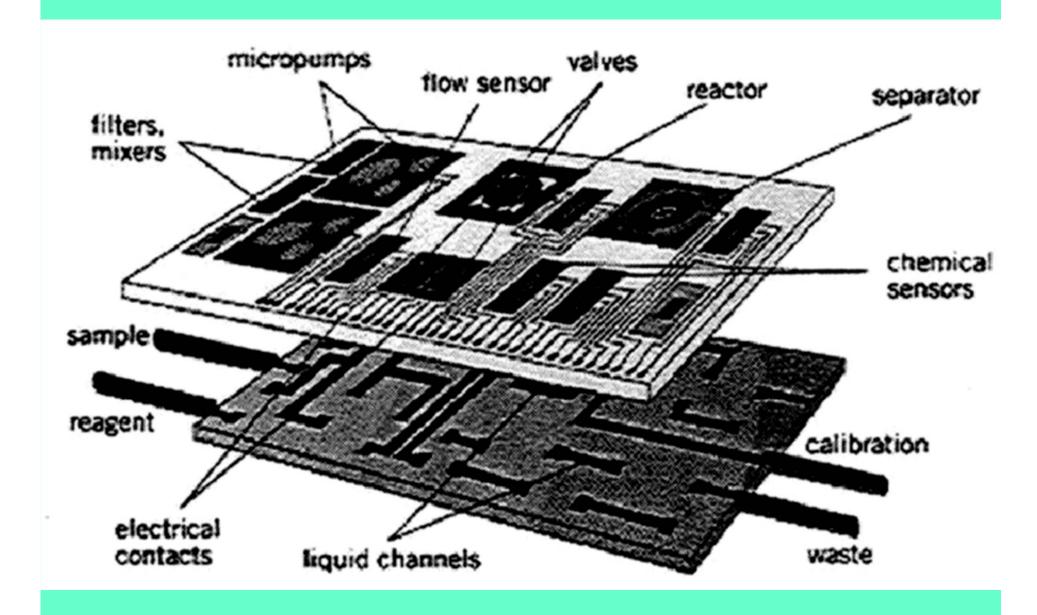

## "LAB ON A CHIP"

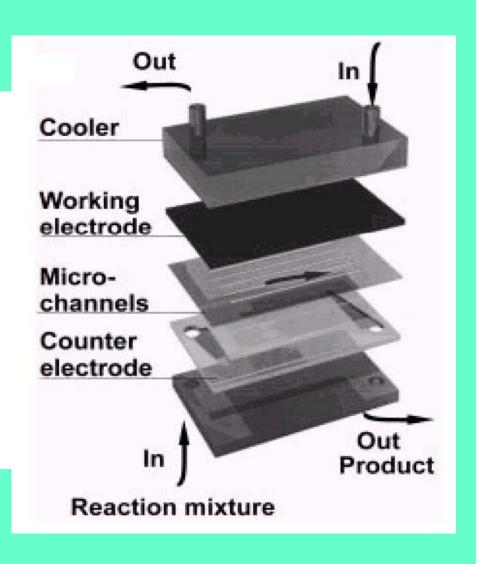

# SISTEMAS MICRO-QUÍMICOS

- Micro tecnologia é não agressiva ao meio ambiente

- Poupa recursos

- Fornece Miniaturização

- Melhora o controle dos processos

- Permite processamento Paralelo

- Problemas de segurança menores

Conventional tools

New tools: Micro Chemical and Thermal Systems

# EVOLUÇÃO FUTURA DO PROCESSAMENTO QUÍ MI CO

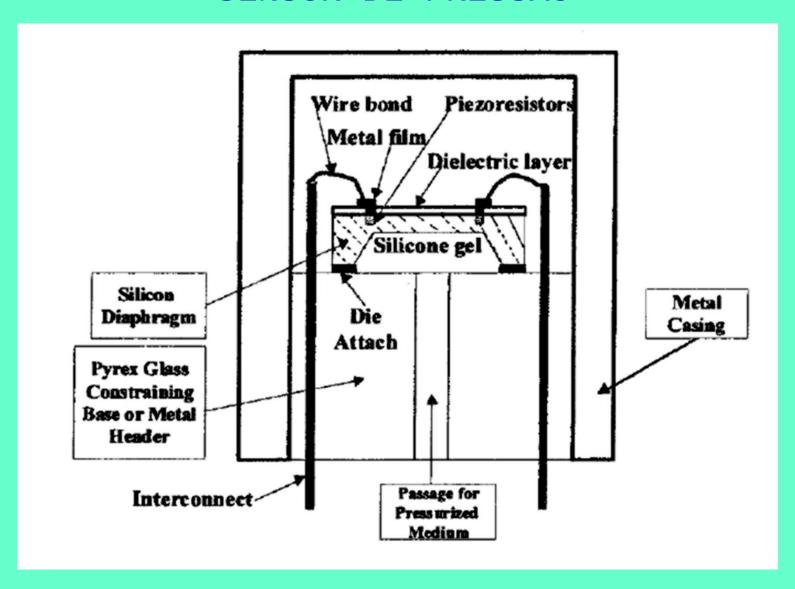

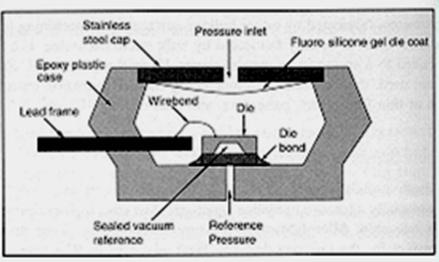

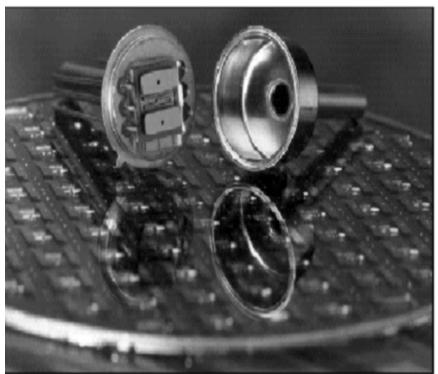

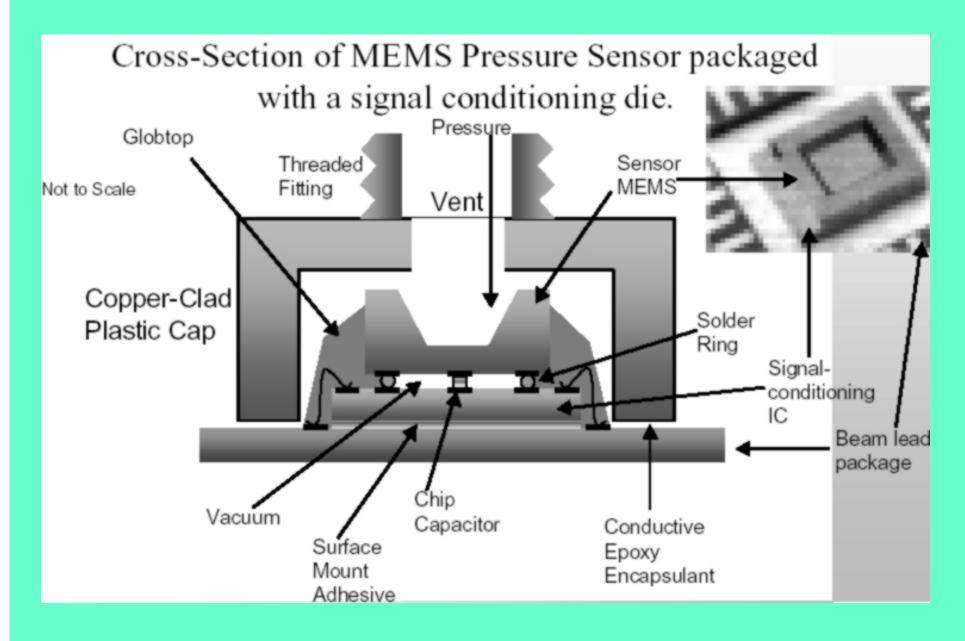

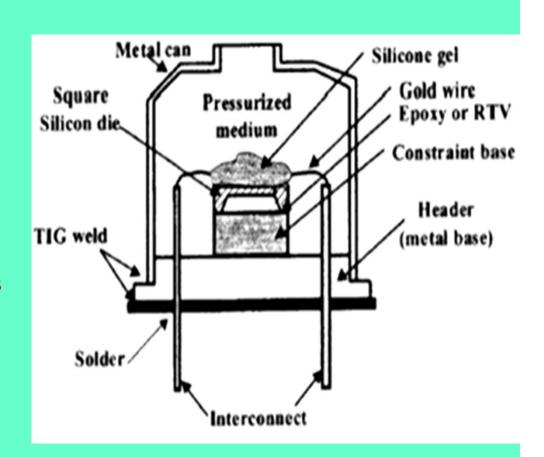

# PRIMEIRO ENCAPSULAMENTO DE MEMS SENSOR DE PRESSÃO

### SENSORES DE PRESSÃO PIEZORESISTIVOS

- Os sensores de pressão são o primeiro produto MEMS/MST a ser produzido em larga escala.

- A Piezo resistividade é um propriedade dos materiais onde a resistência de corpo é influenciada pela tensão mecânica aplicada ao dispositivo

- Piezo resistores comuns:Si, Si poly, SiO2 e ZnO

- Projeto típico: 4 piezo resistores em uma ponte de Wheatstone num diafragma de Si

- Sensibilidade de pressão(mV/V-bar):  $S = (\Delta R/\Delta P)(1/R)$

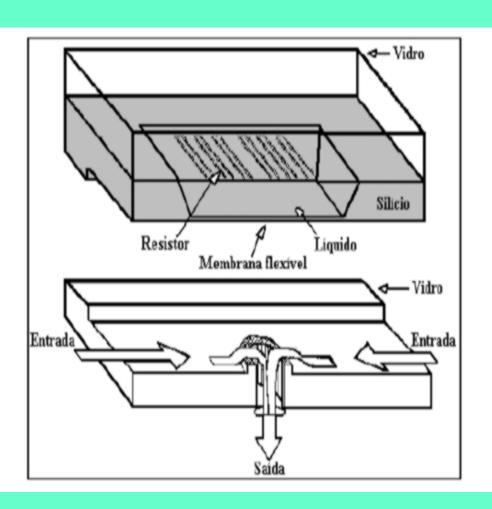

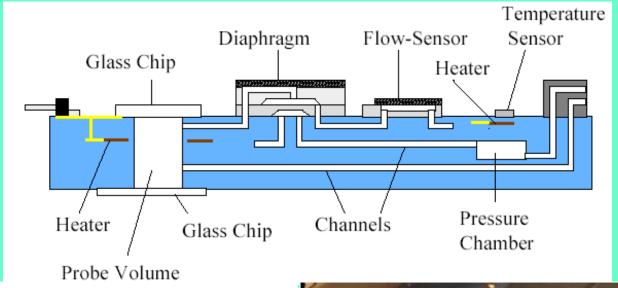

# MI CROFLUI DI CA

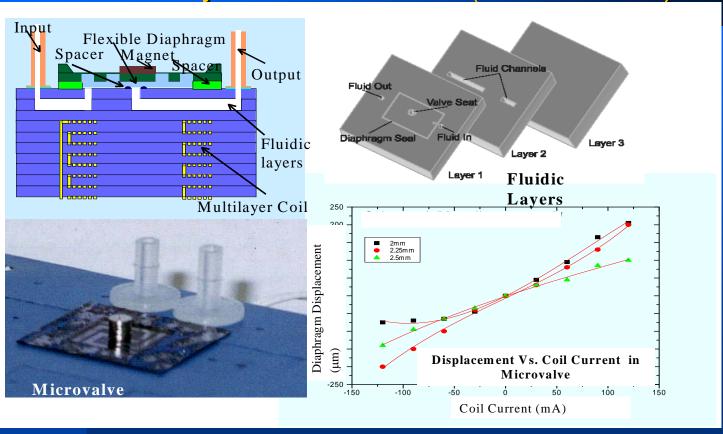

# MICROVALVULAS TERMOPNEUMÁTICAS

# MI CROVALVULA HÍ BRI DA USANDO LTCC

LTCC Meso-System Technology

# LTCC Hybrid Actuators (Microvalve)

**IPT**

In: Gongora-Rubio M.R., Santiago-Aviles J.J. et al., SPIE (1.999), v.3877. p.230 - 239

# MI CRO-QUÍ MI CA

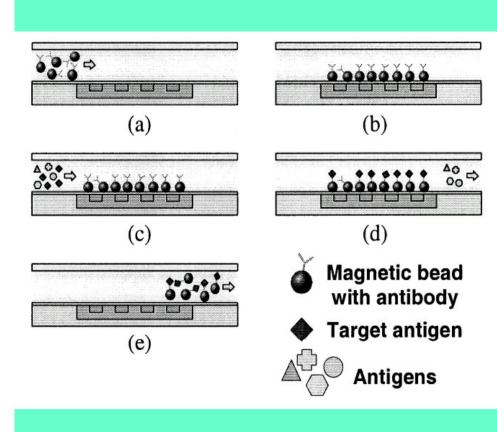

# **BIO-SEPARAÇÃO**

#### **MICROREATORES**

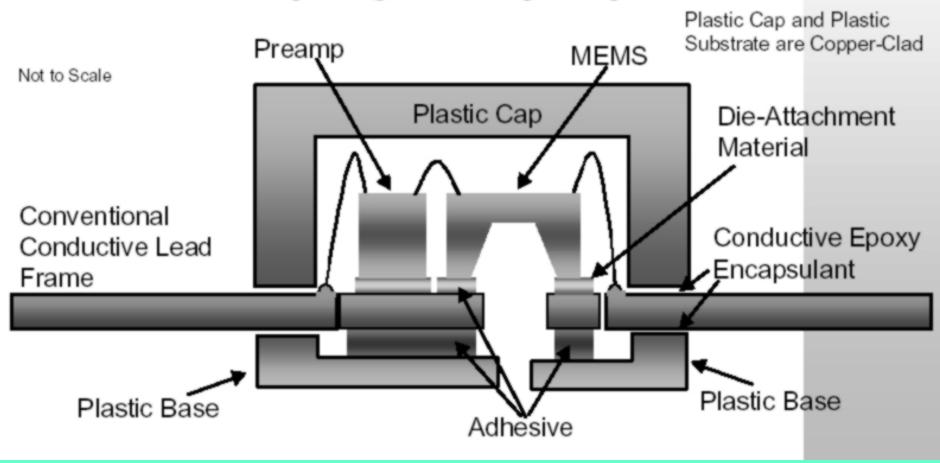

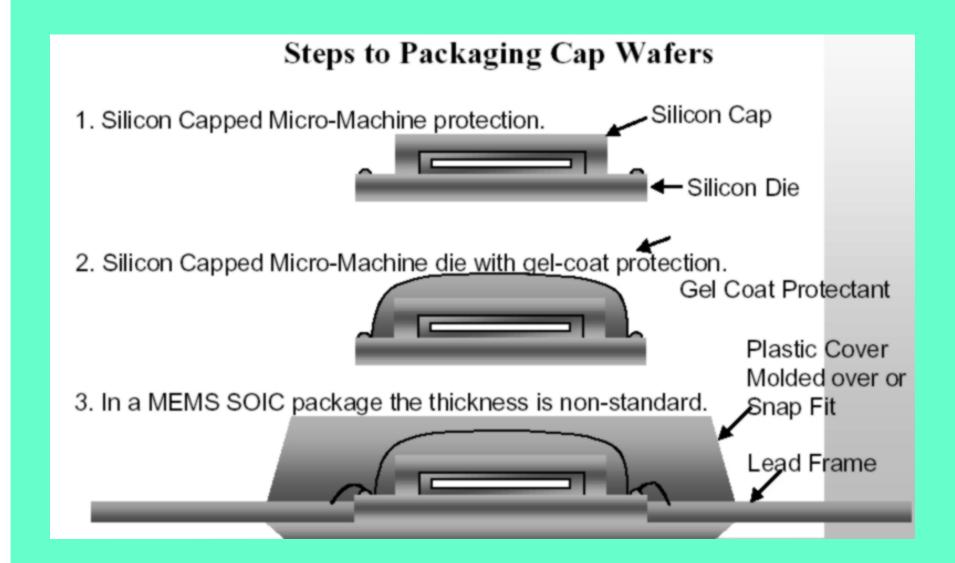

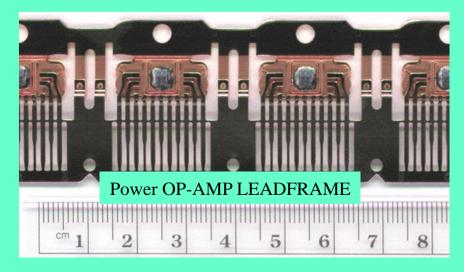

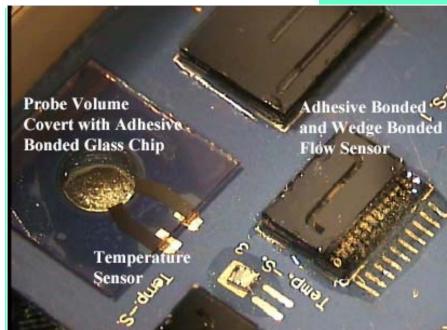

#### ENCAPSULAMENTO MEMS USANDO LEAD FRAMES

Cross-Section of MEMS Acoustic Sensor packaged with a preamp die.

#### ENCAPSULAMENTO SMD PARA MEMS

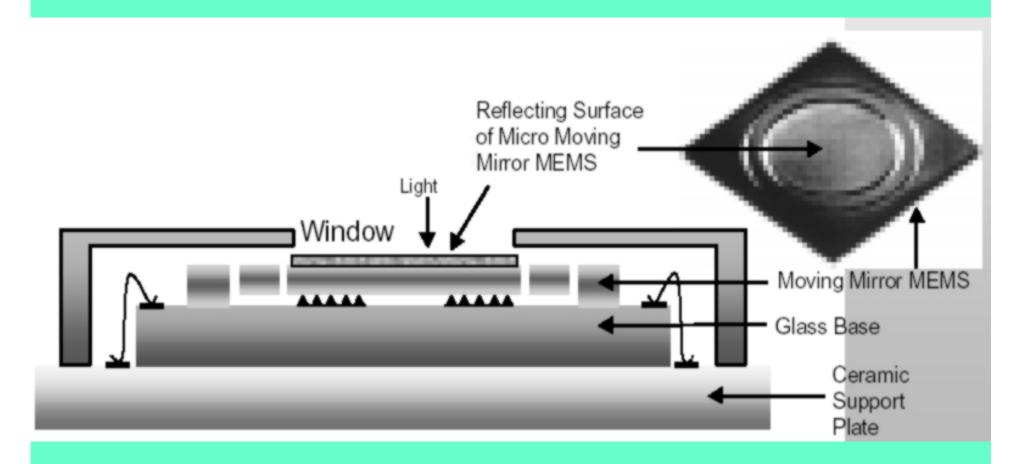

# ENCAPSULAMENTO CERÂMICO PARA MEMS

• Encapsulamento de Micro espelho móvel para aplicações espaciais

#### "MEMS PACKAGING"

- O propósito do encapsulamento ou "Packaging" em Micro-eletrônica é :

- Fornecer suporte mecânico,

- Inter-conexão elétrica,

- Gerenciamento de calor

- Proteção aos Circuitos Integrados "IC's" em relação a fontes de interferência mecânicas e ambientais.

- No caso de "MEMS/MST":

- O encapsulamento deve cumprir todas as funções anteriores com requerimentos adicionais de:

- Proteção ambiental contra eletrólitos e umidade e ao mesmo tempo permitir a interação com o meio ambiente para realizar as funções de sensoriamento e atuação com os diversos domínios de energia atuantes em condições mais severas de operação;

- Proteção mecânica adequada para garantir a integridade estrutural do dispositivo;

- Isolação térmica, ótica e química para evitar efeitos indesejados;

- Bio-compatibilidade e esterilização do dispositivo.

- Em geral os custos associados aos encapsulamentos de micro-sistemas representam parte significativa do custo total de fabricação.

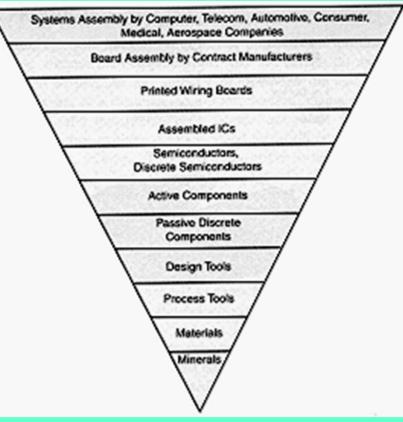

# EMCAPSULAMENTO ELETRÔNI CO (PACKAGI NG)

- Define-se como a Tecnologia de Interconexão de Componentes Eletrônicos. Esta tecnologia permite definir e controlar o ambiente operacional dos arranjos com o objetivo de cumprir especificações em termos de:

- 1. Desempenho

- 2. Confiabilidade

- 3. Velocidade

- 4. Tamanho

- 5. Custo

- 6. Outros

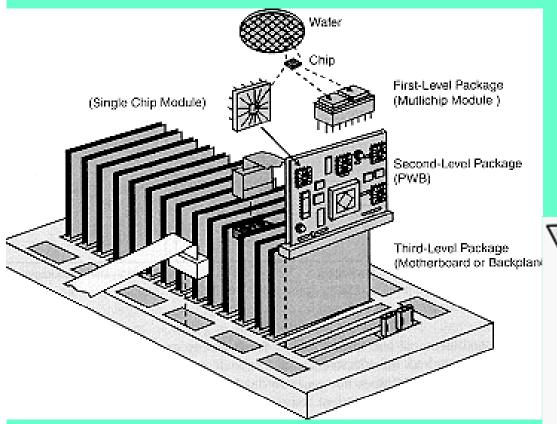

# HIERARQUIA DO ENCAPSULAMENTO ELETRÔNICO

- Nível 0

- "Dies" (Circuitos integrados)

- Nível 1

- A nível de "CHIP"

- Nível 2

- A nível de Circuito impresso

- Nível 3

- A nível de arranjo de C. Impresso

- Nível 4

- A nível de Sistema

# HIERARQUIA NO ENCAPSULAMENTO ELETRÔNICO

#### HIERARQUIA PARA "MEMS PACKAGING"

- Propõe-se uma hierarquia para microsistemas assim:

- Nível do "Die"

- Envolve passivação, isolação, colagem e interconexão elétrica "Wire Bonding" dos diversos sensores e atuadores do microsistema

- Nível do Dispositivo

- Envolve fornecimento de energia , transdução de sinais (entrada/ saída) e interconexões elétricas e colagem dos diversos componentes

- Nível do Sistema

- Envolve quatro tarefas importantes de engenharia:

- Projeto do encapsulamento

- Fabricação do encapsulamento

- Montagem do micro-sistema

- Inspeção e Testes do micro-sistema

#### NECESSIDADES DE UM ENCAPSULAMENTO ELETRÔNICO

#### 1. VELOCIDADE

- 1. Velocidade de Propagação (Chip-Chip) alta (Retardos Baixos)

- 2. Largura de banda elevada (Freqüência. de trabalho elevada)

# 2. NUMERO DE PINOS E "WIREABILITY"

- 1. Alto Nº. de Pinos de I/O por Chip

- 2. Alto Nº. de Conexões de I/O entre 1º e 2º Nível

- 3. Grande Nº. de Conexões

#### 3. TAMANHO

1. Tamanhos Compactos

#### 4. RUÍDO

- 1. Linhas de Transmissão de qualidade (Zo alto e R baixo)

- 2. Baixo "Cross Talk"

- 3. Distribuição de energia com (L alto e R baixo)

- 4. Evitar "spikes" de ligação e ter baixas quedas IR

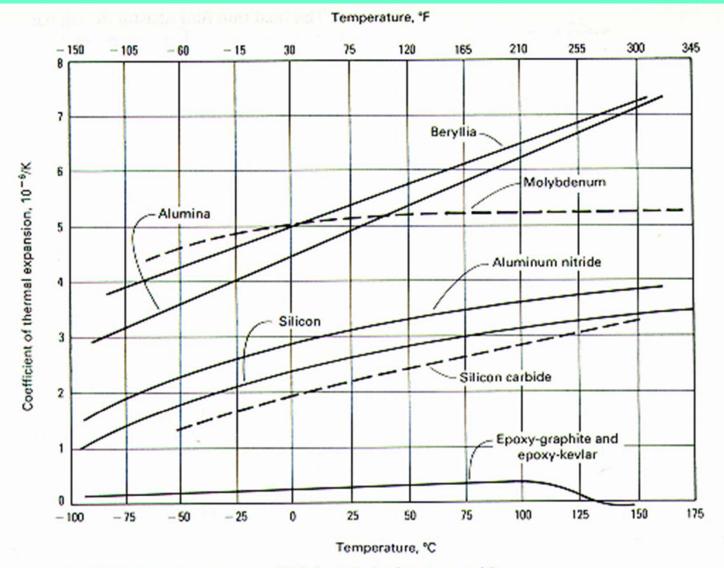

# 5. CARACTERÍSTICAS TÉRMICAS E MECÂNICAS

- 1. Alta remoção de Calor

- 2. Acoplamento dos Coeficientes de Expansão Térmica entre "Dice" e "Chip Carrier"

- 3. Resistência a vibrações e Stress Mecânico

#### 6. FACILIDADE DE MANUFATURA

- 1. Fáceis de Fabricar e Testar

- 2. Fáceis de Modificar e Consertar

- 7. ALTA CONFIABILIDADE

- 8. BAIXO CUSTO

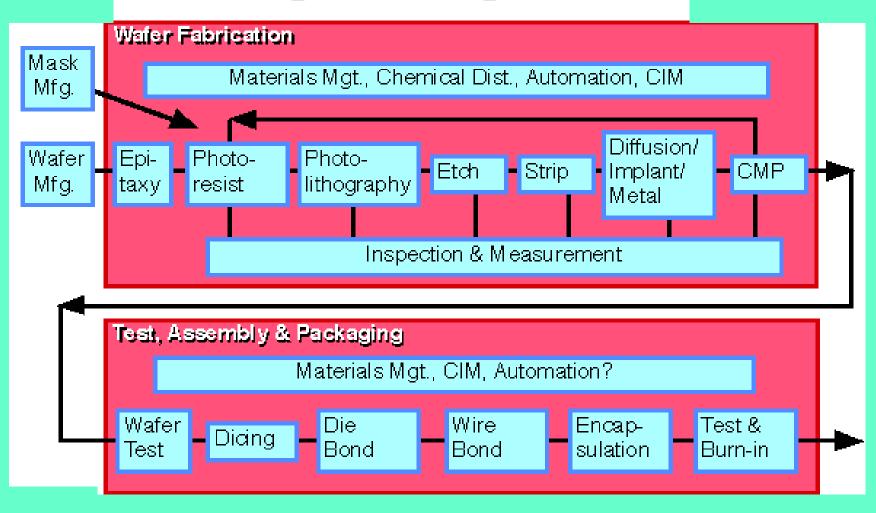

# PROCESSO DE FABRICAÇÃO DE CIRCUITOS INTEGRADOS

# The Chip-Making Process

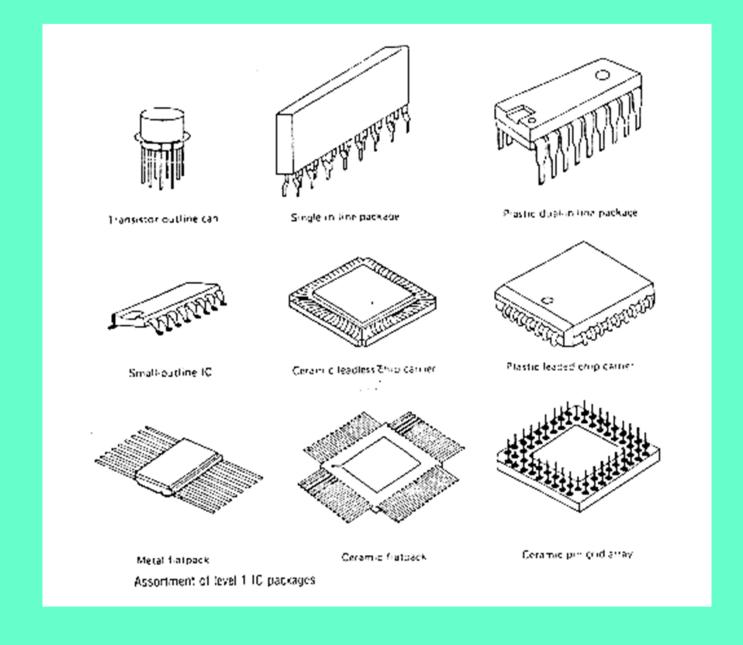

# ENCAPSULAMENTOS TÍPICOS

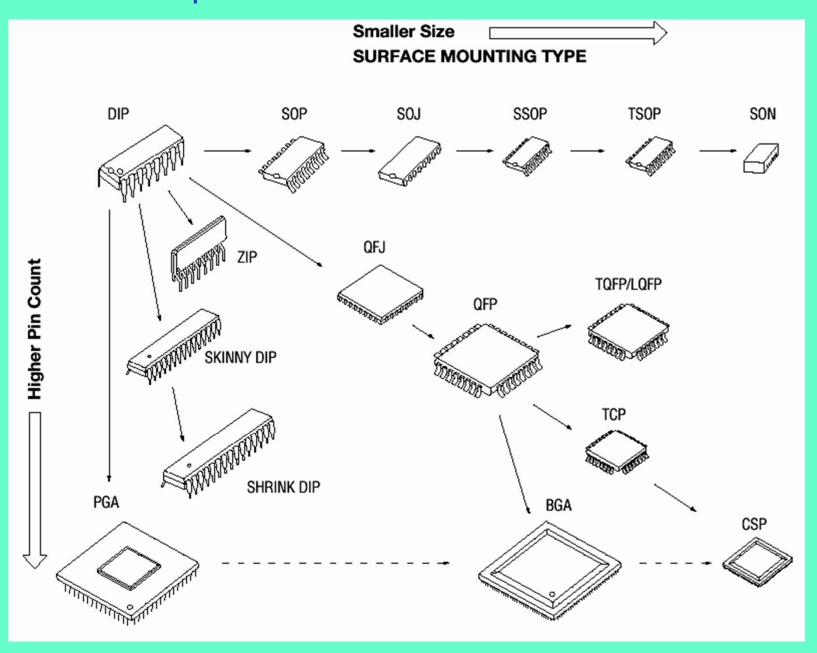

# TENDÊNCIAS para ENCAPSULAMENTOS DISCRETOS

# FUNÇÕES BÁSICAS DAS INTER-CONEXÕES ELÉTRICAS EM SISTEMAS ELETRÔNICOS

- 1. Permitir intercâmbio de informações em todos os níveis de Encapsulamento

- 2. Fornecer em todos níveis energia para o funcionamento adequado do sistema

- 3. Permitir outros tipos de interconexões com o meio ambiente, através de sensores e atuadores, para o encapsulamento de MEMS ou Micro-sistemas

# FATORES MECÂNICOS, ELÉTRICOS, TÉRMICOS E AMBIENTAIS

• Estes fatores são de grande importância, já que afetam diretamente a confiabilidade de um encapsulamento diminuindo muito sua vida útil:

- 1. Fatores Mecânicos

- 1. Tensões de origem Mecânica

- 2. Tensões de origem Térmica

- 2. Fatores Térmicos

- 1. Controle Térmico

- 2. Indução de tensões

- 3. Fatores Elétricos

- 1. Velocidade

- 2. Ruído

- 3. Qualidade de Interconexões

- 4. Distribuição de Energia

- 4. Fatores Ambientais

- 1. Proteção do encapsulamento contra ambientes externos hostis

## CONTROLE TÉRMICO DOS ENCAPSULAMENTOS

#### • OBJETIVOS:

- Manter as temperatura das junções de todos os componentes abaixo dos níveis máximos permitidos

- Administrar a diferença de temperatura de junção entre componentes

- Administrar diferenças de temperatura entre membros estruturais do arranjo

- Quando implementada corretamente, uma boa administração térmica pode:

- Estender a vida dos componentes além da vida projetada.

- Manter a operação do dispositivo sem flutuações induzidas por temperatura excessiva.

- Aumentar as velocidades de chaveamento já que a temperatura de operação é reduzida nos dispositivos semicondutores.

- Aumentar a eficiência térmica dos componentes passivos.

# ADMINISTRAÇÃO TÉRMICA nos ENCAPSULAMENTOS

- O processo de administração térmica pode ser dividido em três fases principais:

- Transferência de calor dentro do encapsulamento do componente semicondutor.

- Transferência de calor do encapsulamento até o dissipador de calor.

- Transferência de calor desde o dissipador de calor até o meio ambiente.

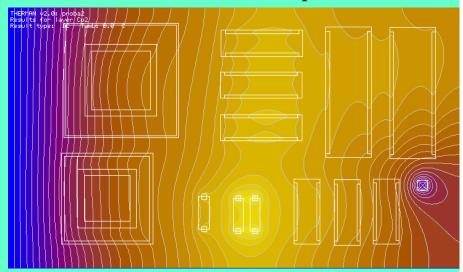

## MODELAGEM TÉRMICA EM ENCAPSULAMENTOS

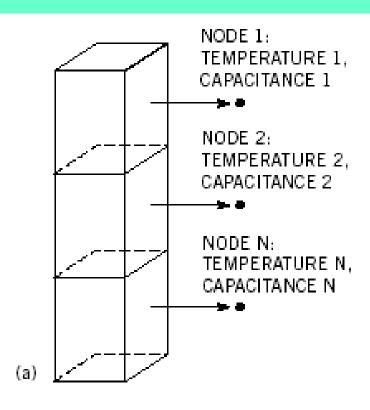

• Uma forma de modelar termicamente circuitos integrados ou dispositivos MEMS é quebrar os objetos em nós que possuem uma temperatura e uma massa térmica ou capacitância térmica (a). Condutores (G = 1/R) no circuito térmico representam os caminhos de fluxo térmico entre os nós (b), após esta modelagem simulação usando SPICE pode ser realizada para obter mapas térmicos no circuito ou dispositivo.

# TENSÕES DE ORIGEM TÉRMICA EM EMPACOTAMENTOS ELETRÔNICOS

- Estas tensões de origem térmica induzem falhas nos diversos arranjos eletrônicos e apresentam as seguintes causas:

- Deformações termoelásticas devidas a mudanças uniformes de Temperatura

- 2. Campos de tensões resultantes devido a variações elevadas de Temperatura ou deslocamentos

- 3. Tensões Elásticas ou Elastoplásticas devidas a choques térmicos, tensões de ruptura ou fadiga térmica

- 4. Problemas associados à materiais frágeis

- Os diversos tipos de falhas associadas a tensões termicamente induzidas são:

- Falha nas junções dos transistores

- Deformações elásticas ou plásticas excessivas

- Falha de ruptura dúctil

- Falha de ruptura frágil

- Falha de fadiga

- Falha de "Creep"

- Falha devida a choque térmico

- Falha devida a tensões de Corrosão

- Falha devida a fadiga térmica

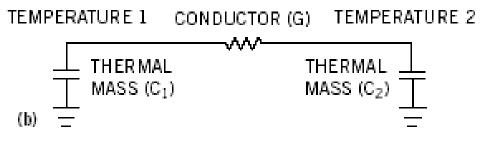

# (CET) DE MATERIAIS USADOS EM "PACKAGING"

| APLI CAÇÃO               | MATERI AL                                                                  | COEFICIENTE DE<br>EXPANSÃO TÉRMICA<br>PPM x(°C-1) |

|--------------------------|----------------------------------------------------------------------------|---------------------------------------------------|

| Substrato de CI          | Silício<br>Arseneto de Gálio                                               | 2, 6<br>5, 7                                      |

| Pi nos                   | Cobre<br>Ligas de Ni-Fe (Liga<br>42)                                       | 16, 3-18<br>4, 1-6                                |

| Suportes de<br>Substrato | Al umi na (99%)<br>A <sub>I</sub> N<br>BeO (99, 5%)                        | 6, 7<br>4, 1<br>6, 7                              |

| Adesi vos                | Au-Si (Liga Eutética)<br>Pb-Sn (Solda)<br>Epóxi com Prata<br>RTV- Silicone | 14, 2<br>24, 7<br>32<br>300-800                   |

| Camadas<br>Conformadoras | Polimida<br>Silicone RTV<br>Silica Gel                                     | 40-50<br>300-800<br>300                           |

| Compostos<br>Moldáveis   | Epóxi<br>Epóxi com Prata                                                   | 60-80<br>12-24                                    |

# (CET) DE SUBSTRATOS

Fig. 9 Coefficient of thermal expansion (CTE) for typical substrate materials

# CONDUTI VI DADE TÉRMI CA EM SUBSTRATOS

Fig. 8 Thermal conductivities for typical substrate materials

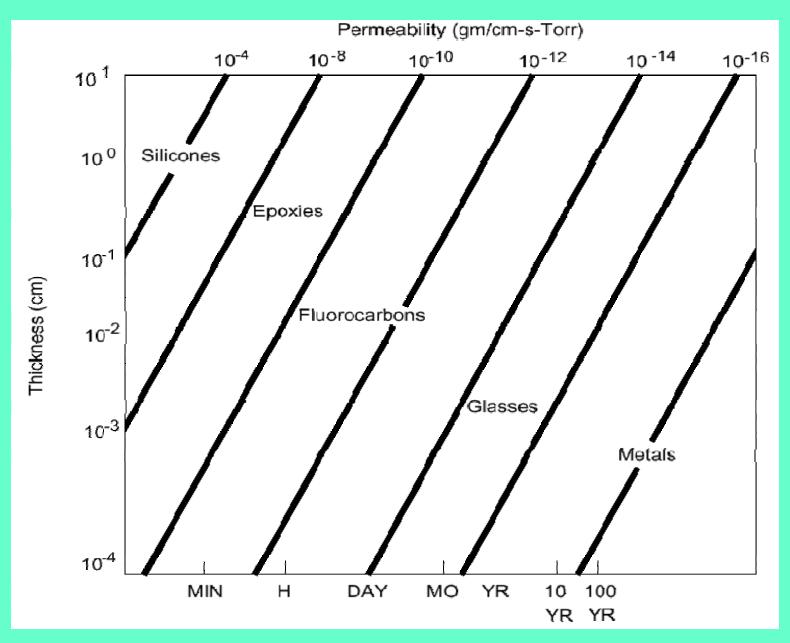

## HERMETICIDADE RELATIVA DE MATERIAIS

#### MECANISMOS DE FALHA EM MEMS

- Os mecanismos associados a "MEMS" e Micro-sistemas são diferentes dos normalmente associados a microeletrônica, apresentando mecanismos de falha diversos aos relacionados com as juntas de solda como:

- Falhas por desgaste;

- Falhas por esticção ( adesão de duas superfícies muito próximas);

- Falhas por delaminação de filmes ou camadas;

- Falhas ambientais (ciclos térmicos, vibração, choque, umidade, corrosão e efeitos de radiações incidentes);

- Ciclos de Fadiga termicamente induzidos;

- Amortecimento de micro-estruturas mecânicas.

#### MECANISMOS DE FALHA EM MEMS

#### MECANISMOS DE FALHA EM MICROSSISTEMAS Mecanismos de sobretensão Mecanismos de Desgaste Mecânicos Químicos Elétrica Elétricos Mecânica **EMI** Fadiga Fratura Frágil **ESD** Fluência Formação de Corrosão aglomerados (Creep) Deformação Radiação Cravação e Difusão Desgaste junções Plástica Delaminação Delaminação Eletromigração Ruptura Crescimento Interfacial interfacial dendritico Derretimento de interconexões

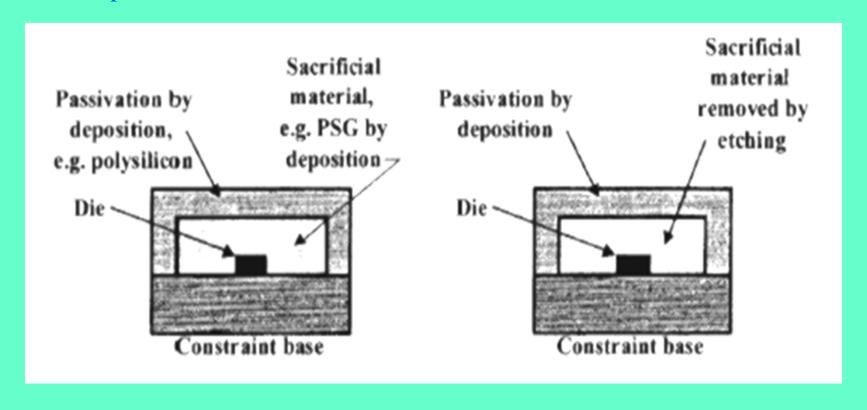

# ENCAPSULAMENTO A NÍVEL DE "DIE" PASSIVAÇÃO DO "DIE"

- Os encapsulamentos de MEMS

freqüentemente estão em contato com

meios agressivos, assim torna-se

necessário sua proteção através de

camadas de passivação como:

- Deposição conforme de camadas de 2 ou 3 μm de substâncias orgânicas como Parylene (material Biocompatível) usando LPCVD em baixas temperaturas.

- Apresenta problemas de mudanças das características dinâmicas do dispositivo sensor ou atuador

- Cobertura da superfície do DIE com substâncias moles como Gel de Silicone

- Apresenta problemas de endurecimento com o tempo

# PASSI VAÇÃO DO "DIE" (Cont.)

- Uso de coberturas externas plásticas, com aberturas para passagens de sinal ou energia.

- Passivação de estruturas com micro-usinagem superficial com camadas de sacrifício (PSG) e de passivação (Si-Poly) usando LPCVD em baixa temperatura.

# I SOLAÇÃO DO "DIE"

- Trata-se da isolação do dispositivo de outras fontes de energia que podem interagir, perturbar e produzir interferências nos sensores ou atuadores do dispositivo em questão.

- Existem diversas tipos de isolação nos diversos domínios de energia mas distinguem-se os métodos mecânicos e eletromagnéticos.

- Métodos de Isolação Mecânicos:

- Compensações de problemas devidos ao CET dos materiais

- Modificação de caminhos térmicos

- Amortecimentos por mudança da razão de aspecto das estruturas

- Uso de estruturas diferenciais, de razão ou servo-estruturas

- Métodos de Isolação Eletromagnéticos:

- Gaiolas de Faraday

- Aterramentos adequados

- Codificação de sinais

- Uso de estruturas diferenciais

# ISOLAÇÃO MECÂNICA DE DISPOSITIVOS MEMS

#### SOLDAGEM OU COLAGEM DE "DIES"

- Soldagem Anódica

- Soldagem por Fusão

- Soldagem Eutética

- Soldagem com Vidro

- Soldagem com Polímeros

- Soldagem com Solda tipo "Soft"

- Outros Métodos:

- Prensagem

- Termo-compressão metálica

- Soldagem Ultra sônica

- Soldagem por LASER

## PRINCIPAIS TÉCNICAS DE COLAGEM EM SILÍCIO

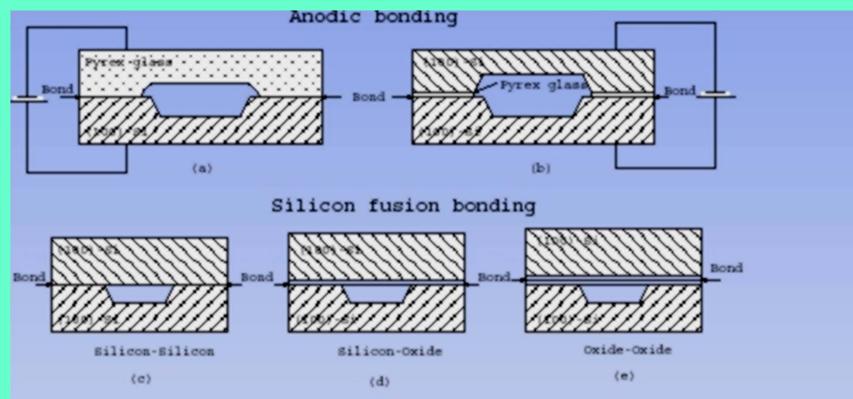

Cross-sectional views of two wafer bonding techniques.

- (a) Anodic bonding of a glass wafer to a silicon wafer.

- (b) Anodic bonding of a silicon wafer with deposited glass layer to a silicon wafer

- (c) Fusion bonding of two silicon wafers without silicondioxide layers.

- (d) Fusion bonding of two silicon wafers where one of the wafers has a layer SiO2

- (e) Fusion bonding of two silicon wafers with silicondioxide layers.

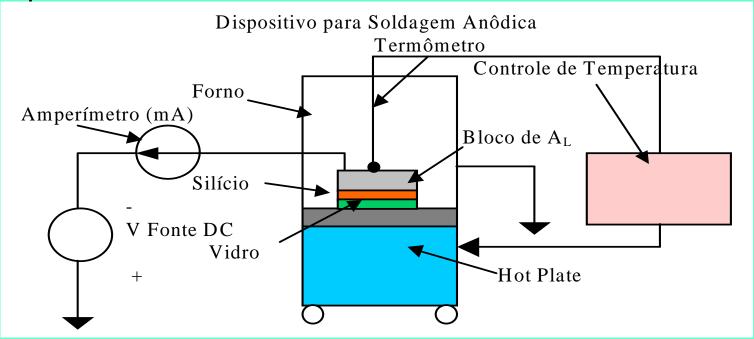

## SOLDAGEM ANÓDICA

- Permite a soldagem de substratos de silício com substratos de vidro

- Ao parâmetros críticos do processo são:

- Limpeza das superfícies

- Amplitude e duração da tensão aplicada

- Temperatura e área da região soldada

- A tensão aplicada varia de 400-1000V dependendo dos materiais e da temperatura.

- A Temperatura varia de 200-500 °C

## Mecanismo da Soldagem Anódica

- Considera-se como um processo eletro-químico

- Em temperaturas elevadas, a mobilidade de íons positivos de sódio presentes no vidro é elevada

- A presença do campo elétrico externo causa a migração dos ions para o catodo negativamente carregado, na superfície posterior do substrato de vidro

- A migração dos íons Na<sup>+</sup> deixa para trás íons negativos. Esses íons negativos formam uma região de depleção (camada de carga espacial) adjacente à superfície de silício (com largura da ordem de 1 μm), o que dá origem a um forte campo elétrico interno na interface silício-vidro.

- Como resultado do campo elétrico interno fortes forças de origem eletrostática geram pressões da ordem de varias atmosferas, colocando o silício e vidro em contato intimo.

- A medida de corrente que flui pelo circuito elétrico é um bom indicador sobre o andamento do processo

# SOLDAGEM POR FUSÃO (DWB-DIRECT WAFER BONDING)

- Consiste na fusão de superfícies de Silício, superfícies com filmes de óxido de silício ou outros materiais

- Mecanismos de soldagem de superfícies com dióxido de silício (SiO<sub>2</sub>//SiO<sub>2</sub>)

- A conversão em óxido de silício do oxigênio presente entre as lâminas cria um vácuo parcial, que coloca as amostras em contato íntimo

- A superfície de silício termina em ligações incompletas ( Dangling Bonds)

- Estas ligações reagem rapidamente com água (da atmosfera ou incorporada durante o processo de limpeza) formando grupos SiOH

- Quando as amostras são colocadas em contato a temperatura ambiente,

ligações de hidrogênio se desenvolvem entre as superfícies opostas

- Aquecendo-se as amostras quando a temperatura atinge perto de 200°C, mais ligações de hidrogênio são desenvolvidas entre os grupo OH opostos devido a alta mobilidade destes grupos

- À medida que a temperatura aumenta, quando atinge 300 °C os grupos OH opostos interagem formando H₂O e ligações Si-O-Si são formadas ( a água e hidrogênio se difundem para fora da interface).

## MECANISMOS DE SOLDAGEM DE SUPERFÍCIES DE SI

- Na presença de um óxido nativo a superfície é hidrófila. O estado hidrófilo é causado por grupos OH na superfície. Neste caso a soldagem ocorre de forma semelhante ao caso SiO<sub>2</sub>//SiO<sub>2</sub>.

- Superfície hidrófobas podem ser obtidas limpando-se as amostras de silício em solução de HF. O estado hidrófobo é associado principalmente com grupos Si-H, Si-CHx e numa menor extensão com grupos Si-F.

- Acredita-se que forças de Wan der Walls sejam responsáveis pelo fato das amostras ficarem em contato íntimo.

- Aquecendo-se a amostra os grupos OH disponíveis contribuem para a atração entre as amostras, a 200 °C tem inicio a desidratação de grupos OH e as ligações de hidrogênio são substituídas por ligações Si-O-Si

- A 400°C tem início a desidratação dos grupos Si-H e ligações covalentes Si-Si muito fortes são formadas.

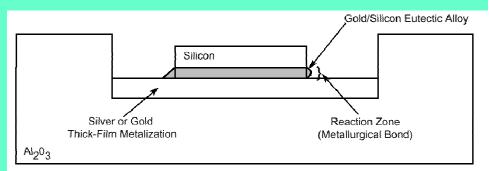

## MÉTODO da COLAGEM ou SOLDA EUTÊTICA

#### •Solda Eutêtica:

- "Die attach" Eutêtico: Com este método não é necessário colocar nenhum adesivo no substrato.

- Isto é feito aquecendo a metalização do substrato, que colocada na metalização da parte inferior do "Die" formando uma cola intermetálica.

- •A Colocação usando Solda Eutêtica permite:

- -Ser usado em aplicações Militares e aero-espaciais

- -Ser usado em sistemas MCM de multi-camadas Cerâmicos

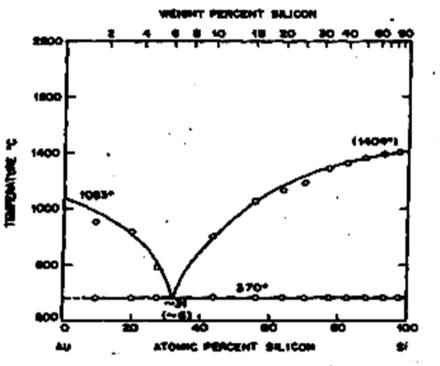

- –Usa a liga mais popular: Au-Si

Phase diagram for the gold-silicon system. (From Hansen.)

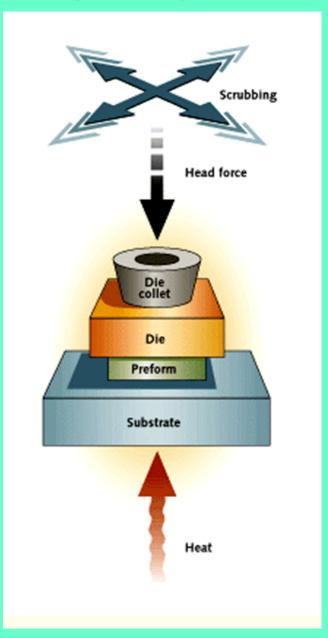

## TÉCNICA da COLAGEM EUTÊTICA

- Aquecimento do Substrato @ 425 °C

- Aplicação de força e esfregada de "Die"

- O Si se difunde no Au até atingir a composição eutêtica e a fusão começa

- Uma frente líquida avança no Au e o Si continua difundindo-se

- Obtém-se então a soldagem completa

- É necessário prevenir a oxidação superficial do Si, de forma que é desejável realizar esta soldagem em ambiente de N<sub>2</sub>

- É necessário realizar uma excelente limpeza da superfície do Si, para a retirada do oxido nativo

- A espessura mínima de A<sub>u</sub> necessária para realizar a solda é de 150 nm

## USO de PRE-FORMAS

- USO DE PRE-FORMAS (A<sub>u</sub>-2S<sub>i</sub>) PARA POUPAR A<sub>u</sub>

- Utiliza-se uma pré-forma que encontra-se perto da composição eutêtica

- A solda realiza-se de forma mais rápida

- A difusão do Si é menor

- A soldagem desta forma exige camadas de Au de somente 10 nm

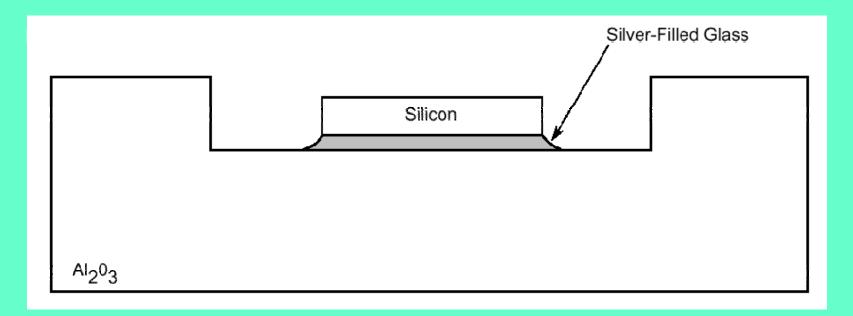

#### COLAGEM de "DIES" USANDO VIDRO

#### • COLAGEM USANDO FILMES DE VIDRO

- Muitos encapsulamentos usam vidro que são mais baratos

- O vidro pode ser fundido a temperaturas maiores que 500 °C e o "DIE" colocado

- Alguns tipos de vidro tem coeficientes de expansão térmica similares ao silício

- Os filmes podem ser depositados usando técnicas de:

#### Espirramento Catódico (Sputtering)

- As superfícies não podem ser muito rugosas ou contaminadas

- Usando fosforosilicatos a solda ocorre a 1000 °C com boa resistência mecânica

- Usando Borosilicatos a solda ocorre a 450 °C com boa resistência mecânica

#### Serigrafia

- Utiliza fritas de óxidos inorgânicos de Boro e Chumbo que misturadas com veículos orgânicos formam uma pasta adequada para serigrafia

- Após a deposição cura-se a pasta retirando-se o veículo orgânico, alinhando-se a estrutura e sob pressão realiza-se a cura a temperaturas maiores de 500 °C

#### COLAGEM USANDO VIDRO-PRATA

- Método de baixo custo

- O sistema é de uma pasta de 81% de Ag carregado com vidro numa matriz orgânica

- Usa-se "Dipping" ou serigrafia para a deposição

- Coloca-se o "DIE" @ T ambiente

- Cura-se @ 375 oC no ar

### SOLDAGEM DE "DIES" USANDO POLÍMEROS

- Este processo é muito usado atualmente devido ao desempenho dos materiais usados desde o ponto de vista de parâmetros do processo como tempo de Cura, tempo de ciclo e qualidade geral.

- Se usam para encapsulamentos do tipo: BGAs, quad flat packs (QFPs), plastic leaded chip carriers (PLCCs) e SOICs.

- Método de baixo custo

- Usam-se Poliimidas com Ag e "Epoxies"

- As temperaturas de cura são de aprox. 130 °C no ar

- Usa-se "Dipping" ou serigrafia para a deposição

- Em altas temperaturas estes materiais degradam-se

- Em ambientes úmidos estes materiais degradam-se

#### SOLDAGEM DE "DIES" USANDO SOLDA

#### • "Die Attach" com solda "Soft":

- É um processo eutêtico onde se introduze a solda para obter a colagem.

- Utiliza-se solda tipo "SOFT" 95 Pb 5 Sn

- A solda é introduzida através de pré-formas ou usando "dispensing" automático.

- É necessária uma camada de adesão

- O processo requer uma rampa de aquecimento e desaquecimento muito maior que a colagem eutêtica sem solda, porem a solda deve ser realizada rapidamente para não ultrapassar os limites de potência máximos do "Die".

- Deve ser usada atmosfera redutora para evitar oxidação nas molduras.

- Componentes fabricados com este método são usados em aplicações automotivas e dispositivos de alta potência.

## ENCAPSULAMENTO A NÍVEL DO DISPOSITIVO

- Transdução de Sinais

- Técnicas de Instrumentação eletrônica são usadas tipicamente

- Interconexão Elétrica

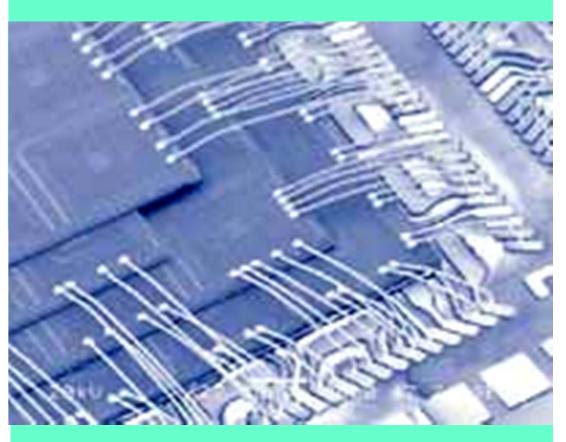

- WB "WIRE BONDING"

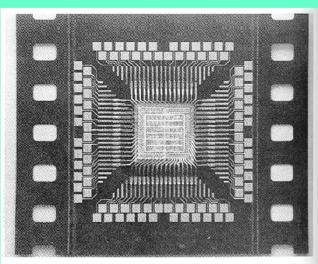

- TAB "TAPE AUTOMATED BONDING"

- FC "FLIP CHIP" e BGA "BALL GRID ARRAY"

- COB "CHIP on BOARD"

- Soldagem ou Colagem de Dispositivos

- Soldagem por Fusão

- Soldagem Anódica

- Soldagem Eutética

- Soldagem com Vidro

- Soldagem com Solda tipo "Soft"

# ENCAPSULAMENTO A NÍVEL DE CHIP

## TÉCNICAS DE INTERCONEXÃO ELÉTRICA

- WB "Wire Bonding"

- TAB "Tape Automated Bonding"

- CHIP on BOARD

- FLIP CHIP

# CARACTERÍSTICAS do "WIRE BONDING"

Table 1-1. Three wirebonding processes.

| Wirebonding       | Pressure | Temperature | Ultrasonic energy | Wire   | Pad    |

|-------------------|----------|-------------|-------------------|--------|--------|

| Thermocompression | High     | 300-500 °C  | No Au,            |        | Al, Au |

| Ultrasonic        | Low      | 25 °C       | Yes               | Au, Al | Al, Au |

| Thermosonic       | Low      | 100-150 °C  | Yes               | Au     | Al, Au |

Table 1-2. Wirebond formation.

| Wirebond   | Bonding technique | Bonding tool | Wire   | Pad    | Speed              |

|------------|-------------------|--------------|--------|--------|--------------------|

| Ball bond  | T/C, T/S          | Capillary    | Au     | Al, Au | 10 wires/sec (T/S) |

| Wedge bond | T/S, U/S          | Wedge        | Au, Al | AI, Au | 4 wires/sec        |

Wedge bond

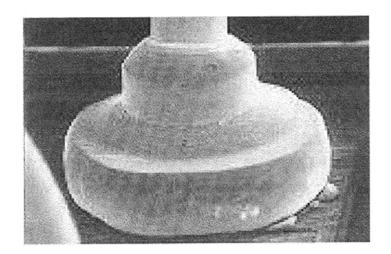

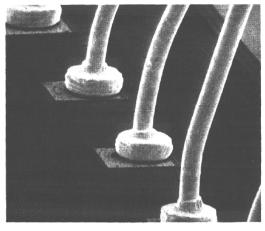

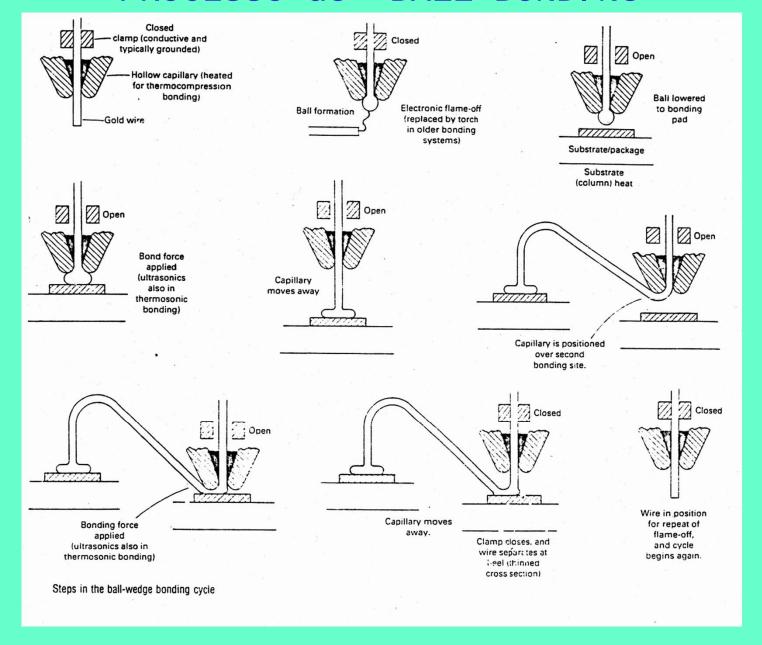

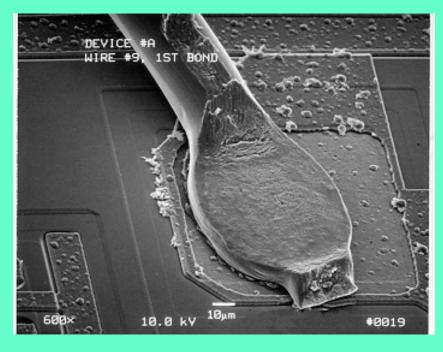

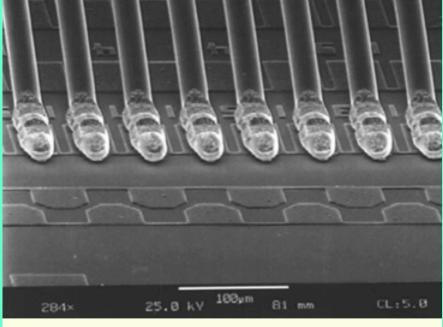

#### "BALL BONDING"

A vantagem do "ball bonding" constitui-se na seção redonda do capilar que permite dobras do fio em qualquer angulo, viabilizando assim o posicionamento do fio em qualquer direção usando-se somente movimentos X-Y. O processo de "ball bonding" consiste na formação de uma primeira solda, tipo bola (ball), no "pad" situado no "die", seguida de uma segunda solda, tipo cunha (wedge), no terminal correspondente do encapsulamento ("leadframe" ou substrato) para formar a conexão elétrica entre o ""Die" e o portador "carrier".

Este processo apresenta diversas etapas e pode ser realizado em 80 mili-segundos.

Bola livre

Primeira Solda

Segunda Solda

## PROCESSO de "BALL BONDING"

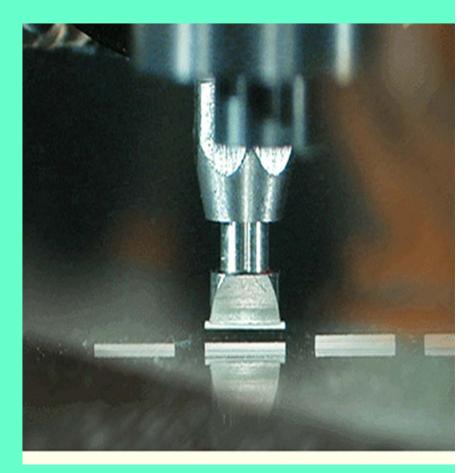

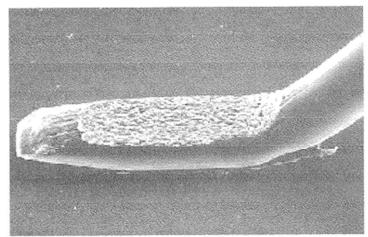

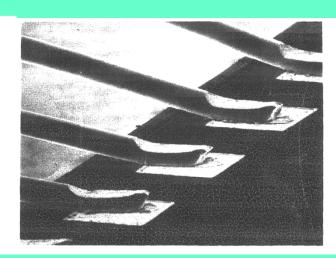

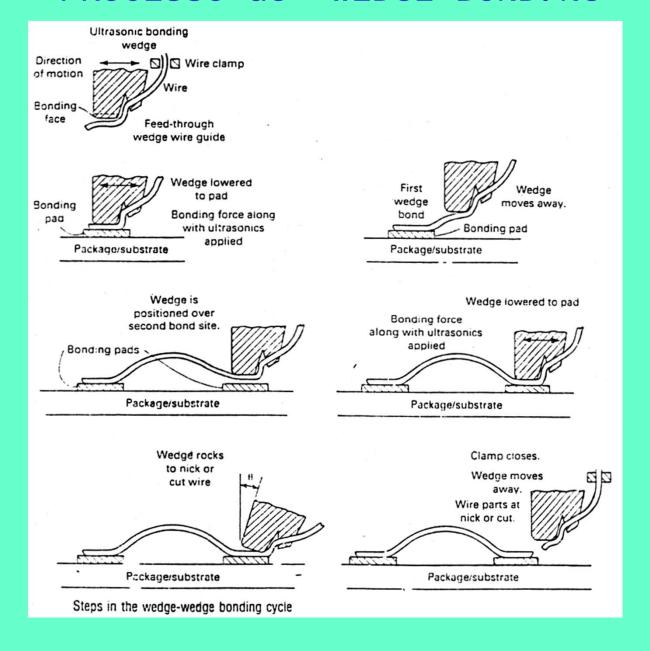

#### "WEDGE BONDING"

Solda tipo "Wedge" sempre permitiu a capacidade de diminuição do "pad pitch", devido a que a solda pode ser realizada deformando o fio com 25 a 30 % além de seu diâmetro original. Comparativamente a formação "ball bond" implica numa deformação de 60 a 80 % de seu diâmetro original. Como a solda é menor, o "pad pitch" pode ser diminuído quando comparado com a técnica de "Ball bonding".

## PROCESSO de "WEDGE BONDING"

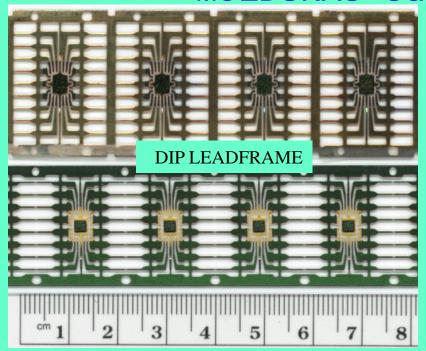

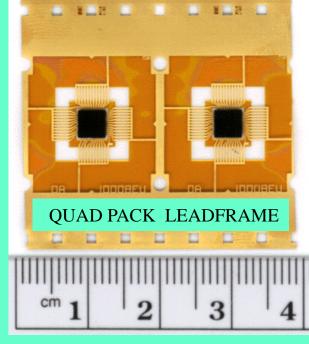

## MOLDURAS ou "LEAD FRAMES"

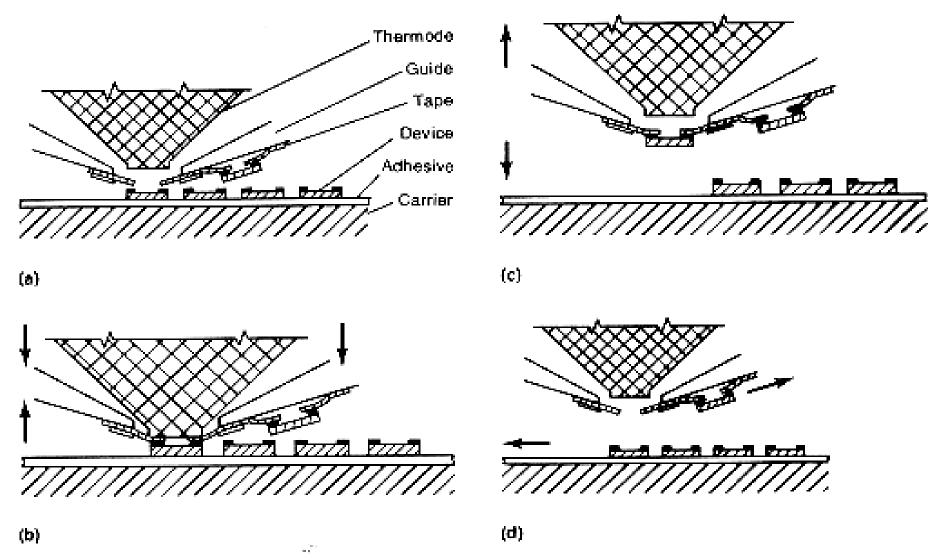

## SOLDAGEM do TERMINAL INTERNO em TAB

Fig. 10 Inner lead bonding sequence. (a) Precision x-y coordinate table. (b) Bonding. (c) Preset bond cycle. (d) Coordinate table indexes to position a new chip. Source: Ref 101-103

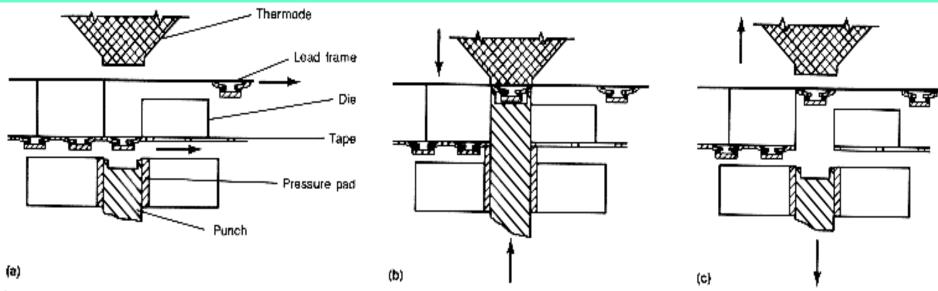

#### SOLDAGEM do TERMINAL EXTERNO em TAB

- Passo1:

- Alimentação do dispositivo

- Passo2:

- Punção, formação de terminais e colagem

- Passo3:

- Retração da ferramenta

Fig. 23 Outer lead bonding sequence. (a) Feed. (b) Punch and bond. (c) Retract. Source: Ref 101-103

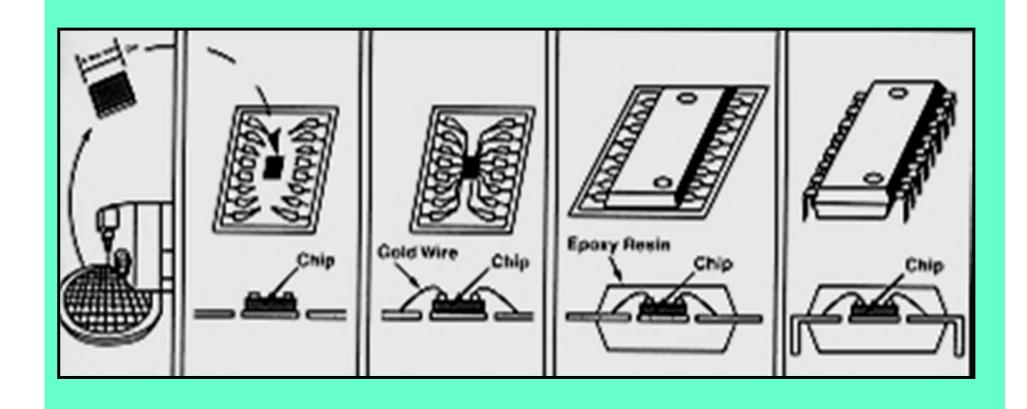

# OUTROS MÉTODOS de ENCAPSULAMENTO "COB" (CHI P ON BOARD)

Substrate, FR4, G10... Die Attach Wire bonding & testing Encapsulation & Testing Surface Mount (SMD) Final test

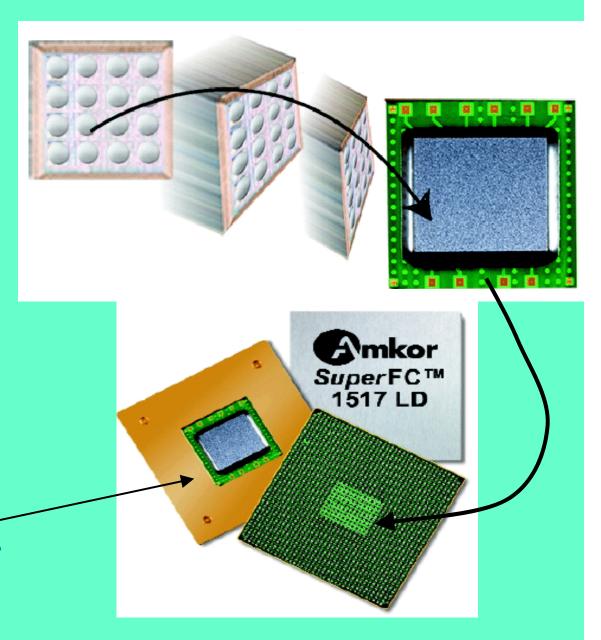

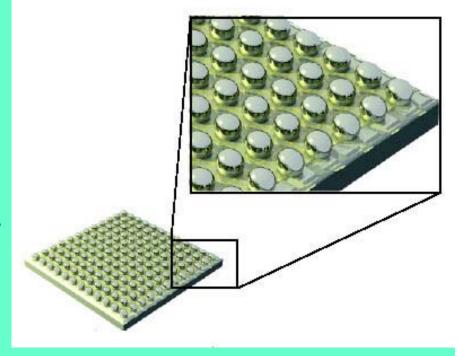

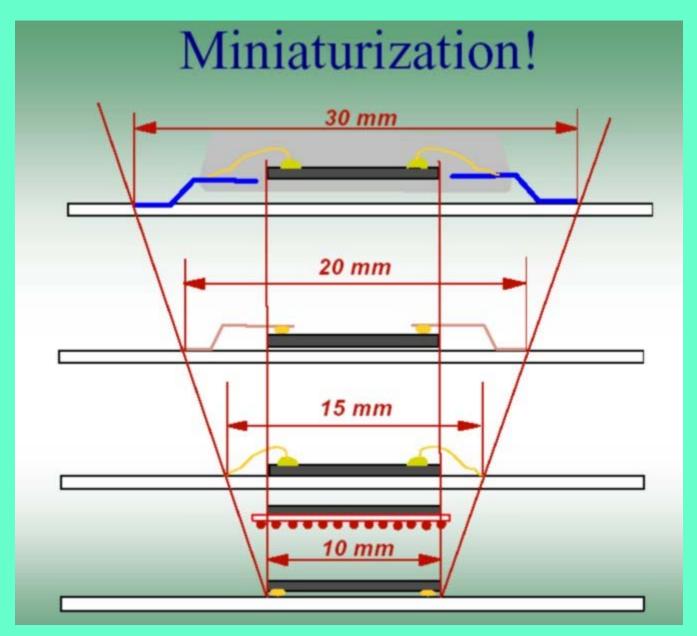

#### TECNOLOGIA FLIP CHIP

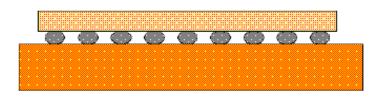

- O comprimento das interconexões entre o Chip e substrato podem ser minimizadas colocando batentes "Bumps" de solda nas ilhas "Pads" do "Die", virando-o, alinhando-o com os "Pads" de contato no substrato e realizando uma refusão de solda para estabelecer a ligação entre "Die" e Substrato.

- Esta técnica hoje permite realizar muitos tipos de encapsulamento como BGA, PGA e CSP

#### TECNOLOGIA FLIP CHIP

#### Vantagens

- Tamanho menor, redução de peso e altura,

- Ganha-se área no silício,

- Aumento de desempenho: fornece baixas indutâncias e capacitâncias parasitas,

- Maior funcionalidade: Aumenta o numero de terminais I/O,

- Aumento de Confiabilidade:

Devido ao uso de "Underfill",

- Facilidade de remoção de calor na parte superior do arranjo,

- Baixo custo.

#### Desvantagens

- Disponibilidade no mercado de "Bumped Chips",

- Inspeção dificultada,

- Compatibilidade fraca com SMT,

- Dificuldade de movimentação de "Dies"

- Necessidade de montagem com alta precisão,

- Tempo de cura longo dos materiais para "Underfilling",

- Re-trabalho ou reparo difícil ou as vezes impossível.

# MOTIVAÇÕES PARA USAR FLIP CHIP

- 1. O desempenho mais alto desde o ponto de vista de velocidade, redução de indutâncias, distribuição de energia, propagação de sinais e isolação de ruídos;

- 2. A maior integração de silício com o maior número de I/O por "Die", pelo uso otimizado da superfície do "Die";

- 3. Utilização crescente do da lâmina. Circuitos integrados projetados em arranjos de área resultam em "Dies" menores e portanto mais "Dies" por Lâmina;

- 4. Pode-se manter as geometrias das pegadas dos "Dies" que reduziram sua área, evitando realizar um novo Lay-out do PCB;

- 5. Maior ergonomia em relação a peso, tamanho e espessura;

- 6. Melhor gerenciamento térmico para sistemas com IC's de alta velocidade e com alto número de I/O;

- 7. Utilização otimizada de maquinário.

# AUMENTO DE MINIATURIZAÇÃO COM FLIP CHIP

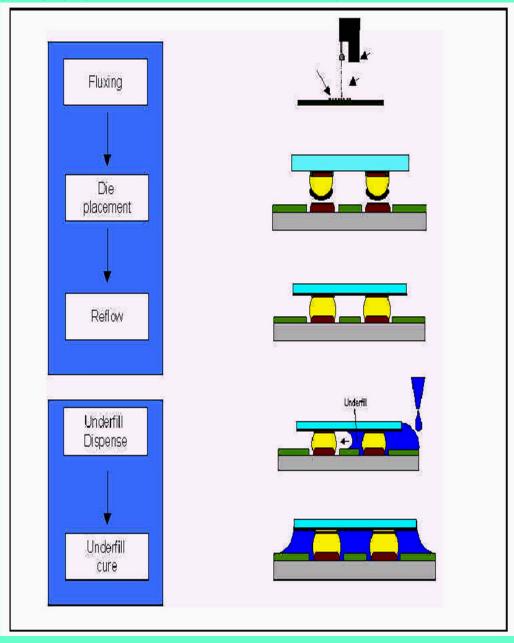

# SEQUÊNCIA DE PROCESSO PARA FLIP CHIP

- Um processo de Flip Chip completo segue os seguintes passos:

- Processo de "Bumping" nas lâminas de Silício

- Corte das lâminas e obtenção de "Dies"

- Colocação em fitas ou bandejas

- Deposição de fundente no substrato

- Posicionamento do "Die"

- Refusão de solda

- Limpeza

- Deposição do "UnderFill"

- Cura do "Underfill"

# PROCESSOS DE DEPOSIÇÃO DOS BATENTES EM FLIP

- São cinco os processos mais usados para fabricar o batente de solda.

- As técnicas de deposição são as seguintes:

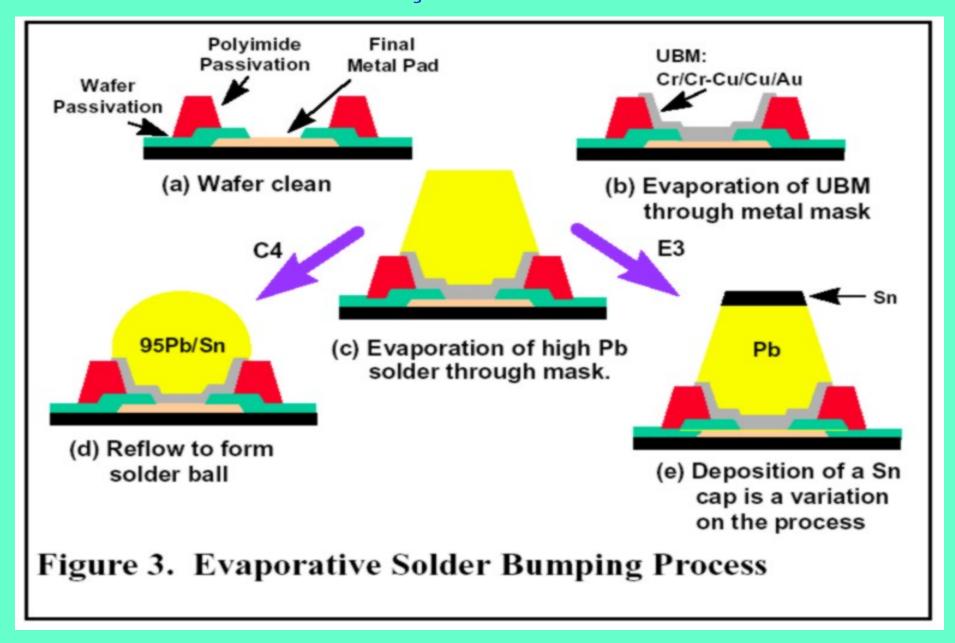

- 1. Formação do batente usando Evaporação;

- 2. Formação do batente usando Eletrodeposição;

- 3. Formação do batente usando Serigrafia;

- 4. UBM de Niquel Electroless seguido de batentes serigrafados ou com adesivos condutivos.

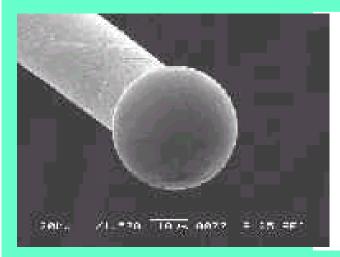

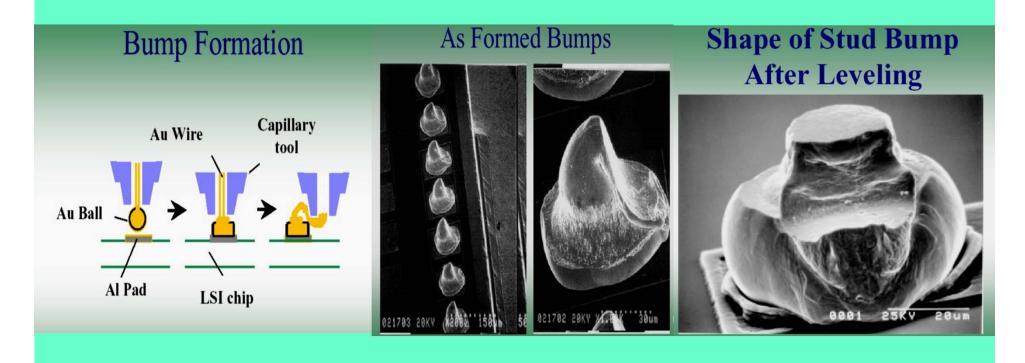

5. Formação do batente usando Bolas de "Wire Bonding" ou "Stud Bump

Bonding";

# PROCESSO C4 EVAPORAÇÃO DE BATENTES OU "BUMPS"

# FORMAÇÃO DO BATENTE "STUD" COM "BALL BONDING"

• Neste caso utiliza-se o processo de "Ball Wire Bonding" para soldar uma bola de Au no metal do C.I. criando assim o batente, que deve ser trabalhado para manter o seu comprimento dentro de valores pré-estabelecidos

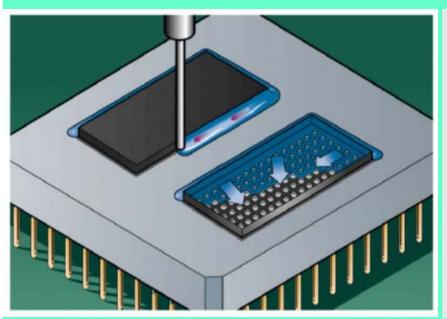

## PROCESSO DE "UNDERFILLING"

flip-chip without underfill-material

flip-chip with underfill

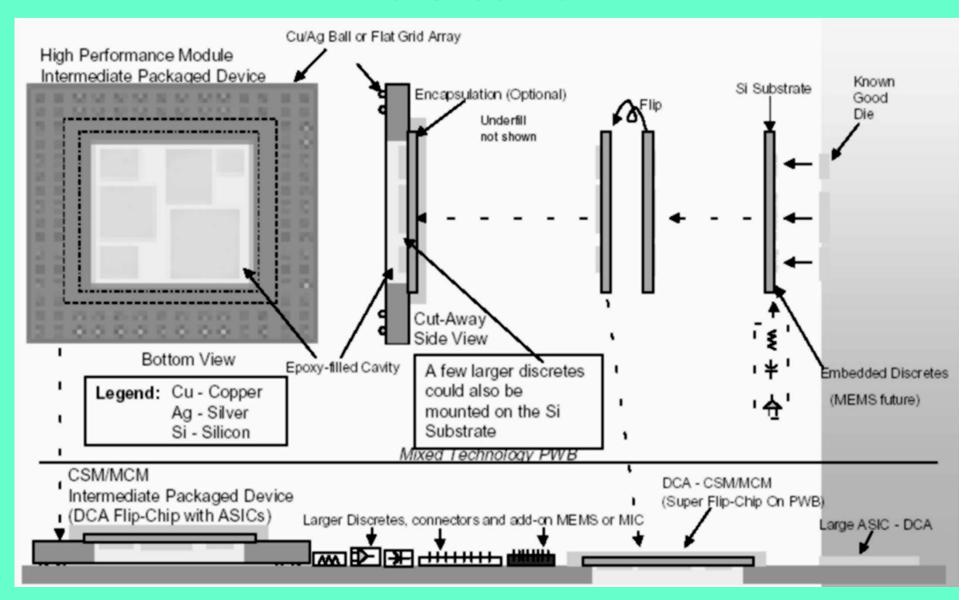

## ENCAPSULAMENTO A NÍVEL DE SISTEMA

#### • Projeto do encapsulamento

Requerem técnicas sofisticadas de analise e simulação para seleção de tecnologias (Ex. Packaging em 2D e 3D) e materiais a serem usados (Plásticos ou cerâmicos)

#### Fabricação dos encapsulamentos

Utilizam-se as técnicas já comentadas, algumas estão disponíveis somente a nível de laboratório

### • Montagem do micro-sistema

- Requerem técnicas robotizadas ou de self-assembling, existem algumas técnicas a nível de protótipo em laboratórios de pesquisa

#### • Inspeção e Testes do micro-sistema

- São necessárias técnicas sofisticadas de inspeção como:

- Raios X

- Microscopia acústica

- Microscopia térmica

- Os testes envolvem medições de parâmetros que dependem da função do micro-sistema

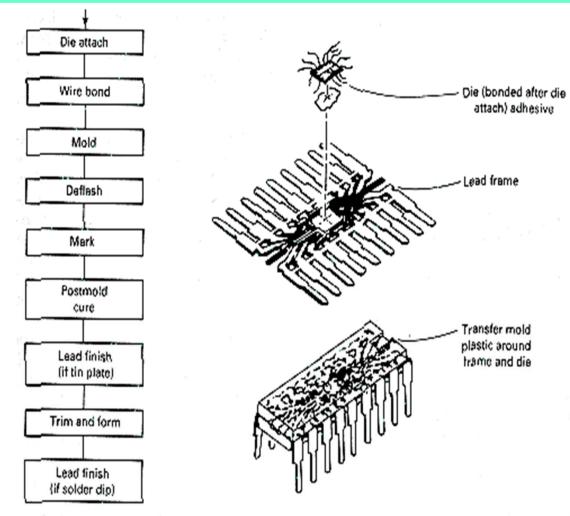

# TÉCNICAS DE ENCAPSULAMENTO 2D (PLÁSTICOS)

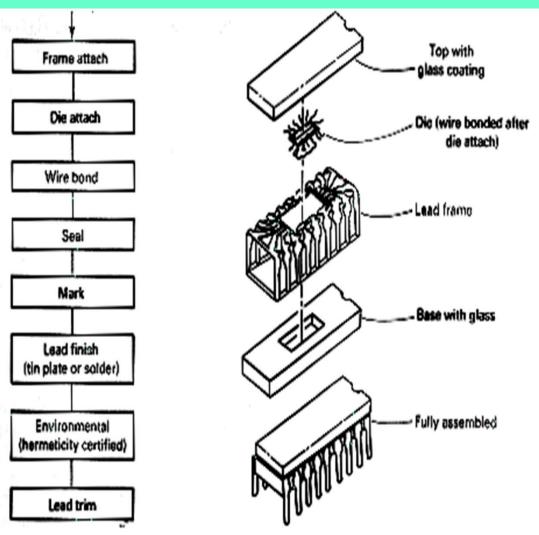

Fig. 7 Assembly sequence for plastic postmolded dual-in-line package. The lead frame serves as the chip carrier after die bond and wire bond.

Fig. 1 View of lead frame positioning in postmolded nonhermetic package showing wire interconnects from chip to inner leads of lead frame

# TÉCNICAS DE ENCAPSULAMENTO 2D (Cerâmicos)

Fig. 6 Assembly sequence for ceramic dual-in-line packages. Base and top components come already glaze coated with glass for lead frame sink and seal.

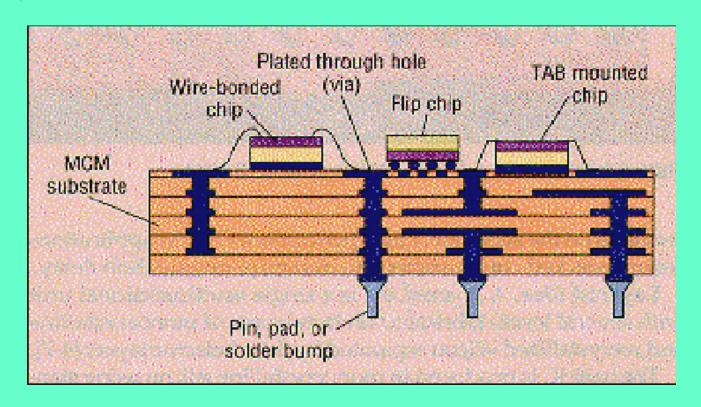

## MÓDULOS MCM

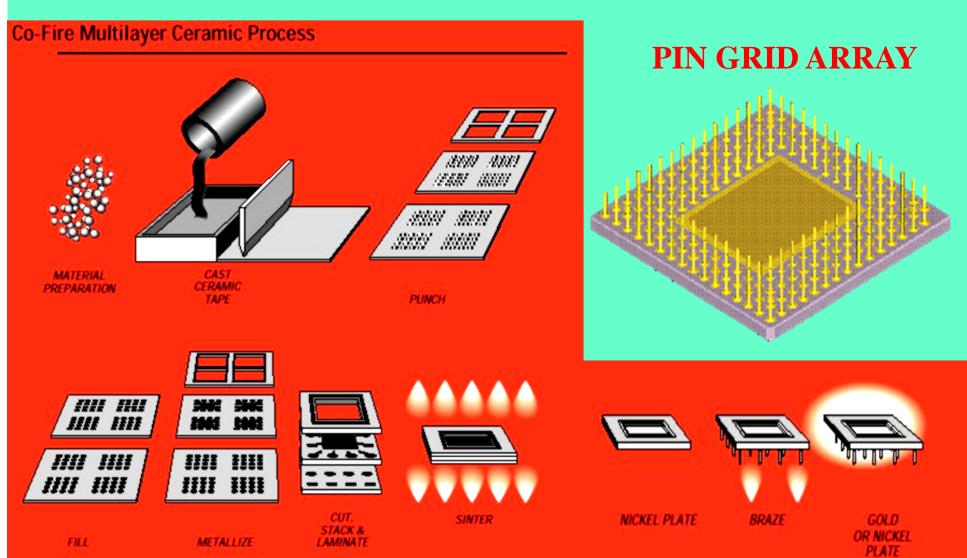

# PROCESSO MULTICAMADA LTCC PARA ENCAPSULAMENTOS (2D) CERÂMICOS

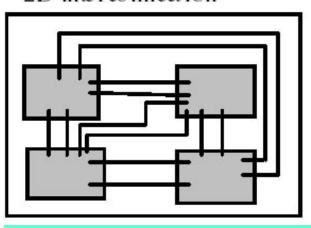

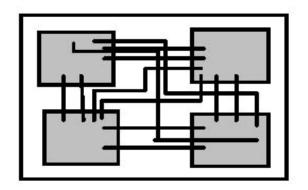

#### DE "2D" PARA "3D"

- Vantagens do encapsulamento 3D

- -Área e peso do encapsulamento

- Interconexões em 3D

- -Possibilidade de integrar passivos

- -Eficiência de Silício

- -Menores retardo e maior largura de banda

- -Menor ruído e consumo de potência

- -Maior acessabilidade para interconexões verticais

2D chip packaging 2D interconnection

2D chip packaging 3D interconnect ion

3D chip packaging

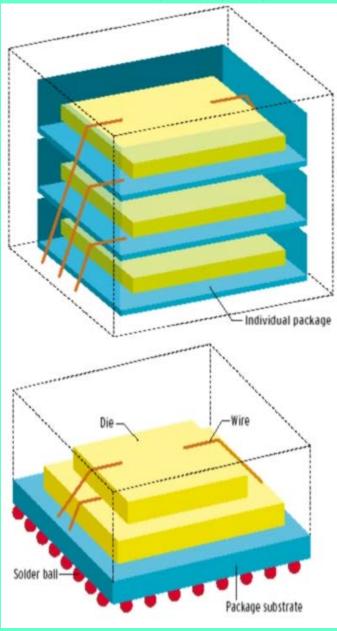

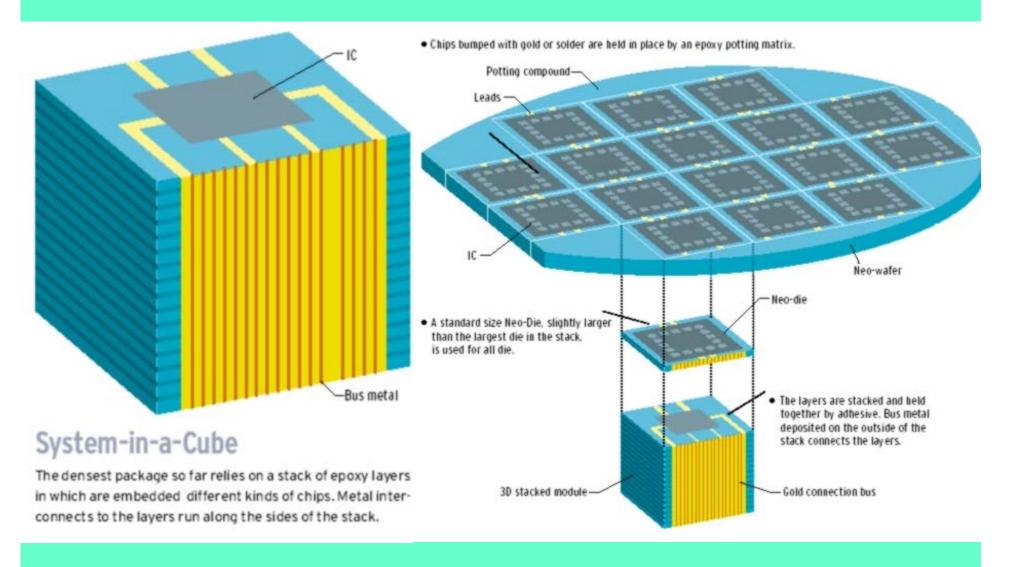

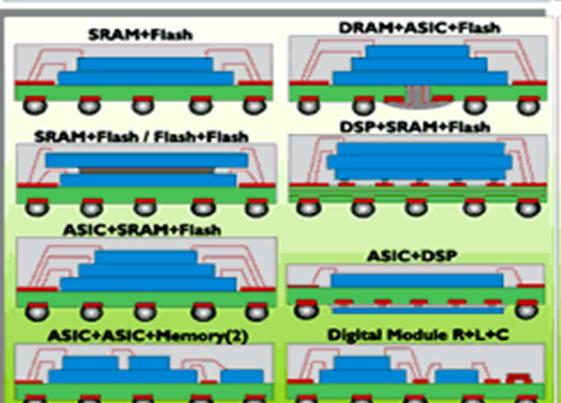

# TÉCNICAS DE ENCAPSULAMENTO 3D

#### EMPILHAMENTO DE CHIPS

# TÉCNICAS DE ENCAPSULAMENTO 3D (Cont.)

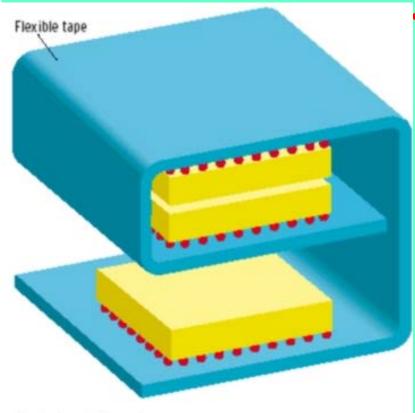

## Folded Package

One of the newer ways for cramming capability into a small package starts with packaged chips on a flat polyimide tape. The flexible tape is then folded to yield a small footprint.

# • ENCAPSULAMENTO DOBRÁVEL 3D

# SISTEMA NUM CUBO EMPILHAMENTO COM CONEXÕES LATERAIS

#### SISTEMAS NUM "CHIP"

#### SOC & SOP Solutions

#### Sytem on a Chip (SOC)

Performance driven

Large die, high pin count BGA

Die / package area ratio <100

6 High cost

#### Sytem in a Package (SOP)

- Minimum footprint

- § Z-direction integration

- Die / package area ratio = 250

- Low cost, 1.7X

- Short time-to-market

- § Technology mix: CMOS, GaAs, SiGe

- S Design mix: analog, digital

- S Assembly technology mix wire bond, flip chip, passives

# COMPARAÇÃO DE CONCEITOS PARA "MEMS PACKAGING"

| Source: Fraunhofer Institute      | 2D Integration |                | 3D Integration   |               |

|-----------------------------------|----------------|----------------|------------------|---------------|

|                                   | packaged       | unpackaged     | packaged         | unpackaged    |

|                                   |                |                |                  |               |

| Size and weight                   | high           | higher than 3D | lower than 2D    | low           |

| Silicon efficiency                | very good      | good           | very good        | low           |

| Power consumption (parasitic C's) | high           | rather high    | rather low       | low           |

| Noise                             | not optimal    | not optimal    | good             | very good     |

| Flexibility / universality        | restricted     | restricted     | high             | restricted    |

| Use of market-available MEMS      | feasible       | difficult      | <b>fe</b> asible | difficult     |

| Standardization of interfaces     | feasible       | difficult      | feasible         | difficult     |

| Additional packaging steps        | necessary      | not necessary  | necessary        | not necessary |

| Protection against environment    | high           | almost none    | high             | almost none   |

| Need for cleanroom environment    | no             | yes            | ho               | yes           |

Table 1: Comparision of MEMS module packaging concepts

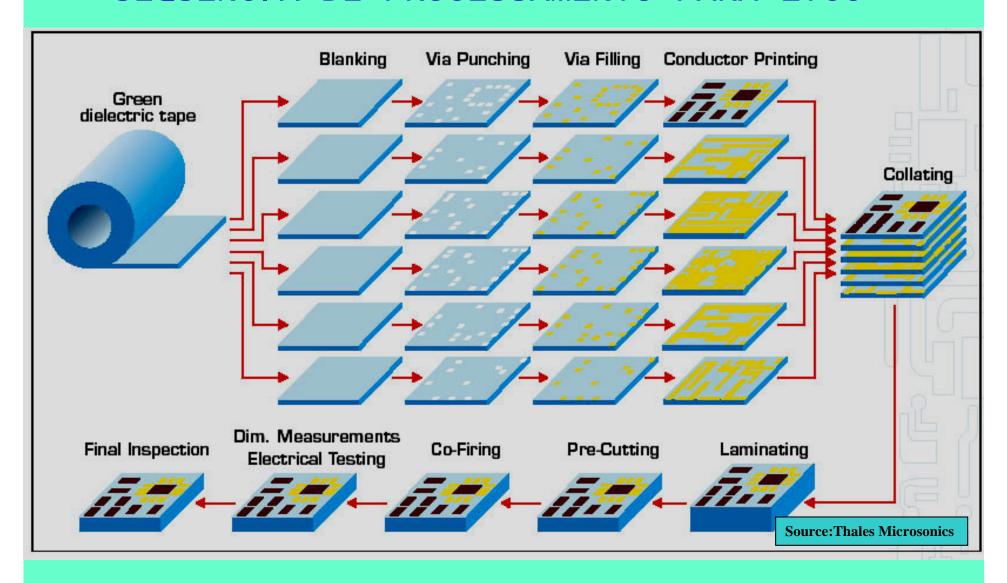

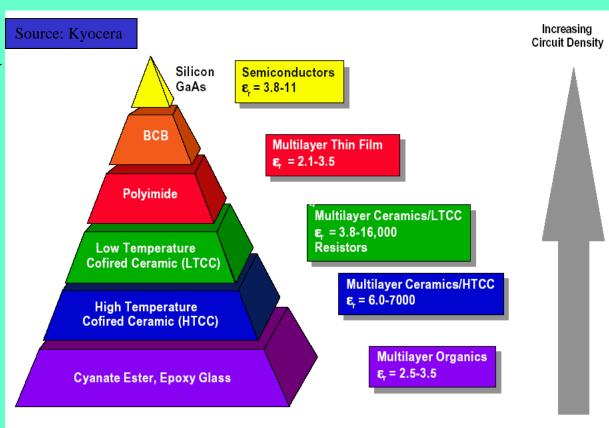

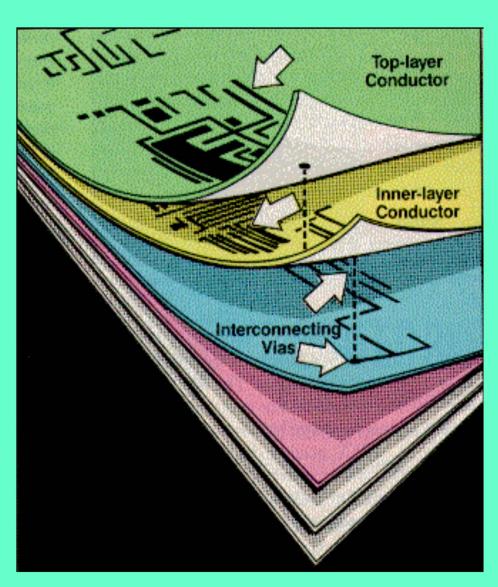

# LTCC (LOW TEMPERATURE COFIRED CERAMICS)

- A tecnologia LTCC foi originalmente desenvolvida pela Hughes e DuPont para sistemas militares.

- Esta tecnologia pode ser definida como uma forma de produzir circuitos multicamada com a ajuda de fitas cerâmicas onde podem ser aplicados filmes condutores, dielétricos ou resistivos.

- Estas fitas cerâmicas podem ser laminadas junto para obter um corpo que será sinterizado numa etapa só.

- Isto permite um ganho de tempo, dinheiro; reduzindo as dimensões do circuito e permitindo a inspeção de cada camada, permitindo sua substituição antes da queima do dispositivo.

- Devido à baixa temperatura de sinterização 850°C é possível a utilização de materiais de baixa resistividade como prata e ouro.

O tamanho dos circuitos pode ser reduzido de forma considerável devido a interligações em 3D e ainda permitindo a colocação de resistores, capacitores e indutores enterrados contribuindo ao grau de integração do circuito.

# SEQUÊNCIA DE PROCESSAMENTO PARA LTCC

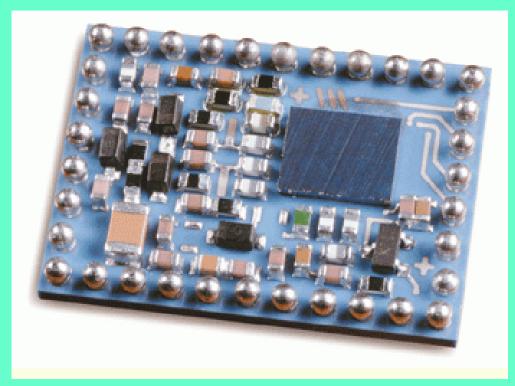

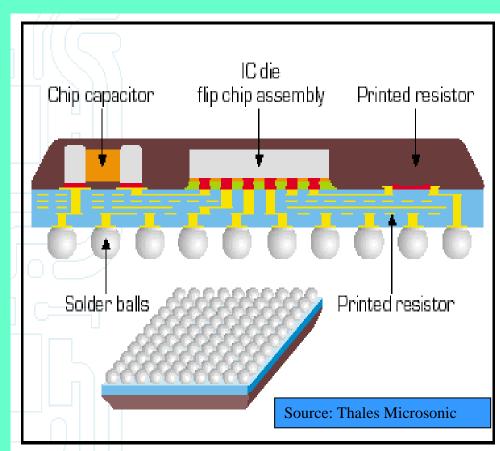

## TÉCNICAS AVANÇADAS DE ENCAPSULAMENTO COM LTCC

- A tecnologia LTCC pode ser adaptada para implementar técnicas de encapsulamento de altao desempenho, associando técnicas FLIP CHIP e BGA

- A combinação destas três tecnologias permite o projeto e fabricação Modulos multi-Chip de alta densidade e baixo custo

#### • FLIP CHIP BGA CSP

#### FLIP-CHIP EM LTCC

#### • Características de Flip-Chip em LTCC

- Distribuição de área ou periférica de Entradas/Saídas

- Distância Entradas/Saídas até 250 μm para batente (125 μm bump)

- Três técnicas possíveis de soldagem de fios

- Refusão de solda SnPb

- Termo compressão

- Adesivos condutivos

#### • Vantagens de Flip-Chip em LTCC

- Soldagem direta nas vias superiores sem metalização adicional

- CTE do LTCC parecido com o CTE do Si

- Alta capacidade de roteamento da tecnologia devido a:

- Estruturas com vias enterradas de diâmetro até 100 μm)

- Distância entre linhas de até 200 µm (usando técnicas convencionais)

- Grande quantidade de camadas

## LTCC REALIZA PASSIVOS INTEGRADOS

- LTCC apresenta uma faixa extensa de propriedades dielétricas quando comparada com qualquer tecnologia de encapsulamento e ainda permite incorporar componentes passivos integrados.

- A tecnologia LTCC pode incorporar resistores, indutores e capacitores enterrados aumentando muito a densidade de componentes da aplicação.

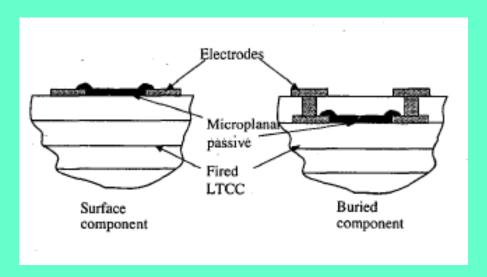

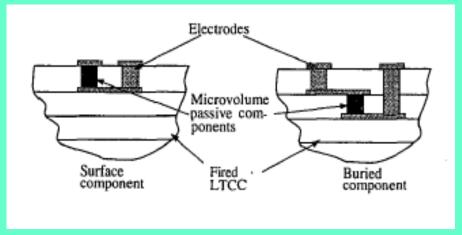

#### RESISTORES ENTERRADOS

- Resistores enterrados podem ser fabricados usando pasta convencionais ou pastas fotosensíveis de filme espesso.

- Existem dois tipos de resistores enterrados :

- -Passivo Microplanar

- -Passivo Microvolumétrico

- Técnicas de Trimming de alta tensão podem ser usadas para ajustar os valores dos componentes enterrados.

# APLICAÇÃO DE LTCC EM MCM

• LTCC se adapta muito bem na implementação de MCM de alto desempenho usando as técnicas de encapsulamento Flip-Chip e BGA.

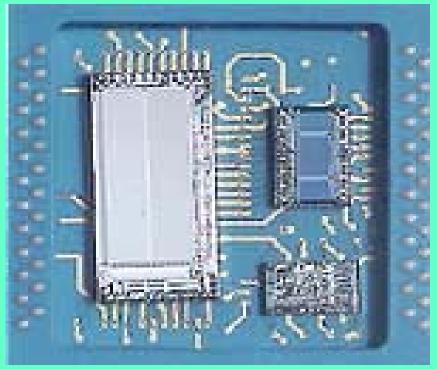

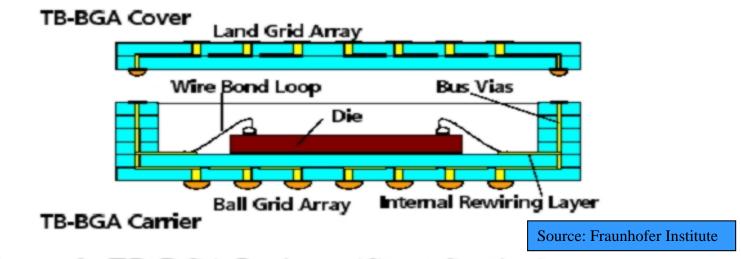

## LTCC TB-BGA PARA MCM

| size      | 12,5 x 12,5 |

|-----------|-------------|

| use       | 9,6 x 11,0  |

| pin count | 4 8         |

| BGA pitch | 1,27        |

units: m m

## LTCC EM MST/MEMS

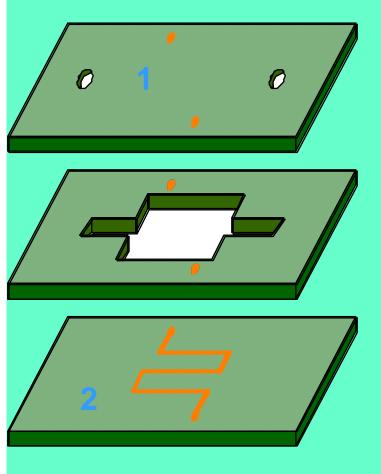

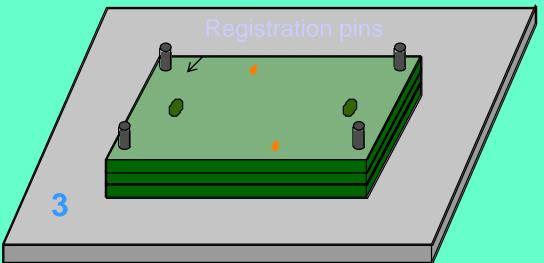

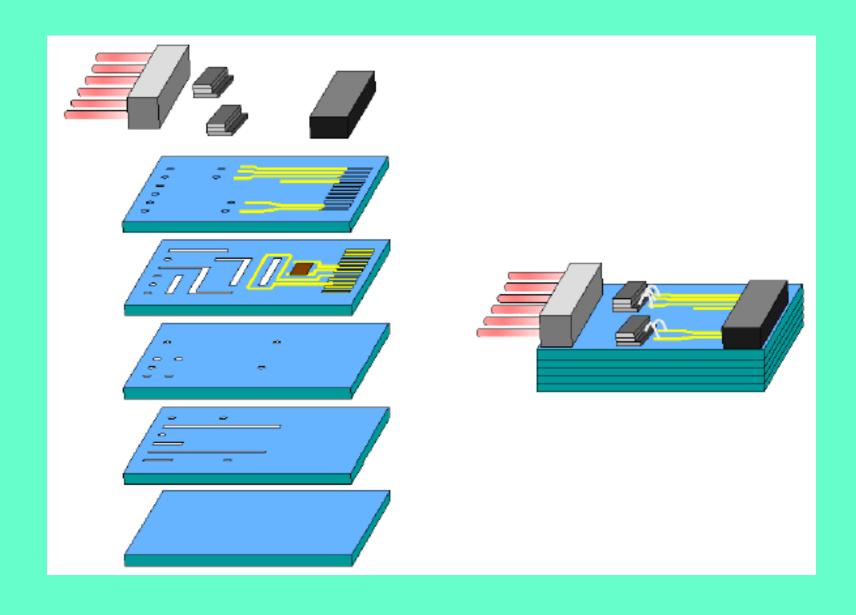

- 1. Maquinado das camadas individuais para definir geometrias

- 2. Serigrafia e preenchimento de vias através de mascaras

- 3. Alinhamento e empilhamento

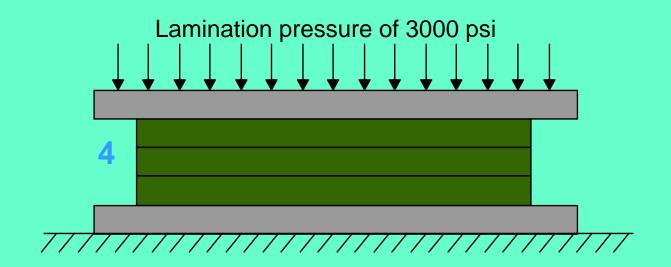

## LTCC EM MST/MEMS

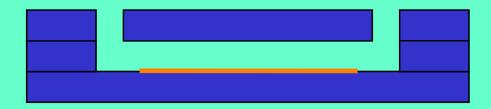

4. Laminação

5. Co-queimado

Cross-section after firing

# MI CROSISTEMAS EM LTCC

# "MANIFOLDS" COM LTCC PARA MICROFLUIDICA

# APLICAÇÕES DE LTCC EM MICROFLUIDICA

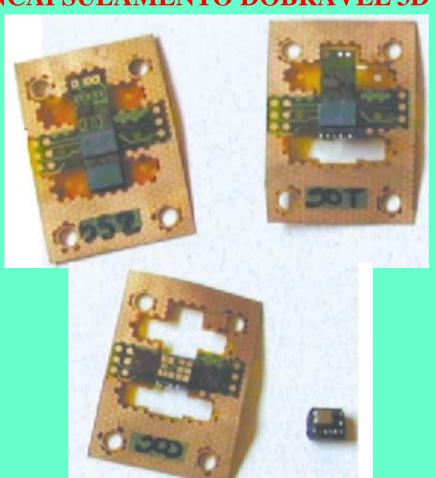

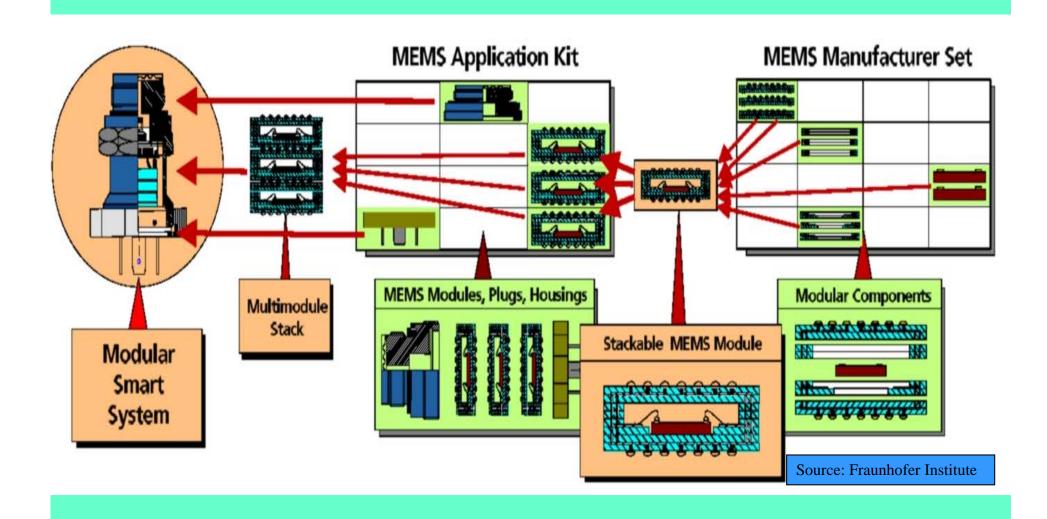

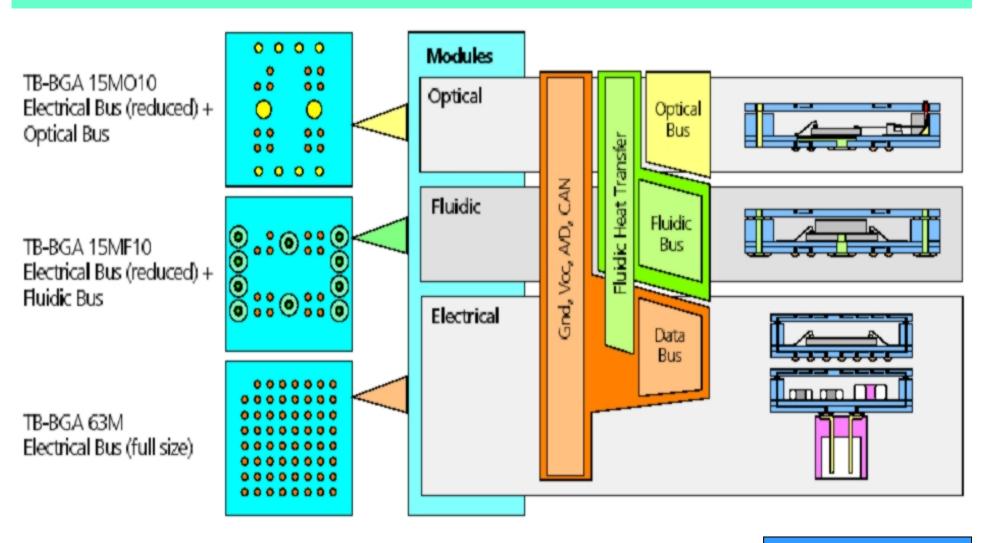

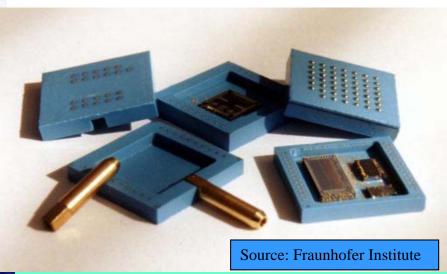

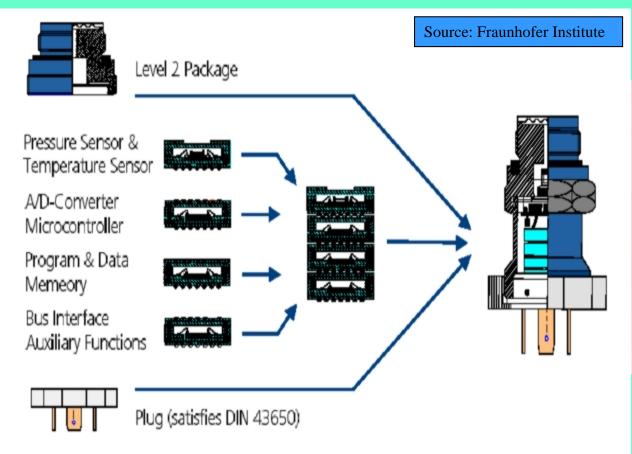

## NOVO CONCELTO: MICRO-SISTEMAS MODULARES

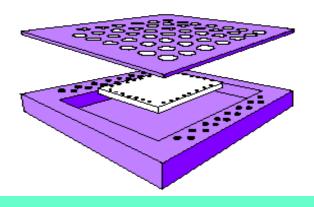

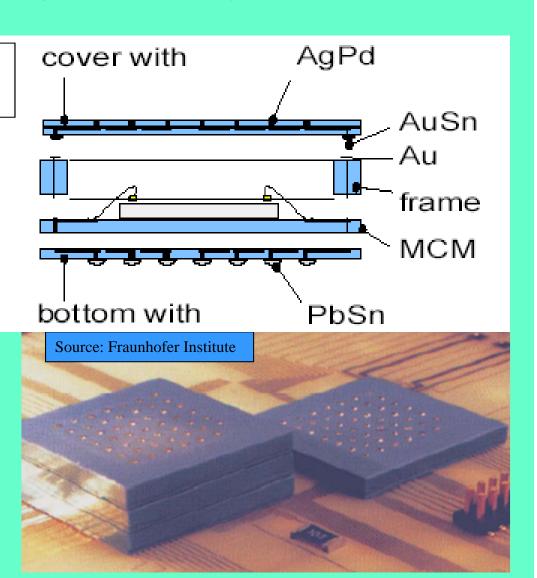

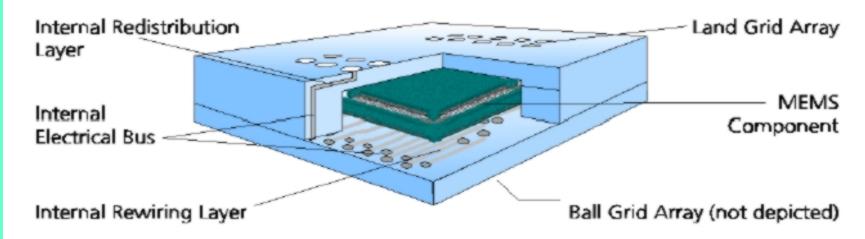

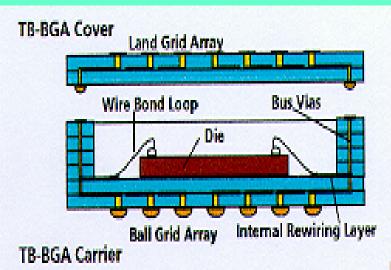

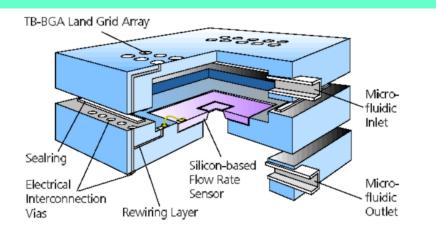

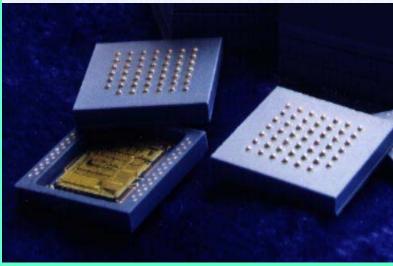

## TB-BGA (TOP-BOTTOM- BALL GRID ARRAY) COM LTCC

Figure 3: TB-BGA Package (Cross Section)

Figure 4: TB-BGA Package (Perspective View)

#### INTERFACES NO SISTEMA MODULAR

Figure 7: TB-BGA Interface Concept

Source: Fraunhofer Institute

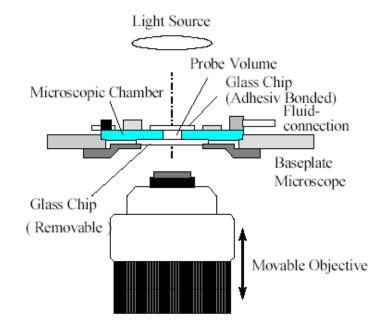

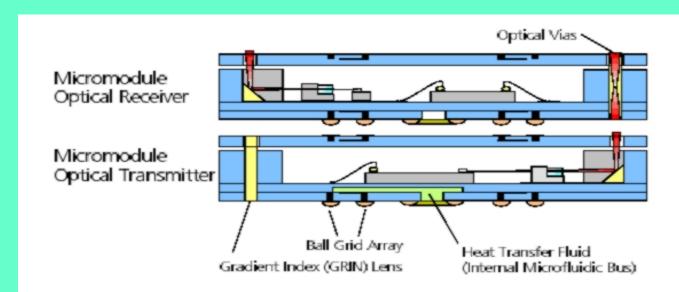

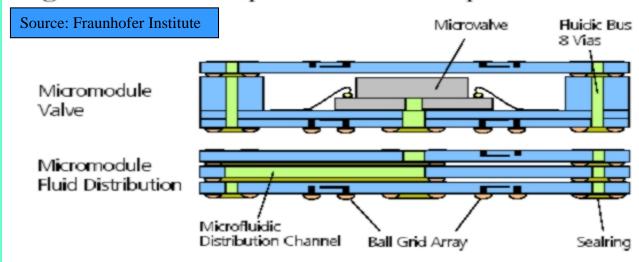

# INTERFACES ÓTICAS E FLUÍDICAS

Figure 5: MEMS Optical Module & Optical Interface

Figure 6: MEMS Microfluidic Module & Fluidic Interface

## MÓDULOS DESENVOLVIDOS

• Microcontrolador de 16 Bits e Medidor de Vazão

**Figure 17:** Design of a Flow Rate Sensor Module (LTCC)

# APLICAÇÕES DO CONCEITO MODULAR (SMART PRESSURE CONTROL SYSTEM)

Figure 20: Modularized Smart Pressure Control System

#### BI BLI OGRAFI A

- M. Madou Fundamentals of Microfabrication, Orlando FL: CRC, 1.997, ISBN: 0849394511

- R. Tummala, Fundamentals of Microsystems Packaging, McGraw-Hill Professional Publishing, 2001. ISBN 0-07-137169-9

- W.S.N. Trimmer (ed.). Micromechanics and MEMS-Classic and Seminal Papers to 1.990, IEEE Press, New York, 1.997

- T.R. Hsu, Packaging Design of Microsystems and Meso-Scale Devices, IEEE Transactions on Advanced Packaging, Vol-23, No4, p-596-601, Nov. 2000

- H. Goldstein, Packages Go Vertical, IEEE Spectrum, August 2001

- M. Shuenemann et al., A highly flexible design and production framework for modularized microelectromechanical systems, Sensors and Actuators, Elsevier, V. 73 p. 153–168, 1999

- M. R. Gongora Rubio, transparências do curso Tecnologias de Encapsulamento do MPCE-FATEC / LSI-EPUSP, 2001