### **PSI3024 – Eletrônica**

Aulas 33 e 34 2023

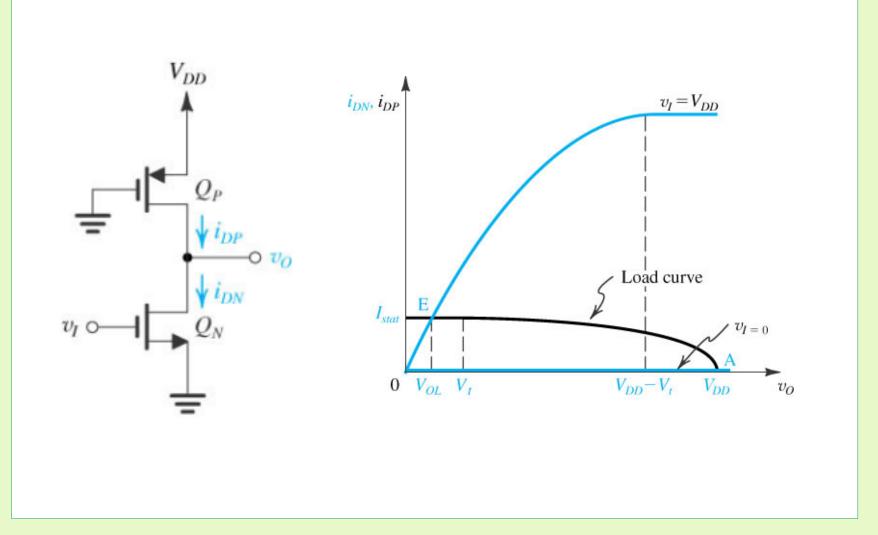

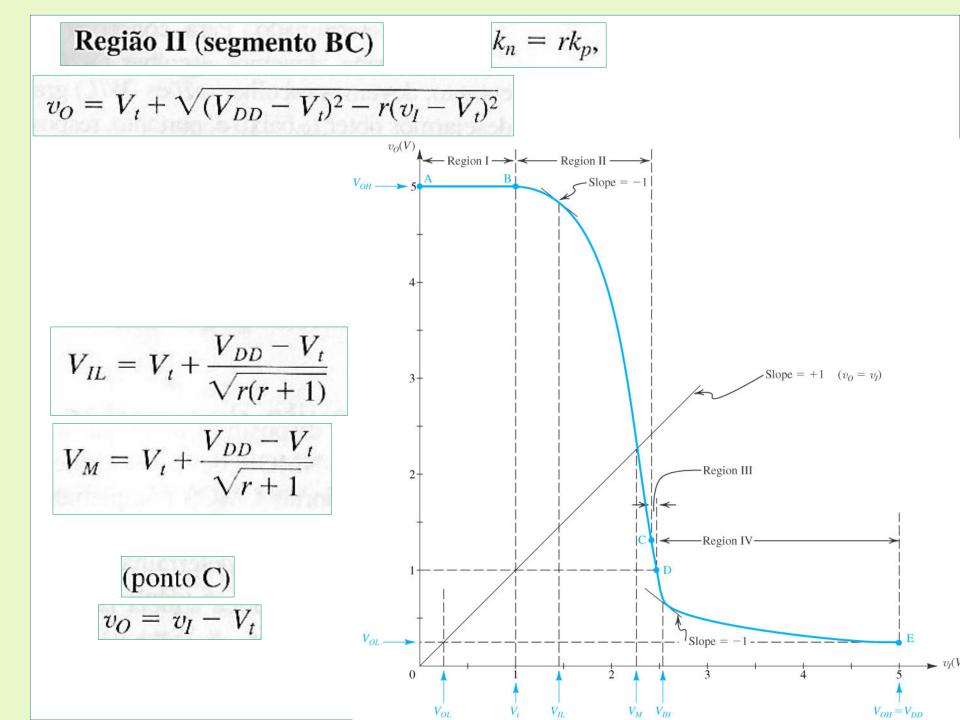

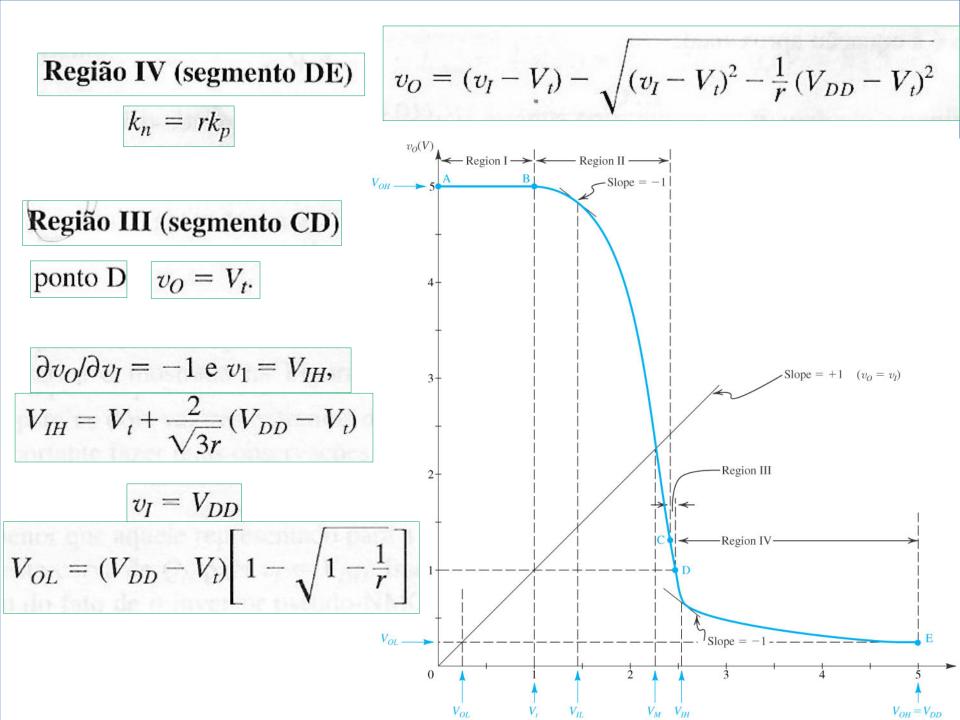

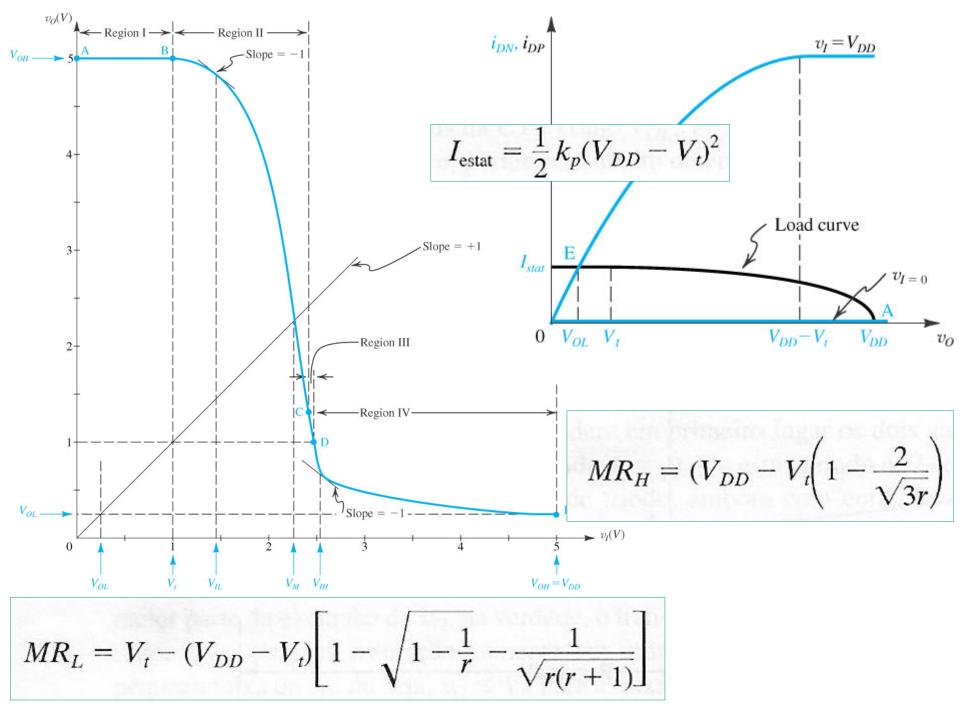

## **Inversor pseudo-NMOS**

#### EXEMPLO 10.3

Considere o inversor pseudo-NMOS fabricado na tecnologia CMOS especificada no Exemplo 10.1, ou seja,  $\mu_n C_{ox} = 115 \ \mu \text{A/V}^2, \ \mu_p C_{ox} = 30 \ \mu \text{A/V}^2, \ V_{tn} = -V_{tp} = 0.4 \text{ V e } V_{DD} = 2.5 \text{ V}.$  Seja a razão *W/L* de  $Q_N$  de  $(0,375 \ \mu \text{m}/0.25 \ \mu \text{m})$  e r = 9. Obtenha:

- (a)  $V_{OH}$ ,  $V_{OL}$ ,  $V_{IL}$ ,  $V_{IH}$ ,  $V_M$ ,  $MR_H e MR_L$ (b)  $(W/L)_p$

- (c)  $I_{\text{estat}} \in P_D$

- (d)  $t_{PLH}$ ,  $t_{PHL}$  e  $t_P$ , supondo uma capacitância total na saída do inversor de 7 fF

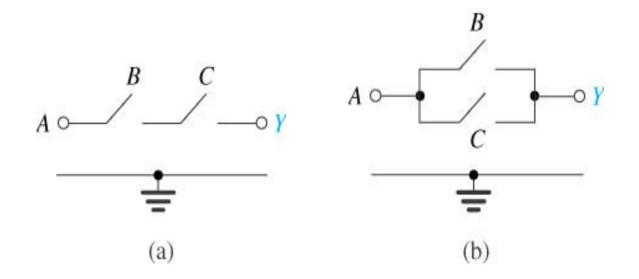

# Portas Lógicas com transistores de passagem

Figure 10.23 Conceptual pass-transistor logic gates. (a) Two switches, controlled by the input variables B and C, when connected in series in the path between the input node to which an input variable A is applied and the output node (with an implied load to ground) realize the function Y = ABC. (b) When the two switches are connected in parallel, the function realized is Y = A(B + C).

0

$t_{PLH}$

t

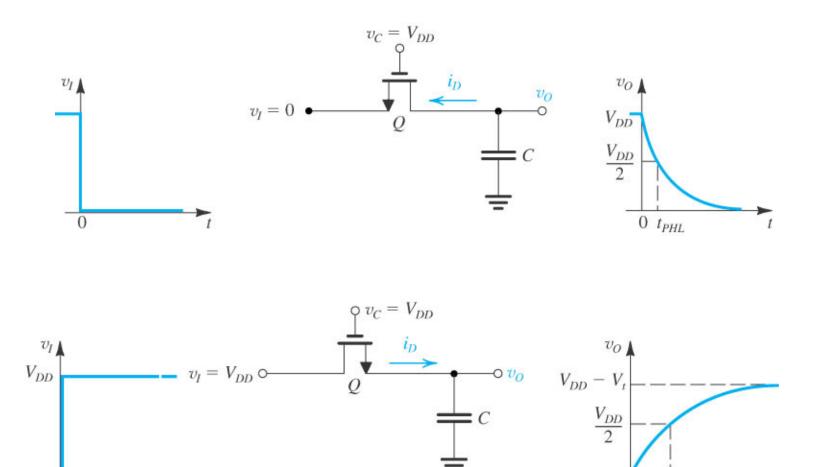

• Figure 10.27 e 10.28 – Transistor NMOS como chave de passagem .

1

0

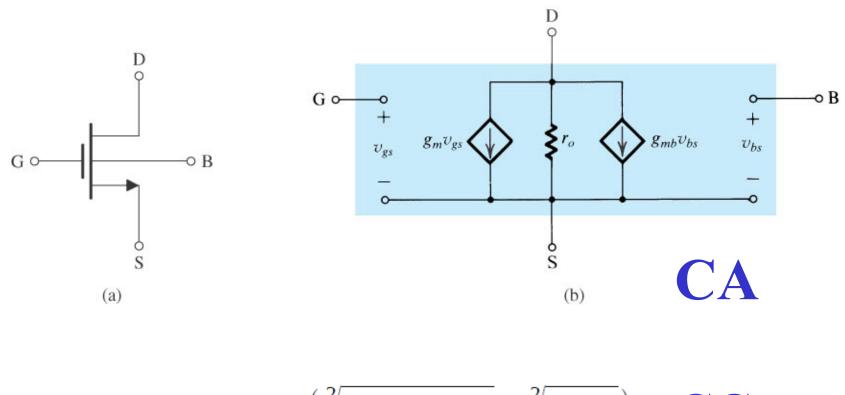

## Efeito de corpo

$$V_t = V_{t0} + \gamma \left( \sqrt[2]{V_{SB}} + 2 \cdot \phi_F - \sqrt[2]{2} \cdot \phi_F \right) \quad \mathbf{CC}$$

Figure 4.41 Small-signal equivalent-circuit model of a MOSFET in which the source is not connected to the body.

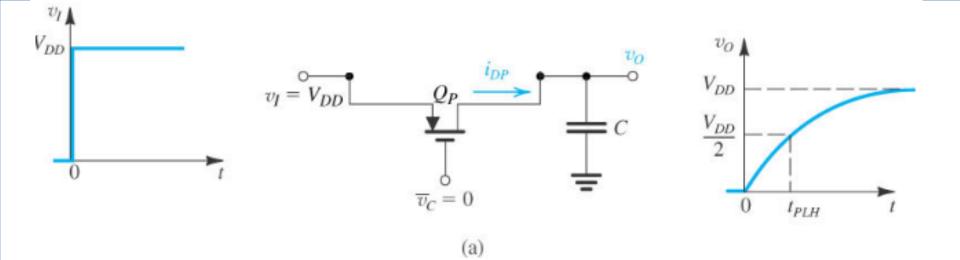

Transistor PMOS como chave de passagem .

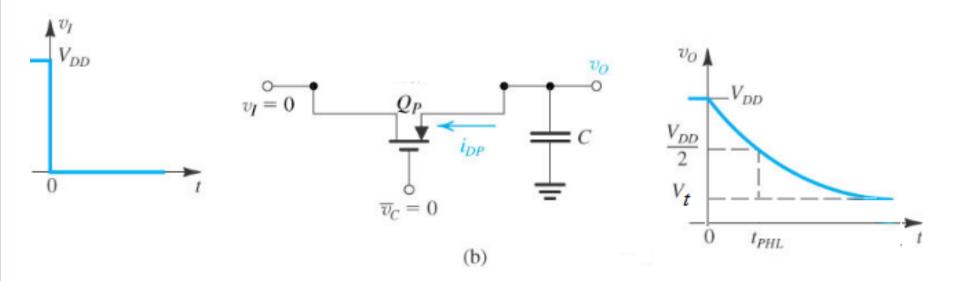

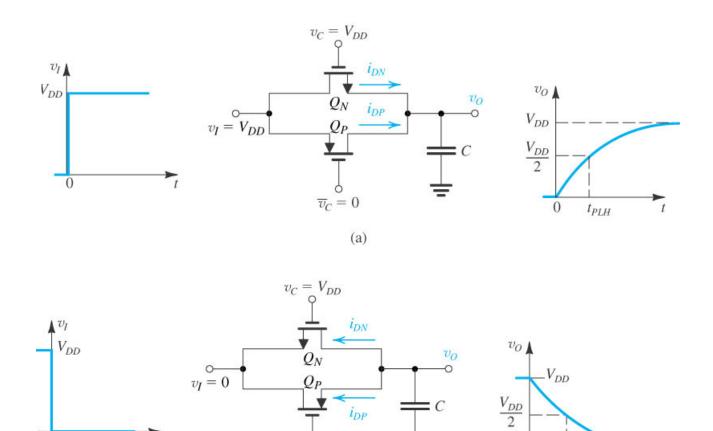

• **Figure 10.29** Operation of the transmission gate as a switch in PTL circuits with (a)  $v_1$  high and (b)  $v_1$  low.

$\overline{v}_C = 0$

(b)

0

$t_{PHL}$

t

0

t

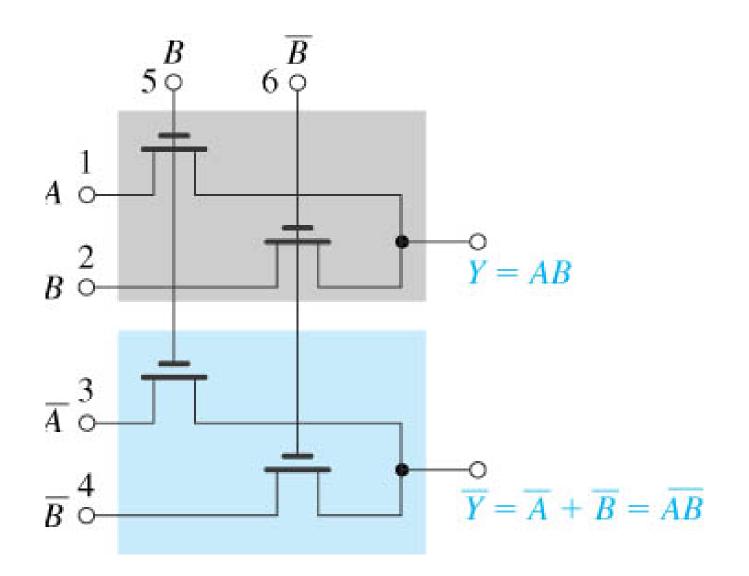

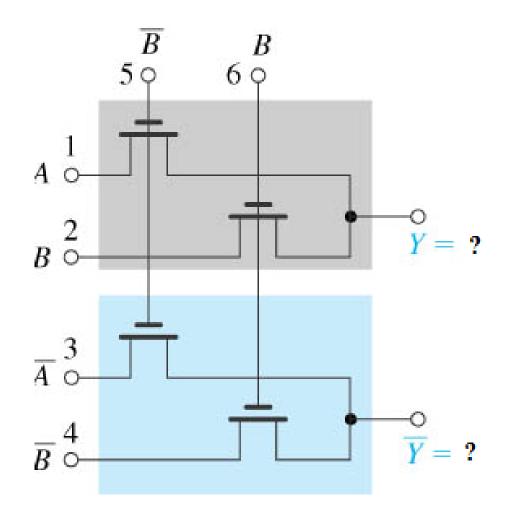

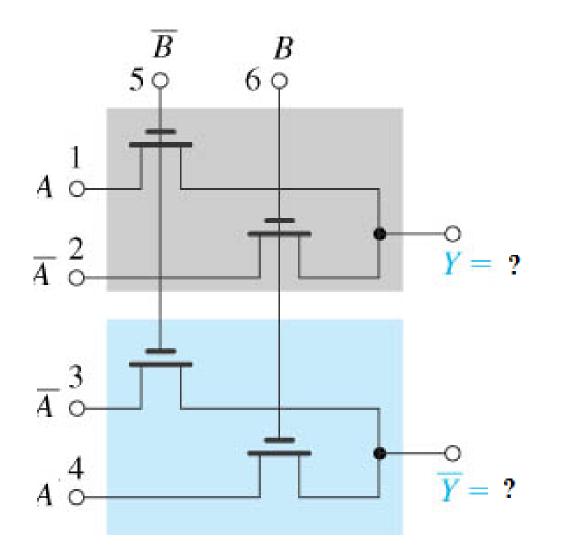

• **Figure 10.32** An example of a pass-transistor logic gate utilizing both the input variables and their complements. This type of circuit is therefore known as complementary pass-transistor logic or CPL. Note that both the output function and its complement are generated.

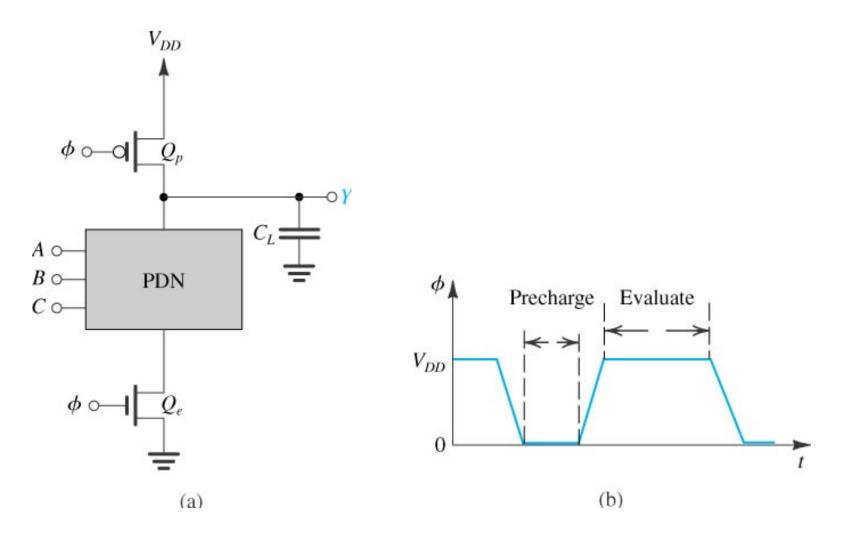

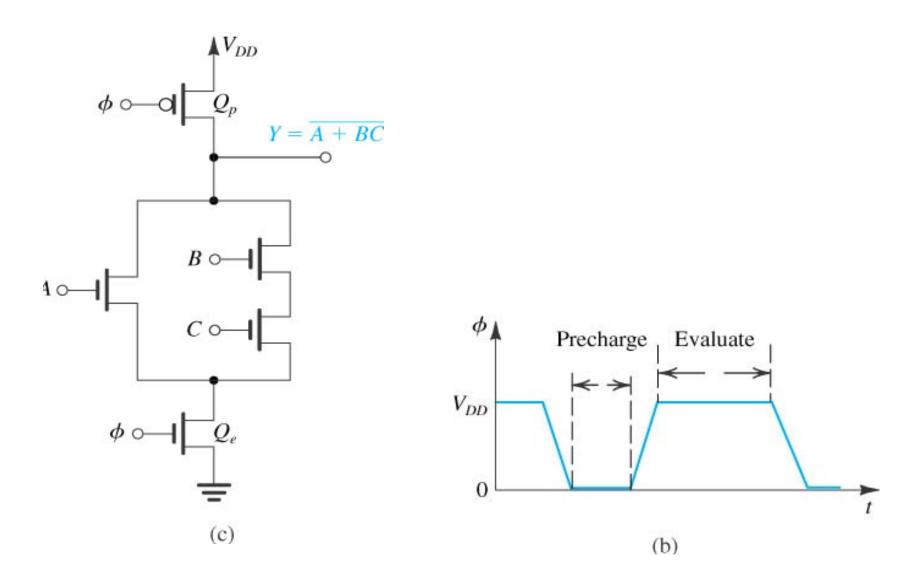

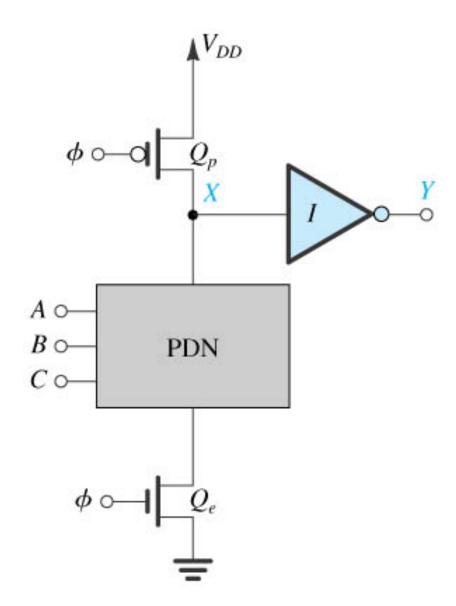

• Figure 10.33 (a) Basic structure of dynamic-MOS logic circuits. (b) Waveform of the clock needed to operate the dynamic logic circuit. (c) An example circuit.

• Figure 10.33 (a) Basic structure of dynamic-MOS logic circuits. (b) Waveform of the clock needed to operate the dynamic logic circuit. (c) An example circuit.

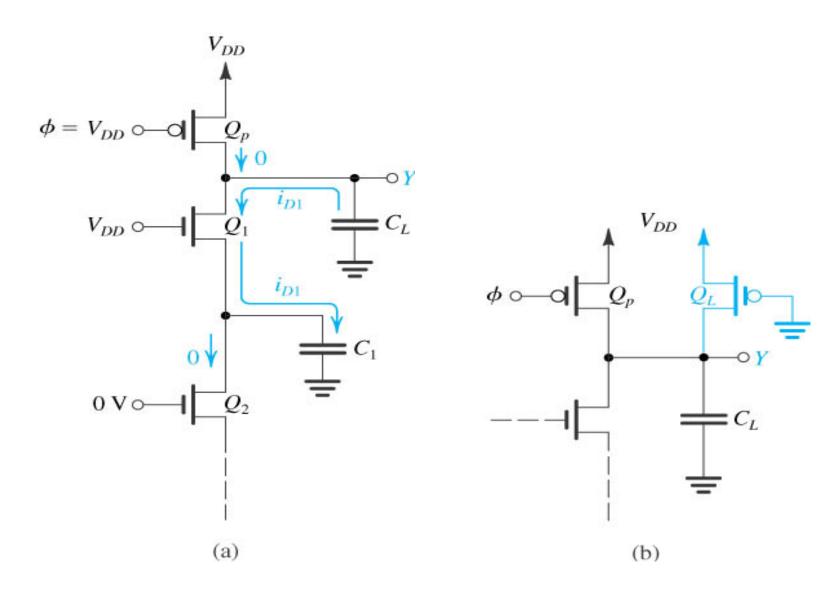

• **Figure 10.34** (a) Charge sharing. (b) Adding a permanently turned-on transistor Q<sub>L</sub> solves the charge-sharing problem at the expense of static power dissipation.

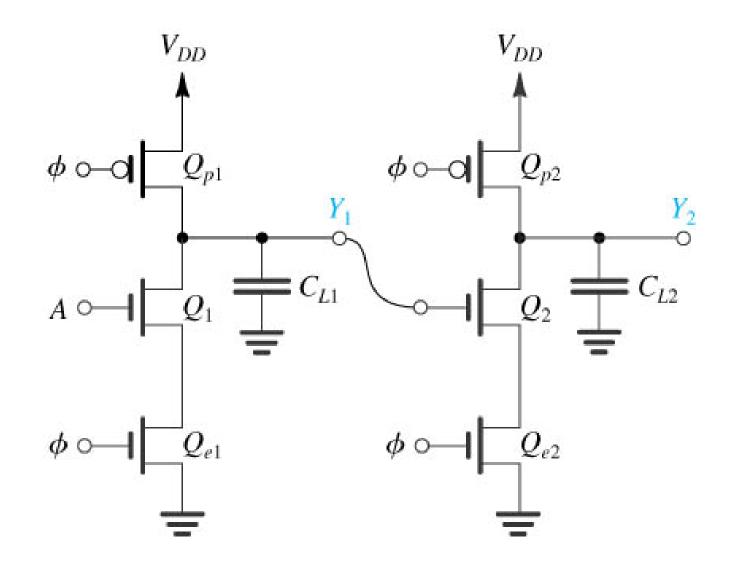

• **Figure 10.35** Two single-input dynamic logic gates connected in cascade. With the input A high, during the evaluation phase  $C_{L2}$  will partially discharge and the output at  $Y_2$  will fall lower than  $V_{DD}$ , which can cause logic malfunction.

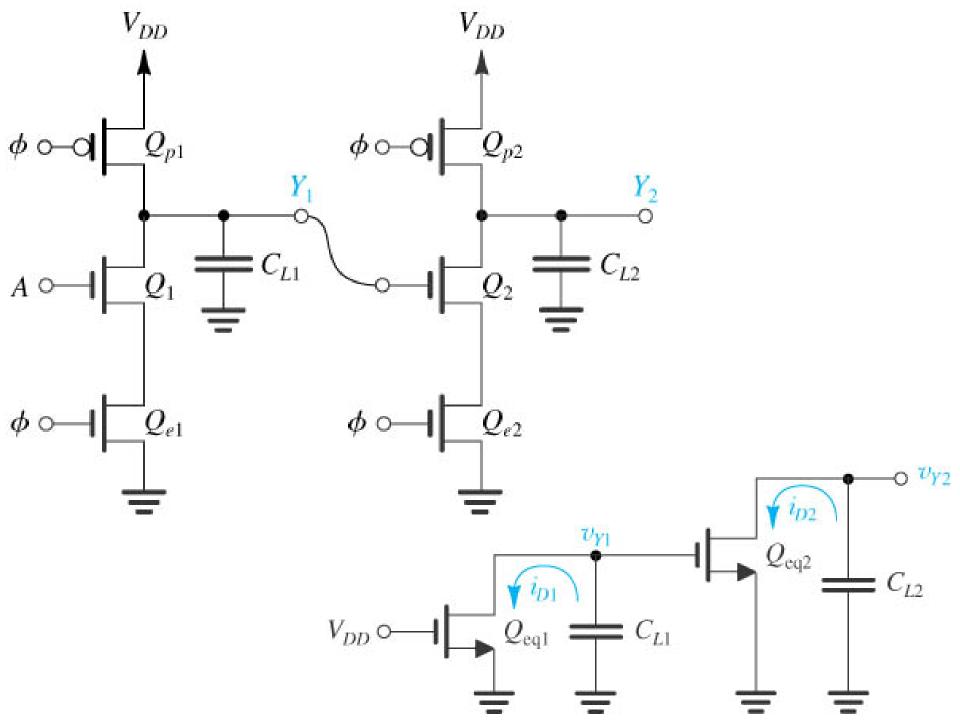

• **Figure 10.36** The Domino CMOS logic gate. The circuit consists of a dynamic-MOS logic gate with a static-CMOS inverter connected to the output. During evaluation, Y either will remain low (at 0 V) or will make one 0-to-1 transition (to V<sub>DD</sub>).

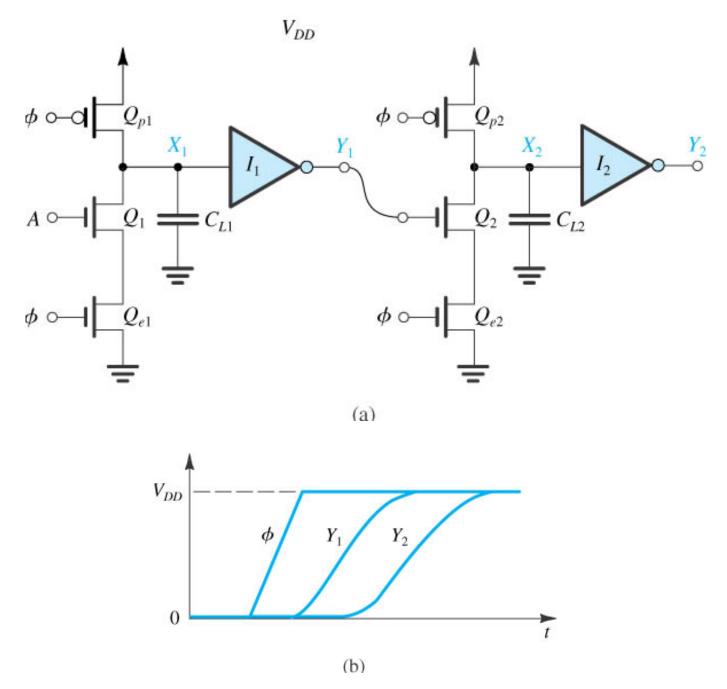

• Figure 10.37 (a) Two single-input domino CMOS logic gates connected in cascade. (b) Waveforms during the evaluation phase.

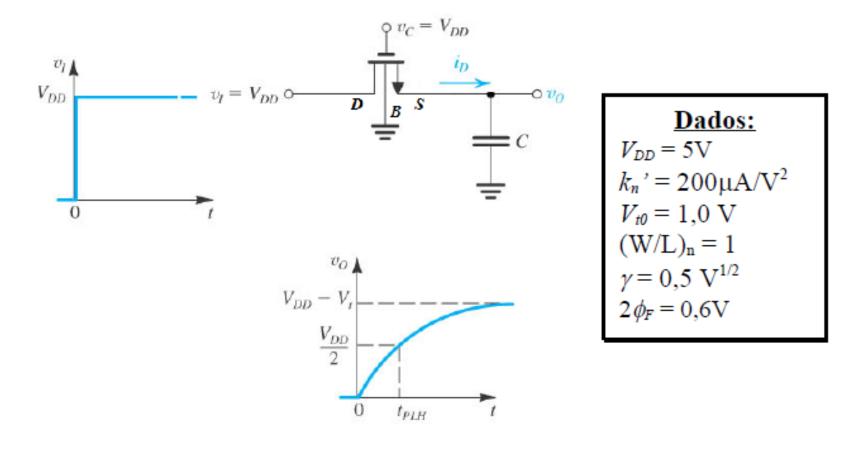

Considere o transistor NMOS habilitado como porta de passagem ( $v_C = V_{DD}$ ). conforme indicado na figura a seguir. Sabendo-se que o substrato (*B*) está aterrado, determine o valor numérico da tensão de saída sobre o capacitor *C* após sua carga completa.

FORMULARIO

$$V_t = V_{t0} + \gamma \left(\sqrt[2]{V_{SB} + 2 \cdot \phi_F} - \sqrt[2]{2 \cdot \phi_F}\right)$$

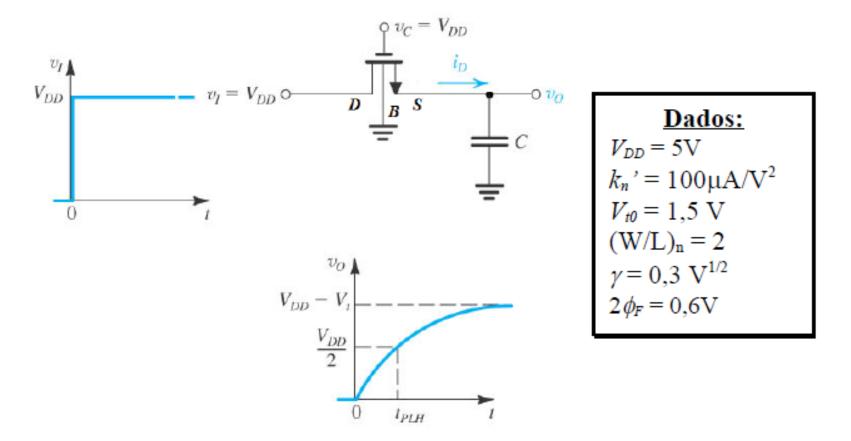

Considere o transistor NMOS habilitado como porta de passagem  $({}^{v_{C}} = V_{DD})$ . conforme indicado na figura a seguir. Sabendo-se que o substrato (*B*) está aterrado, determine o valor numérico da tensão de saída sobre o capacitor *C* após sua carga completa.

FORMULARIO

$$V_t = V_{t0} + \gamma \left(\sqrt[2]{V_{SB} + 2 \cdot \phi_F} - \sqrt[2]{2 \cdot \phi_F}\right)$$

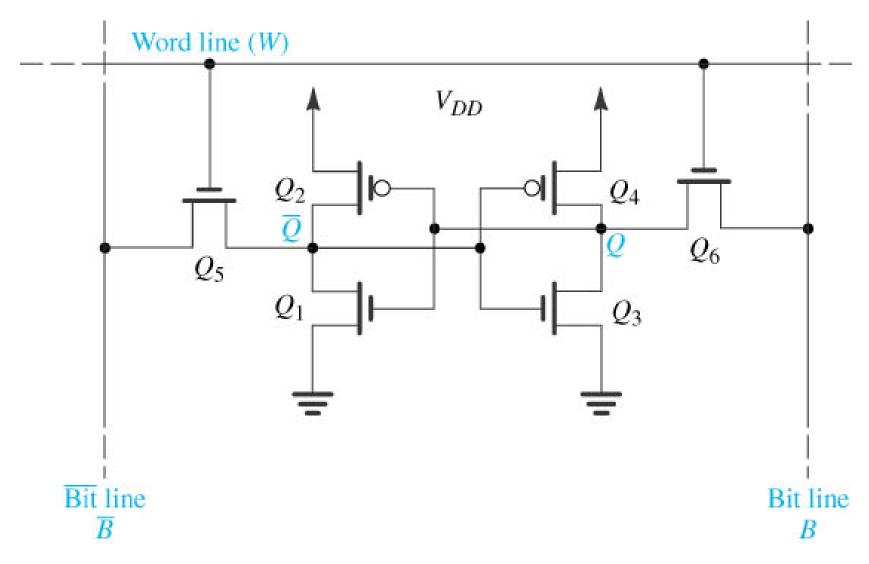

## Célula de Memória SRAM CMOS

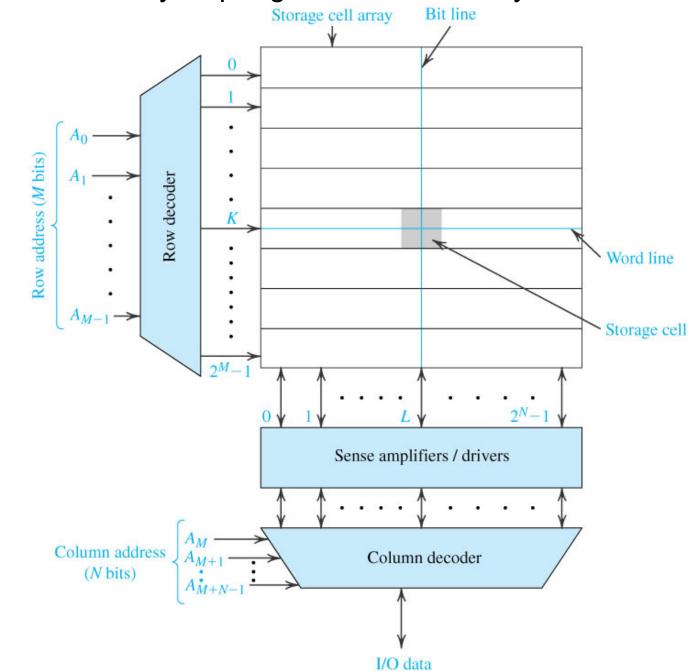

• A  $2^{M+N}$ -bit memory chip organized as an array of  $2^{M}$  rows  $\times 2^{N}$  columns.

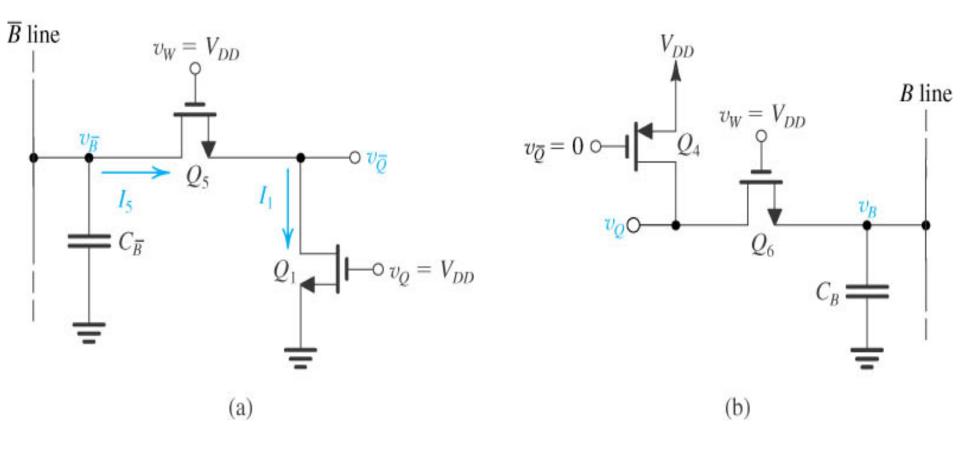

• **Figure 11.19** Relevant parts of the SRAM cell circuit during a read operation when the cell is storing a logic 1. Note that initially  $v_q = V_{DD}$  and  $v_q = 0$ . Also note that the *B* and *B* lines are usually precharged to a voltage of about  $V_{DD}/2$ . However, in Example 11.2, it is assumed for simplicity that the precharge voltage is  $V_{DD}$ .

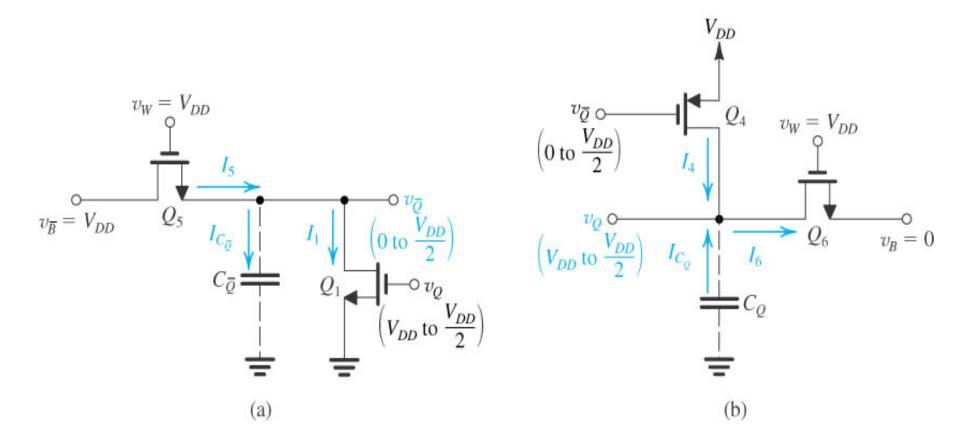

• **Figure 11.20** Relevant parts of the SRAM circuit during a write operation. Initially, the SRAM has a stored 1 and a 0 is being written. These equivalent circuits apply before switching takes place. (a) The circuit is pulling node Q up toward  $V_{DD}/2$ . (b) The circuit is pulling node Q down toward  $V_{DD}/2$ .