## PSI3024 – Eletrônica

Aula 30 2023

# Portas Lógicas: Implementação

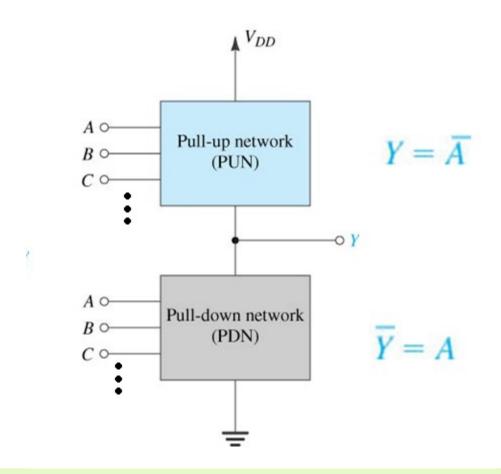

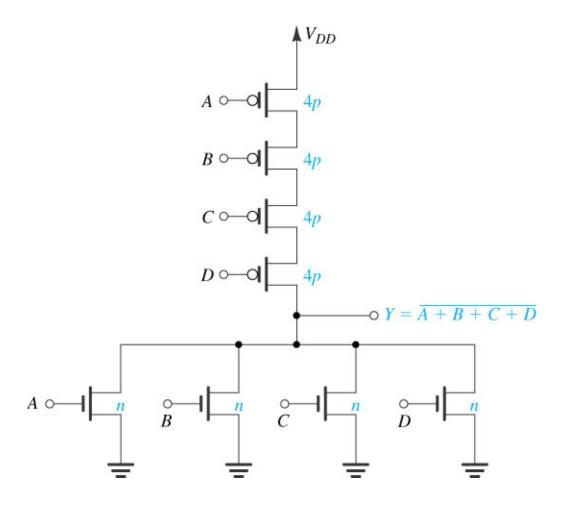

• **Figure 10.16** Proper transistor sizing for a four-input NOR gate. Note that n and p denote the (W/L) ratios of  $Q_N$  and  $Q_P$ , respectively, of the basic inverter.

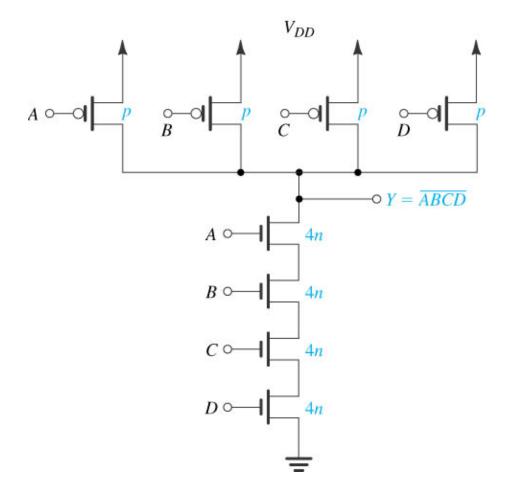

• **Figure 10.17** Proper transistor sizing for a four-input NAND gate. Note that n and p denote the (W/L) ratios of  $Q_N$  and  $Q_P$ , respectively, of the basic inverter.

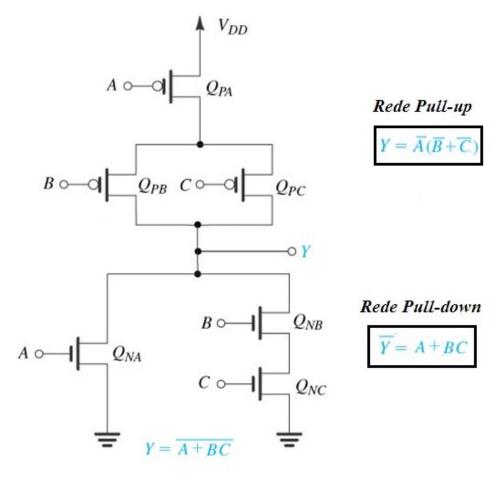

$$Y = \overline{A + B \cdot C} = \overline{A} \cdot (\overline{B} + \overline{C}), \quad \overline{Y} = A + B \cdot C$$

Figura 6

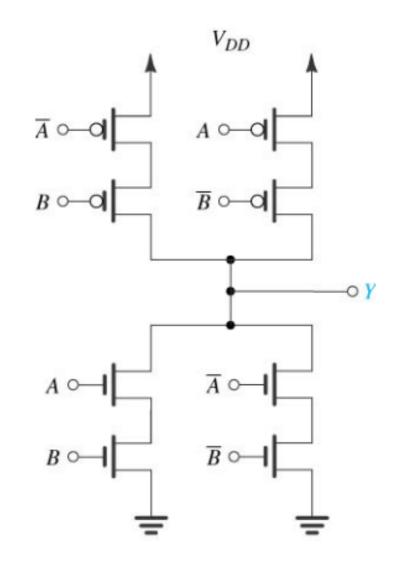

### **Ou-Exclusivo**

$$\overline{Y} = A.B + \overline{A.B}$$

• Figure 10.15 Realization of the exclusive-OR (XOR) function: (a) The PUN synthesized directly from the expression in Eq. (10.25). (b) The complete XOR realization utilizing the PUN in (a) and a PDN that is synthesized directly from the expression in Eq. (10.26). Note that two inverters (not shown) are needed to generate the complemented variables. Also note that in this XOR realization, the PDN and the PUN are not dual networks; however, a realization based on dual networks is possible (see Problem 10.27).

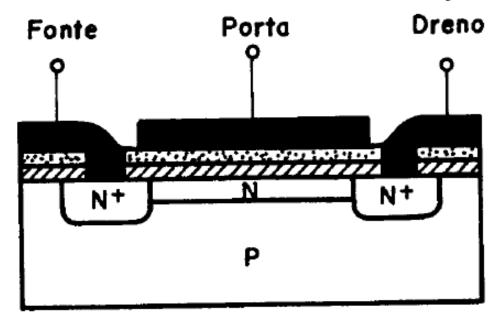

#### CIRCUITOS INVERSORES MOS

O circuito inversor é composto de dois dispositivos:

- um transistor de comando (por exemplo, nMOS)

- um elemento de carga.

O elemento de carga pode ser do tipo:

- a) resistiva

- b) transistor de enriquecimento em triodo

- c) transistor de enriquecimento em saturação

- d) transistor de depleção

- e) transistor tipo pMOS

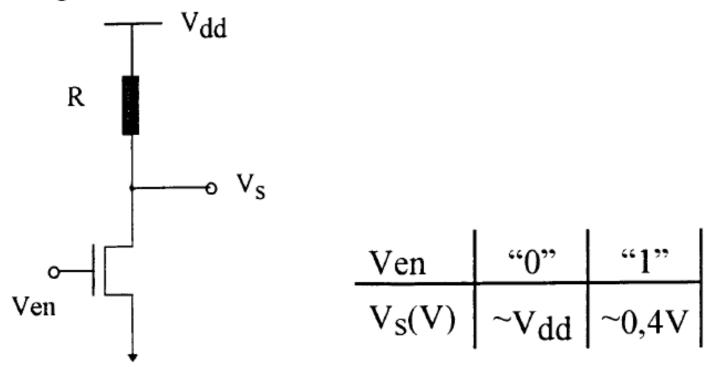

### a) Carga resistiva

Neste caso, Vs("0") depende do valor de R.

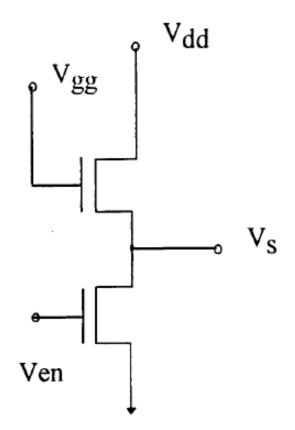

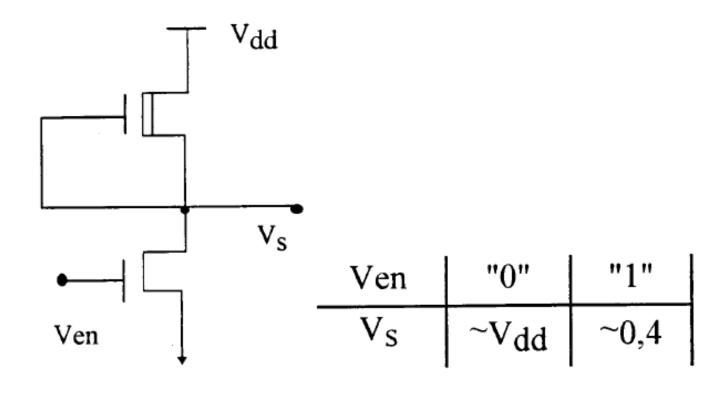

#### b) transistor de enriquecimento em triodo

| Ven        | "0"              | "1"_ |

|------------|------------------|------|

| $V_{S}(V)$ | ~V <sub>dd</sub> | ~0,4 |

Obs:  $V_{gg} > V_{dd} + V_t(V_s)$

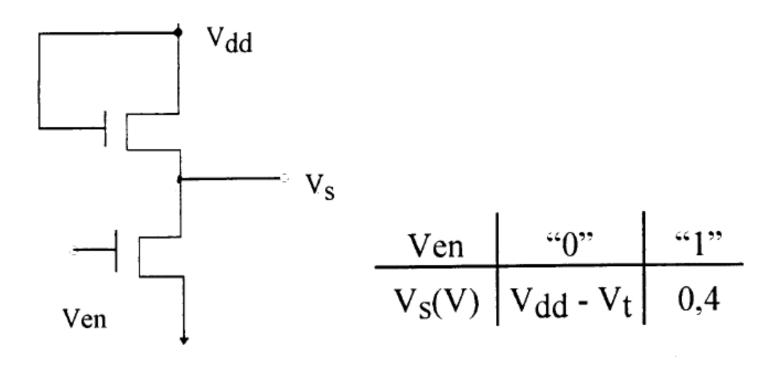

c) transistor de enriquecimento em saturação

#### TRANSISTOR TIPO DEPLEÇÃO

$$V_{TN} = +\frac{\left(2.q.N_{A}.\varepsilon_{o}.\varepsilon_{s}.2.\phi_{F}\right)^{1/2}}{C_{ox}} - \frac{Q_{ef}}{C_{ox}} - \frac{Q_{\operatorname{Im}}}{C_{ox}} + 2.\phi_{F} + \phi_{MS}$$

### d) transistor de depleção

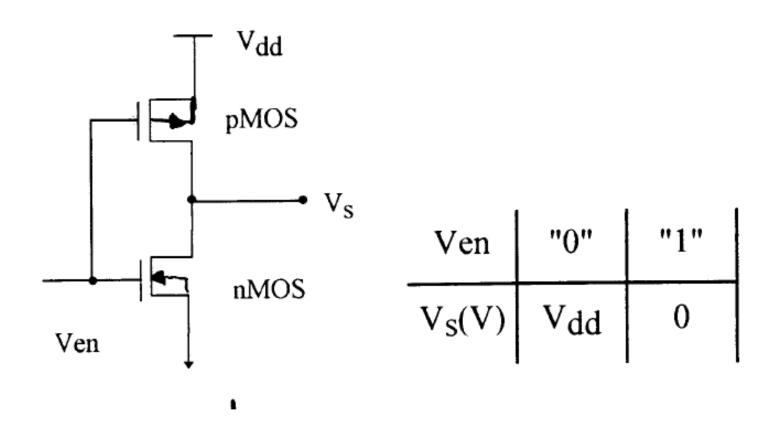

#### e) transistor tipo pMOS (inversor CMOS)

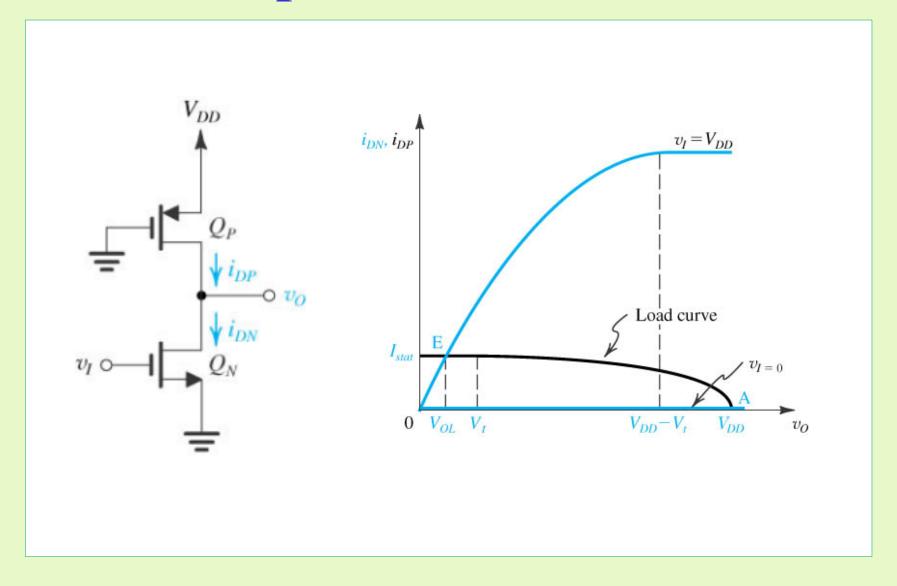

# Inversor pseudo-NMOS

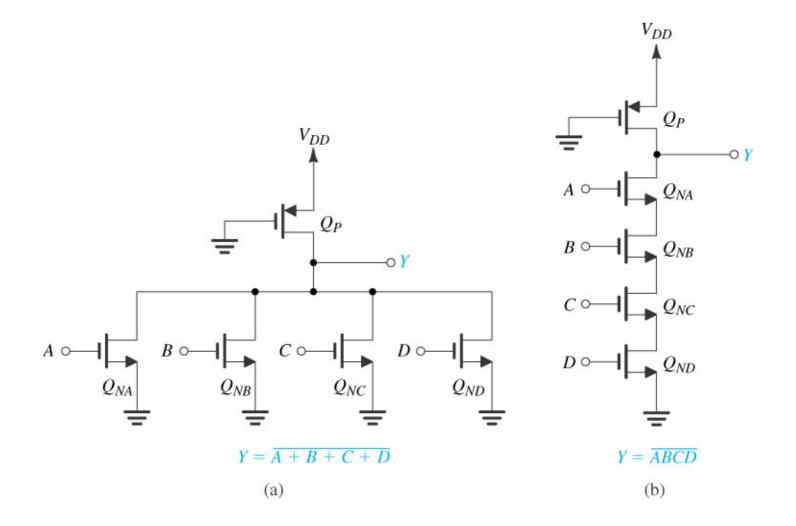

• Figure 10.22 NOR and NAND gates of the pseudo-NMOS type.