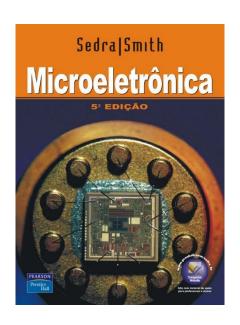

## PSI3322 - ELETRÔNICA II

(capítulos 4, 6, 7, 8)

PSI3322 - João A. Martino - PSI/EPUSP

## PSI3322 - ELETRÔNICA II

## Prof. João Antonio Martino

### AULA 2

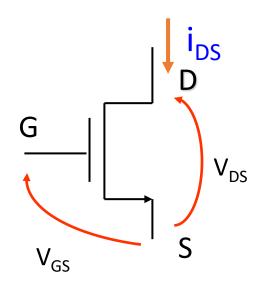

Estrutura e operação dos transistores de efeito de campo canal n, características tensão-corrente.

Sedra, Cap. 4 p. 141-146

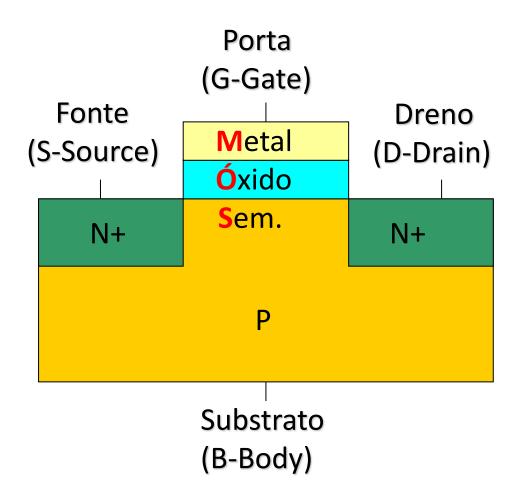

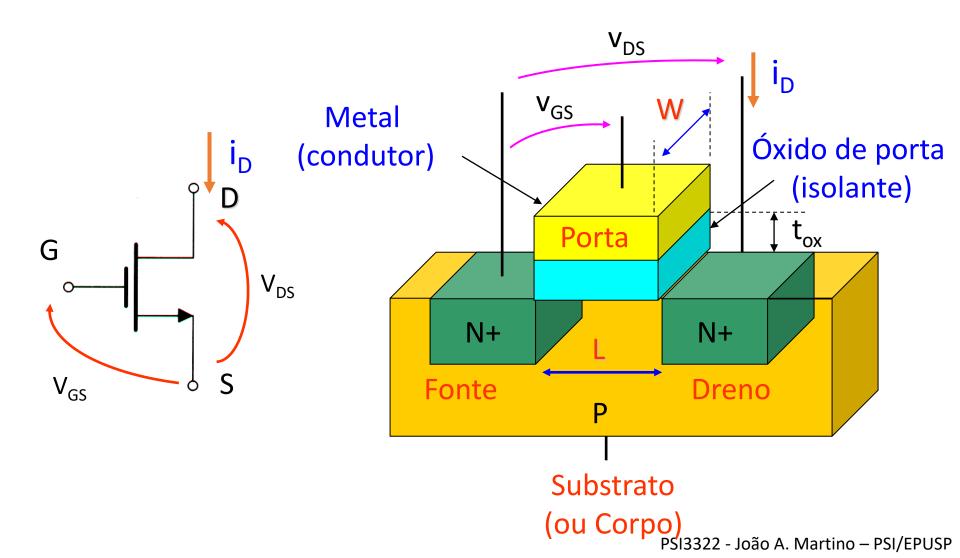

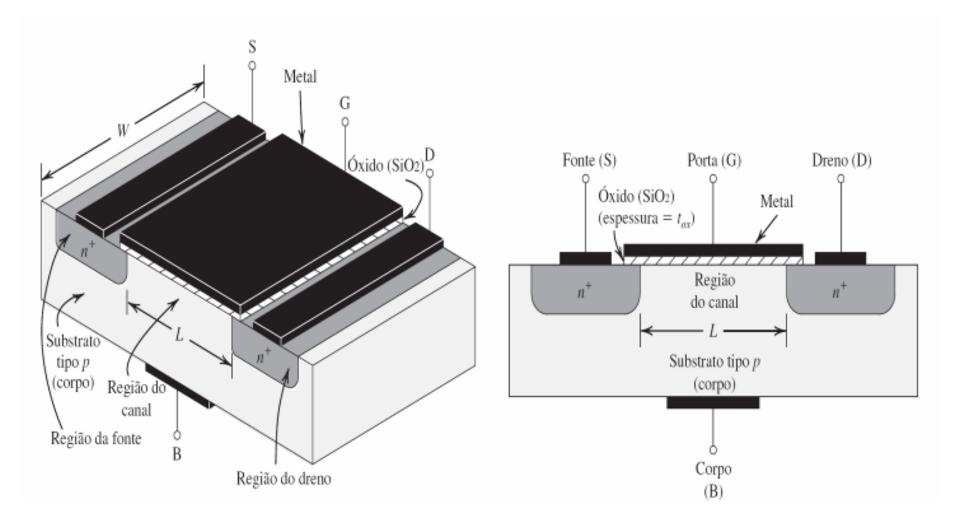

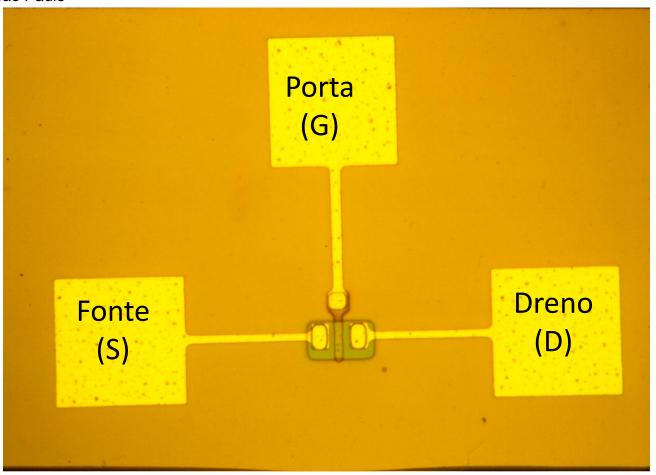

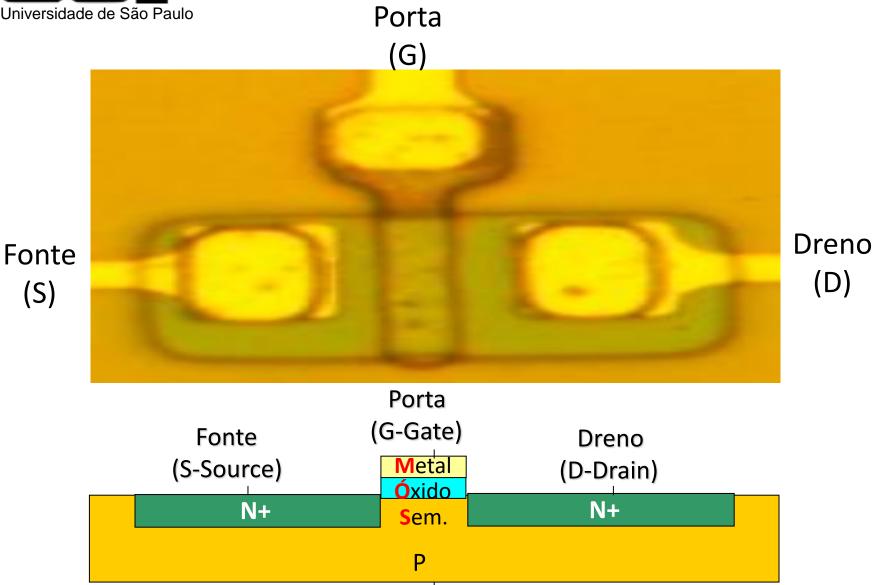

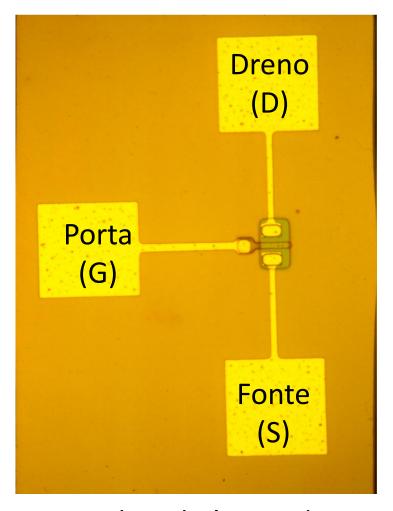

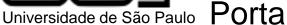

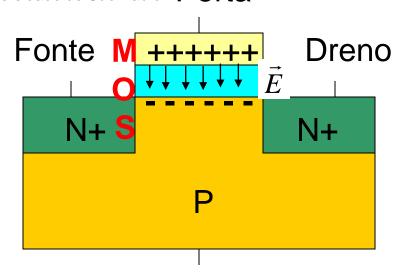

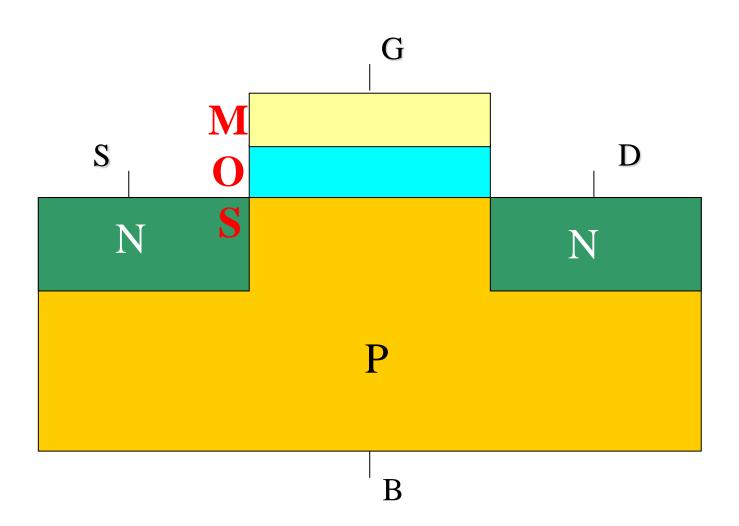

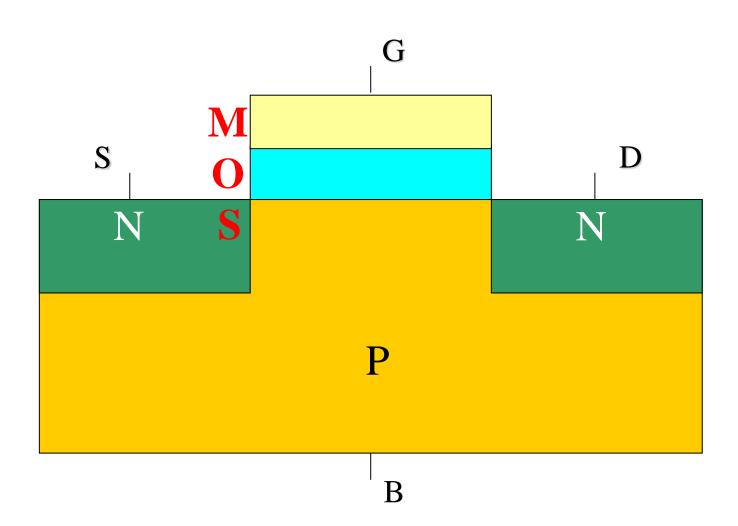

## (Metal-Oxide-Semiconductor Field Effect Transistor, canal N, tipo Enriquecimento)

(Metal-Oxide-Semiconductor Field Effect Transistor, canal N, tipo Enriquecimento)

## (Metal-Oxide-Semiconductor Field Effect Transistor, canal N, tipo Enriquecimento)

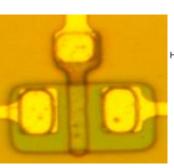

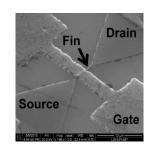

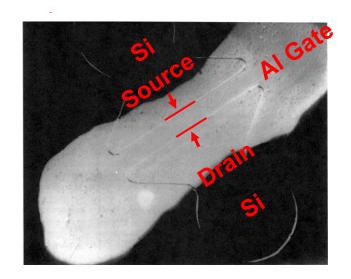

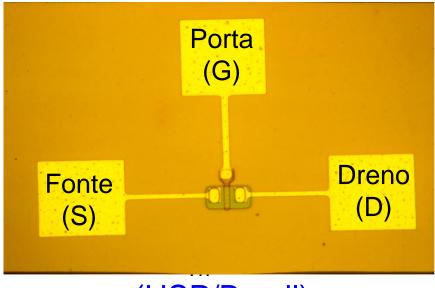

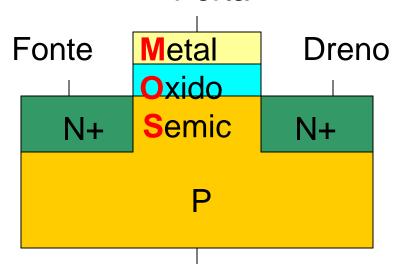

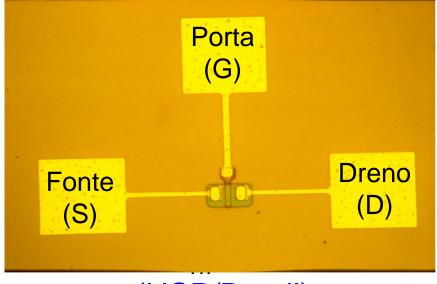

Transistor projetado e fabricado na Escola Politécnica da USP

(Dissertação de Mestrado - João Antonio Martino - 1984)

**(S)**

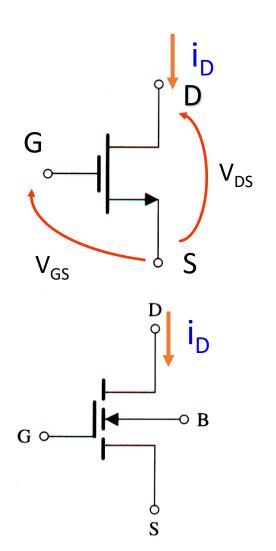

## **Transistor NMOS**

Substrato (B-Body)

PSI3322 - João A. Martino - PSI/EPUSP

Transistor projetado e fabricado na Escola Politécnica da USP

(Dissertação de Mestrado – João Antonio Martino - 1984)

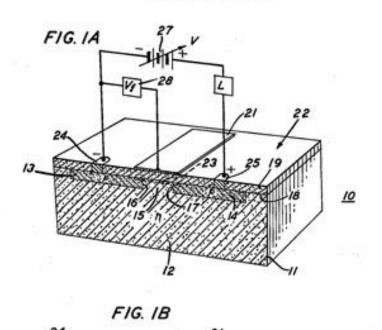

## Primeira Patente do FET 1925 (Teórico)

#### **Julius Edgar Lilienfeld**

J. E. Lilienfeld:

"Method and

apparatus for

controlling electric

current" US patent

1745175 first filed in

Canada on 22nd

October 1925

# Primeira Patente de um FET (1925) (nunca foi construído)

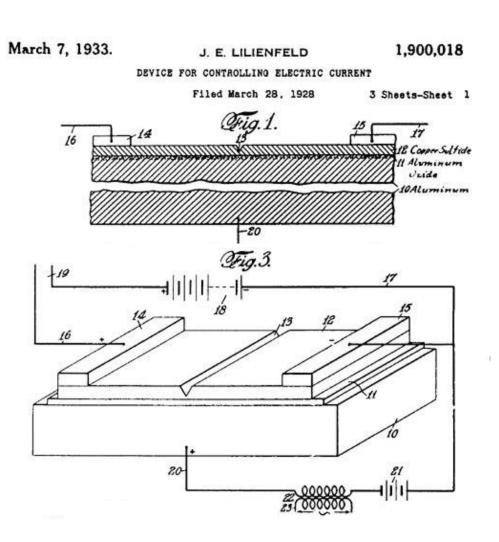

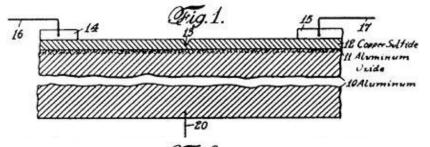

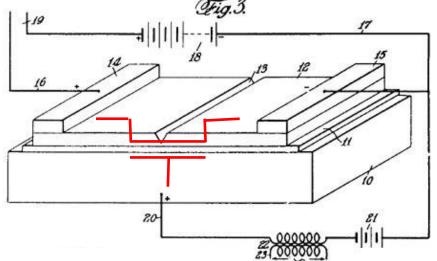

March 7, 1933.

J. E. LILIENFELD

1,900,018

DEVICE FOR CONTROLLING ELECTRIC CURRENT

Filed March 28, 1928

3 Sheets-Sheet 1

### **Julius Edgar Lilienfeld**

J. E. Lilienfeld:

"Method and

apparatus for

controlling electric

current" US patent

1745175 first filed in

Canada on 22nd

October 1925

## Primeira Fabricação de um MOSFET(1960)

#### Metal Oxide Semiconductor (MOS) Field Effect Transistor (FET)

Aug. 27, 1963

DAWON KAHNG

3,102,230

ELECTRIC FIELD CONTROLLED SEMICONDUCTOR DEVICE

Filed May 31, 1960

M. M. (John) Atalla and Dawon

Kahng at Bell Labs achieved the first

successful insulated-gate fieldeffect transistor (MOSFET),

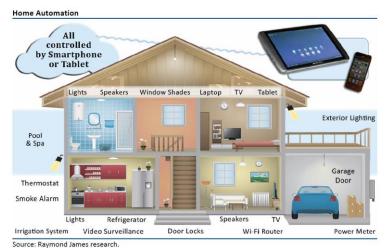

# MOSFET Muitas Aplicações

# MOSFET Muitas Aplicações

Internet of Things (IoT)

**Everything Will Be Connected**

BILLIONS OF WIRELESSLY INTERCONNECTED DEVICES WILL COMMUNICATE DIRECTLY

## Algumas Ideias de Aplicação vieram da Ficção Cientítica

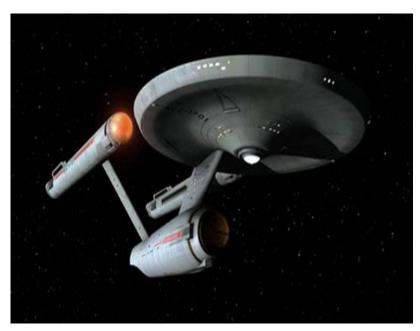

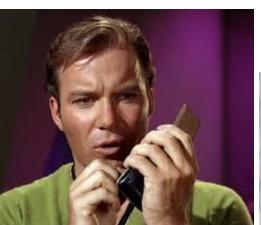

## Jornada nas Estrelas – Star Trek (1966-1969) Da ficção científica para a realidade

https://www.youtube.com/watch?

v=zM3cPMINXho

Enterprise - Star Trek

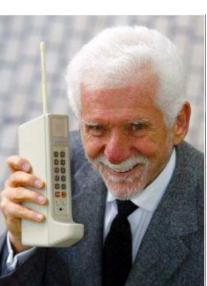

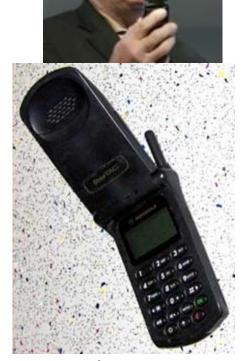

## Telefone Celular

James T. Kirk (1966)

Martin Cooper (1973)

Motorola-StarTAC (1996)

Iphone 7 (2016)

## **Tablets**

## Star trek: The New Generation (1987-1994) Jornada nas Estrelas: A Nova Geração

# Universidade de São Paulo

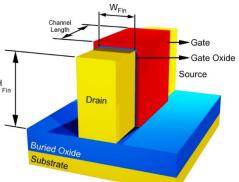

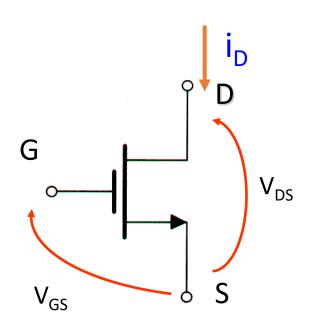

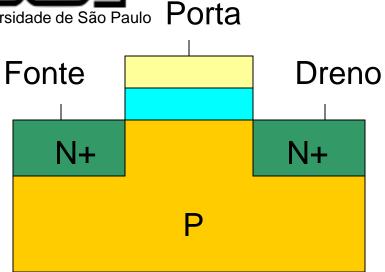

## MOSFET canal N (NMOS)

#### Substrate

## MOSFET canal N (NMOS)

#### Substrate

### (USP/Brasil)

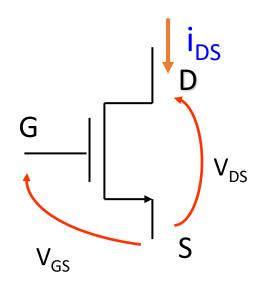

## MOSFET canal N (NMOS)

Porta Universidade de São Paulo

#### Substrate

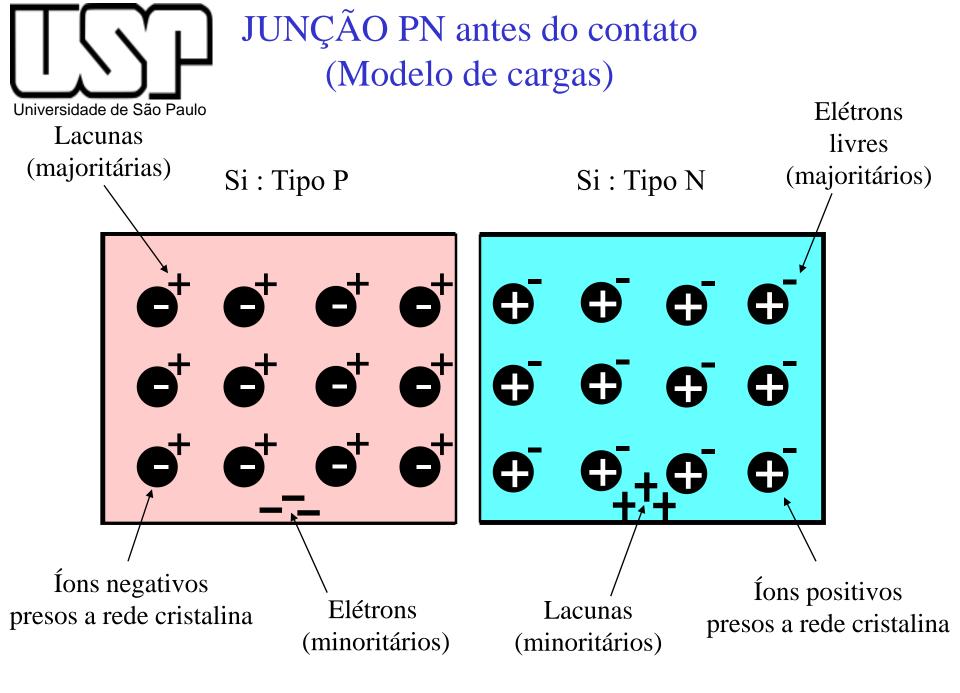

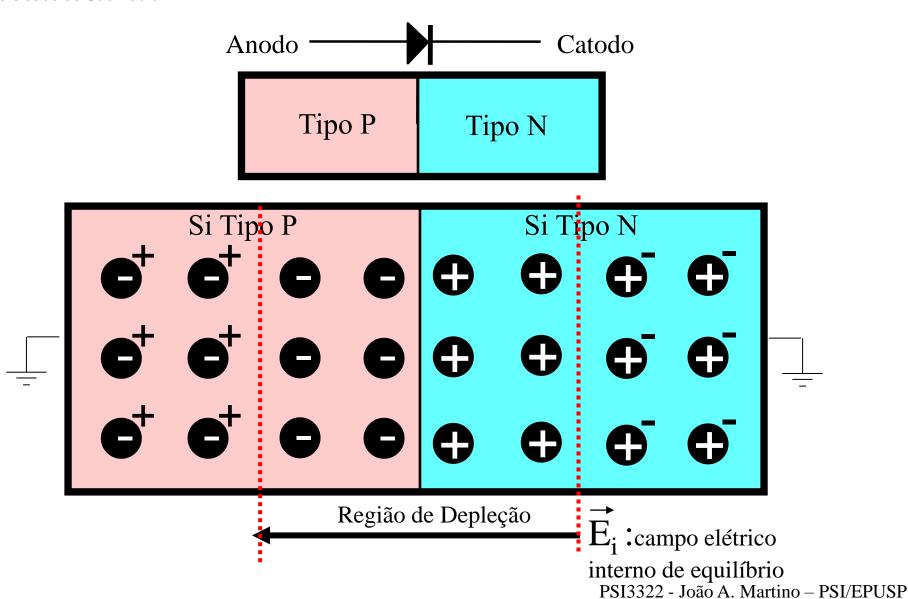

## JUNÇÃO PN em equilíbrio térmico (Modelo de cargas)

# Universidade de São Paulo

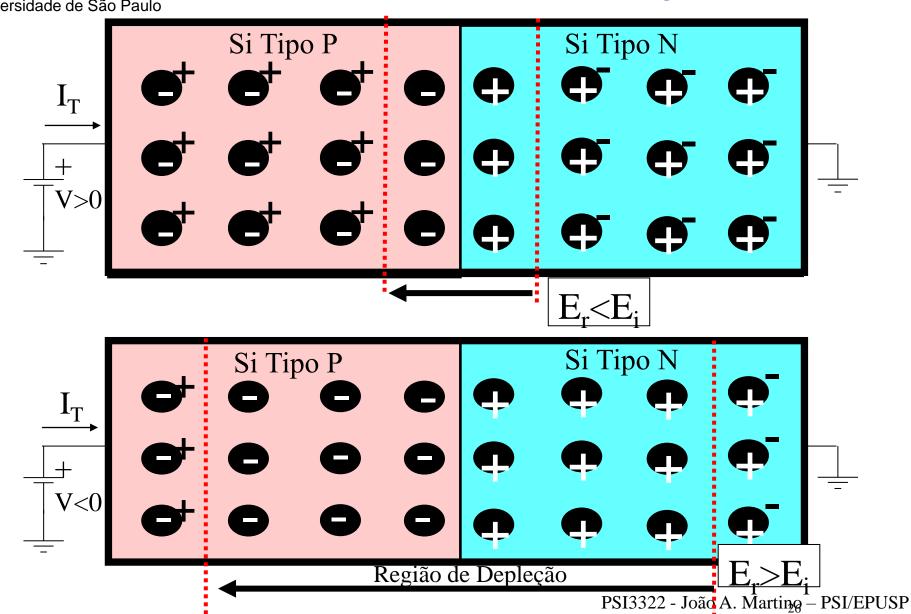

JUNÇÃO PN polarizada diretamente e reversamente (Modelo de cargas)

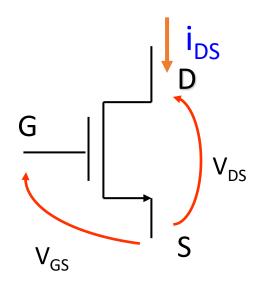

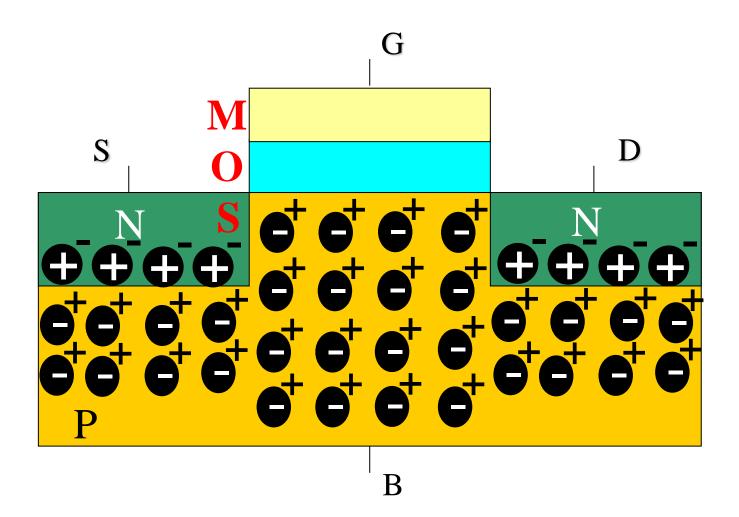

## Transistor NMOS (antes do equilíbrio)

$$V_{GS} = 0 e V_{DS} = 0$$

Desprezando cargas no óxido e diferença de função trabalho entre o metal e o semicondutor

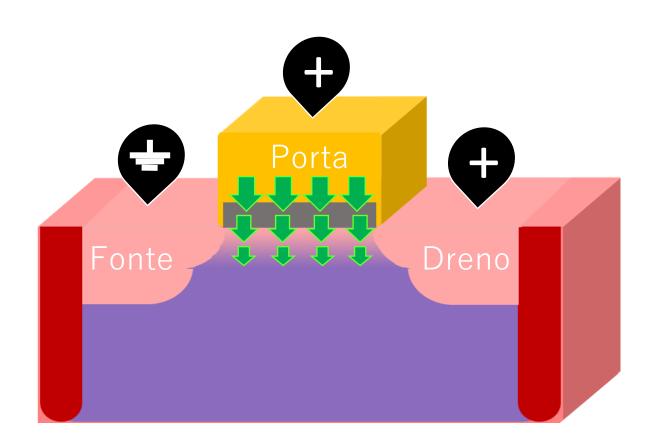

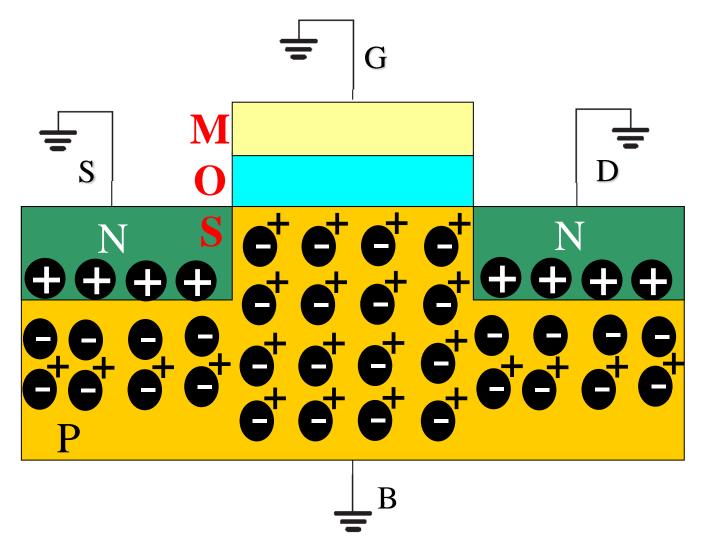

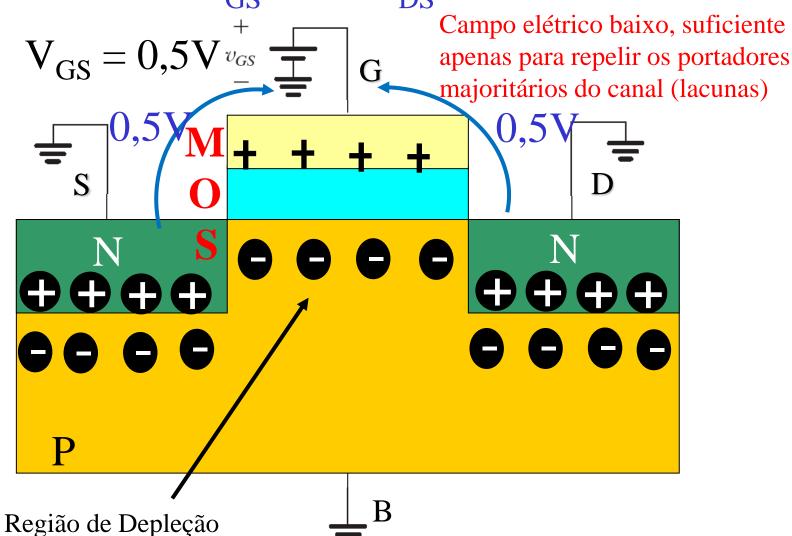

$$V_{GS} > 0 e V_{DS} = 0$$

$$V_{GS} = 0.5V_{-}^{v_{GS}} \stackrel{+}{=} G$$

Campo elétrico baixo, suficiente apenas para repelir os portadores majoritários do canal (lacunas)

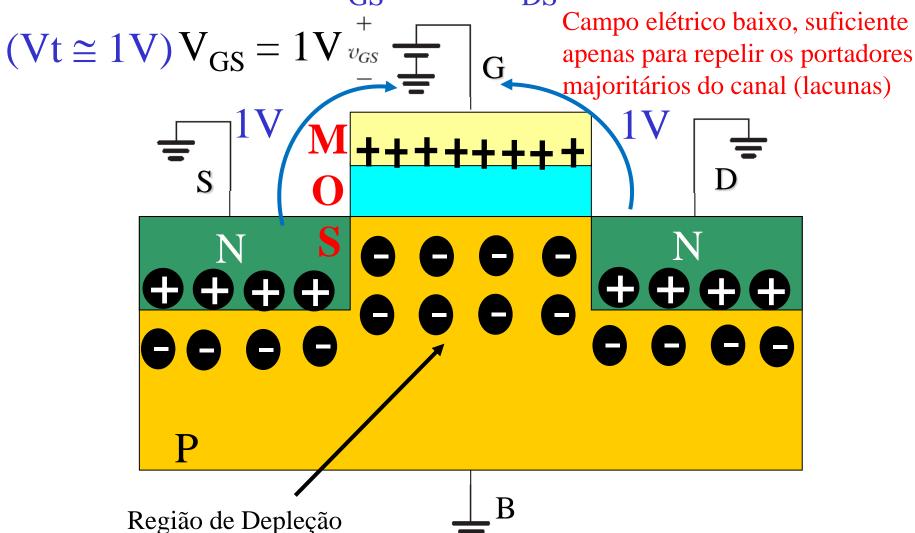

$$V_{GS} > 0 e V_{DS} = 0$$

$$V_{GS} > 0 e V_{DS} = 0$$

# Universidade de São Paulo

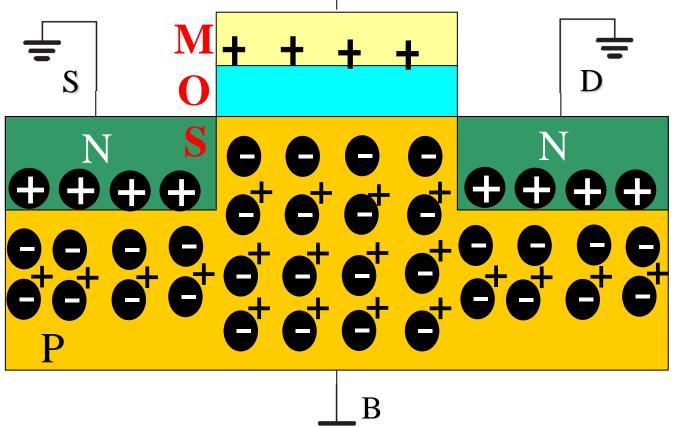

## **Transistor NMOS**

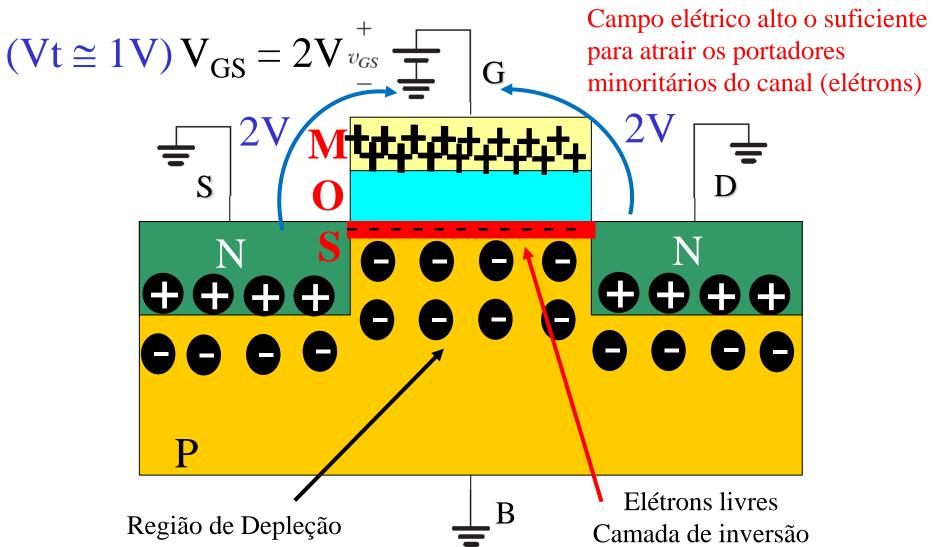

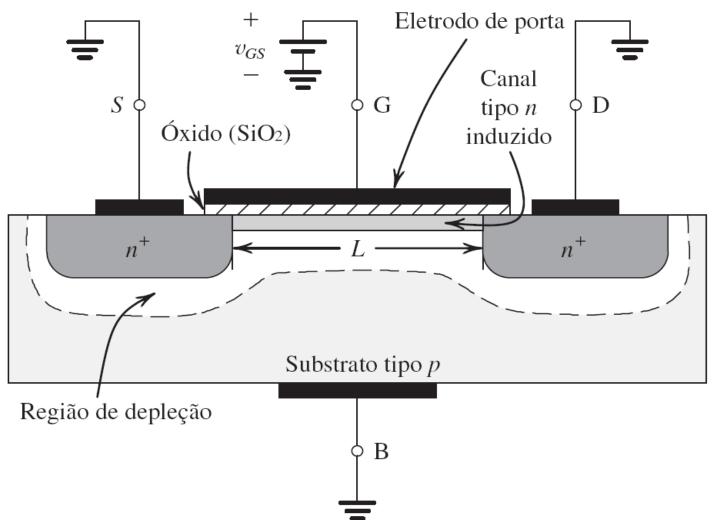

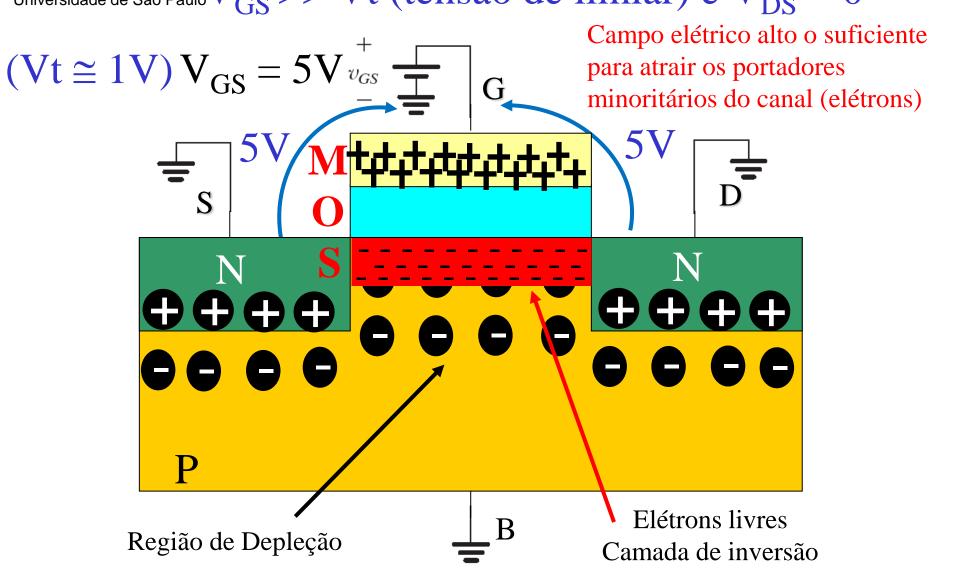

Universidade de São Paulo  $V_{GS} > Vt$  (tensão de limitar) e  $V_{DS} = 0$

# Universidade de São Paulo

## Transistor NMOS

Universidade de São Paulo  $V_{GS} > Vt$  (tensão de limitar) e  $V_{DS} = 0$

##

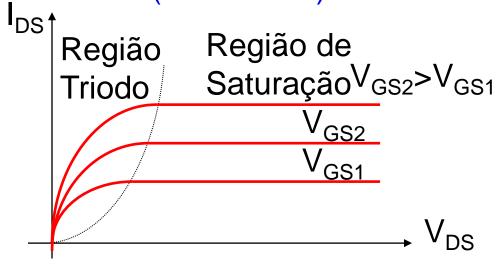

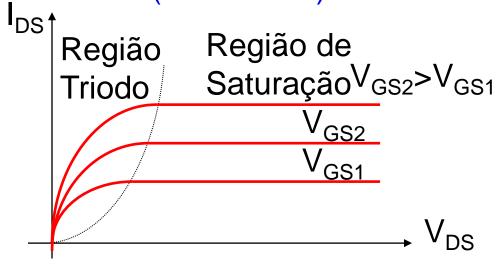

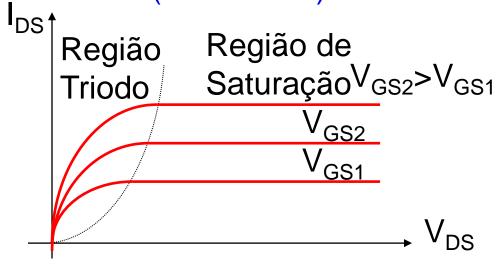

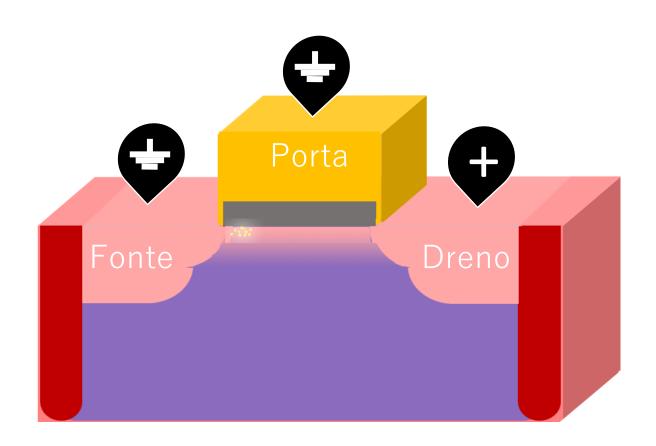

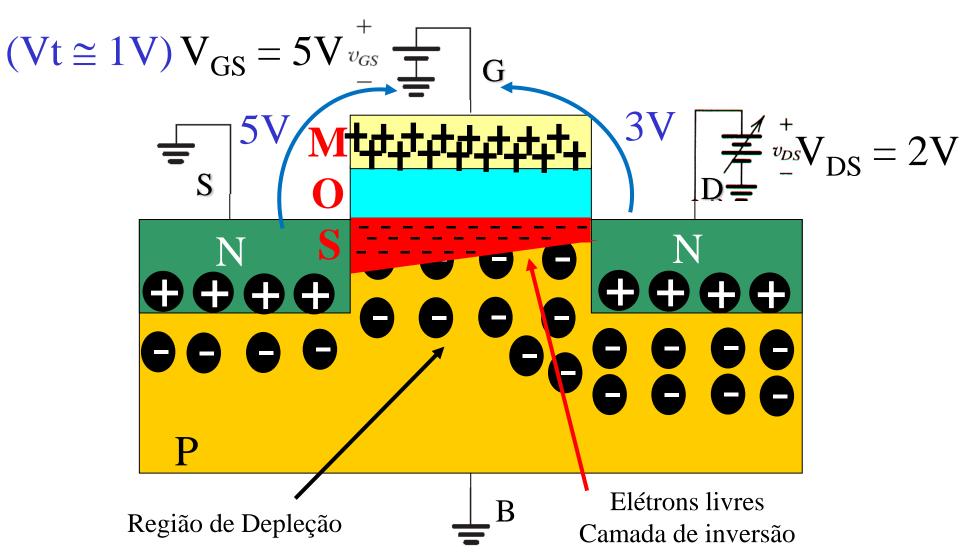

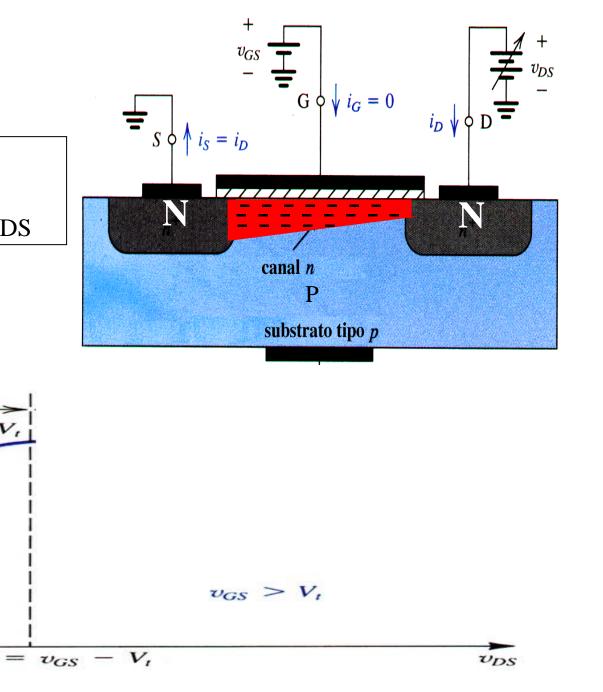

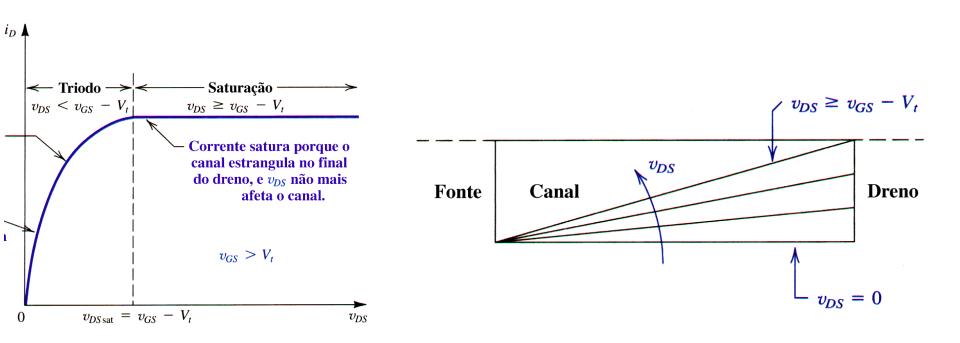

Universidade de São Paulo  $V_{DS} < V_{GS} - Vt$  (Região de tríodo)

# Universidade de São Paulo

## **Transistor NMOS**

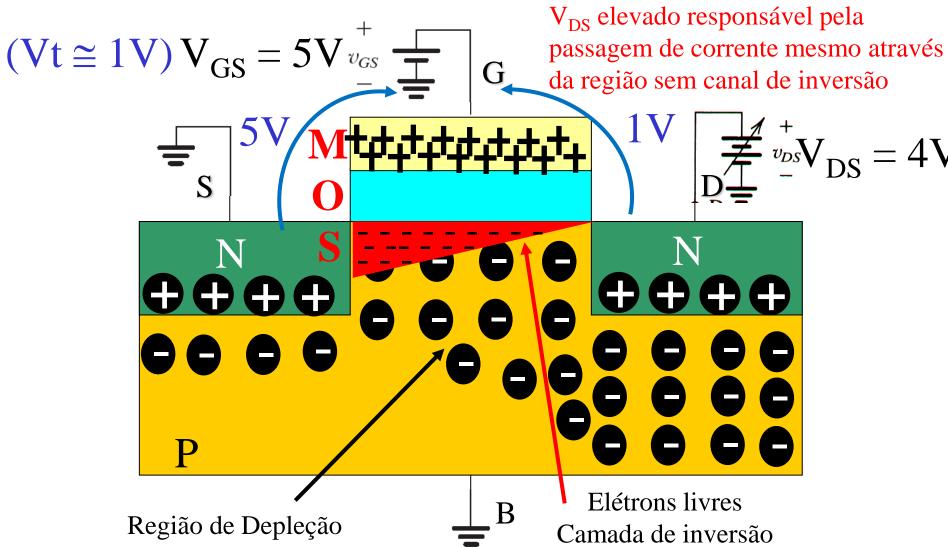

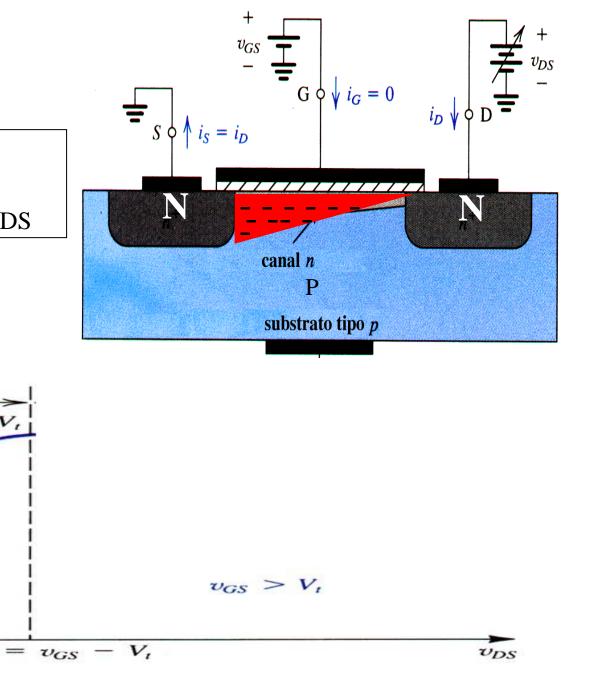

Universidade de São Paulo  $V_{DS} = V_{GS} - Vt \text{ (Triodo/Saturação)}$

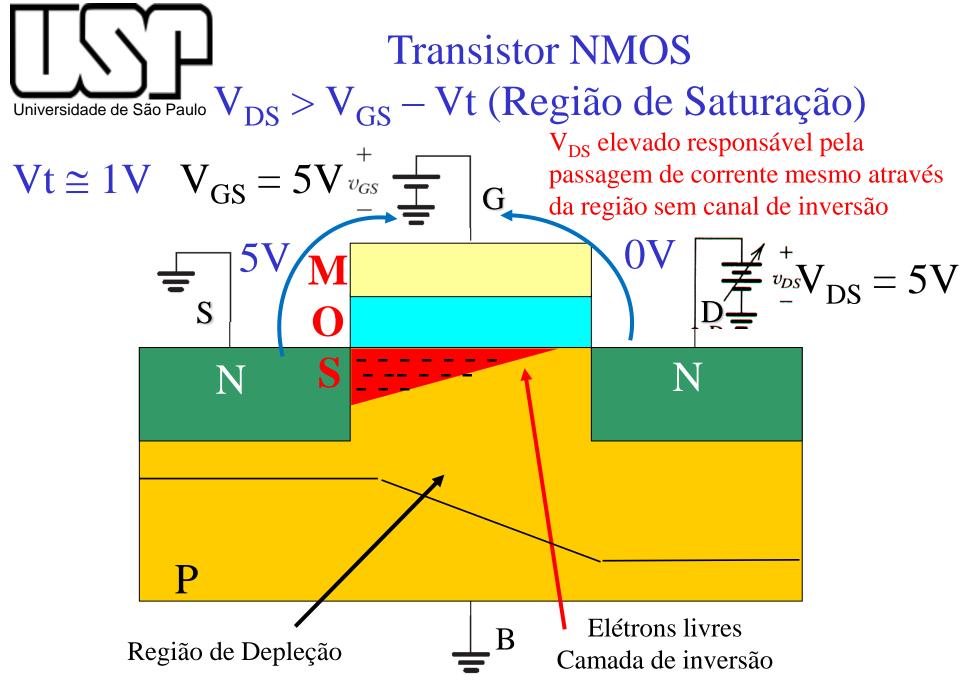

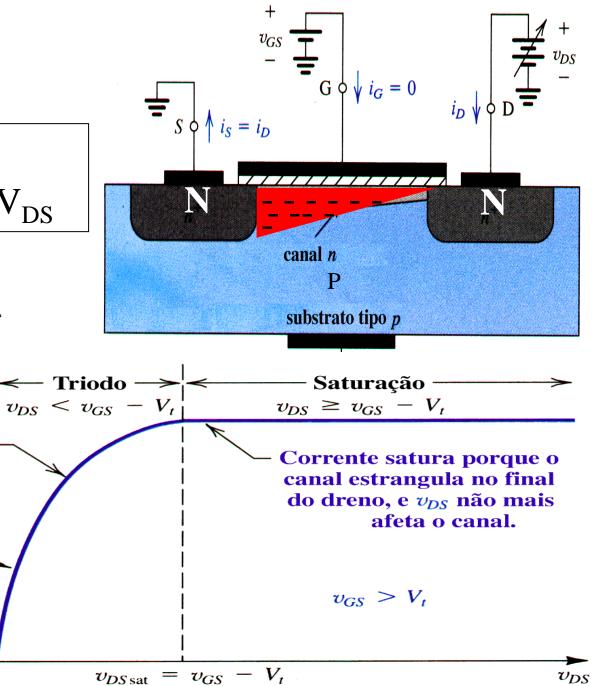

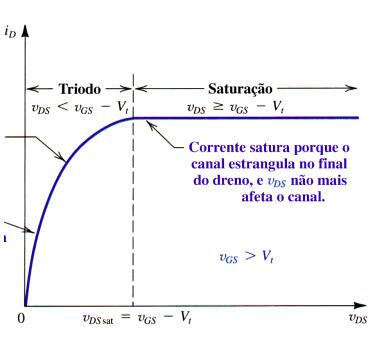

#### Transistor NMOS Universidade de São Paulo $V_{DS} > V_{GS} - Vt \; (Região \; de \; Saturação)$ V<sub>DS</sub> elevado responsável pela $(Vt \cong 1V) V_{GS} = 5V_{v_{GS}}^+ +$ passagem de corrente mesmo através G da região sem canal de inversão Elétrons livres Região de Depleção Camada de inversão

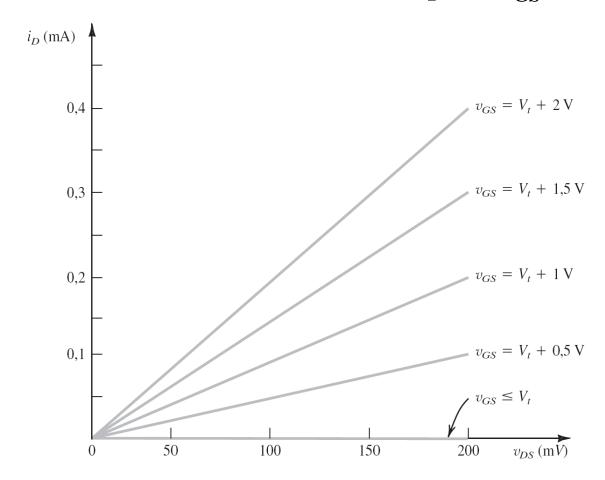

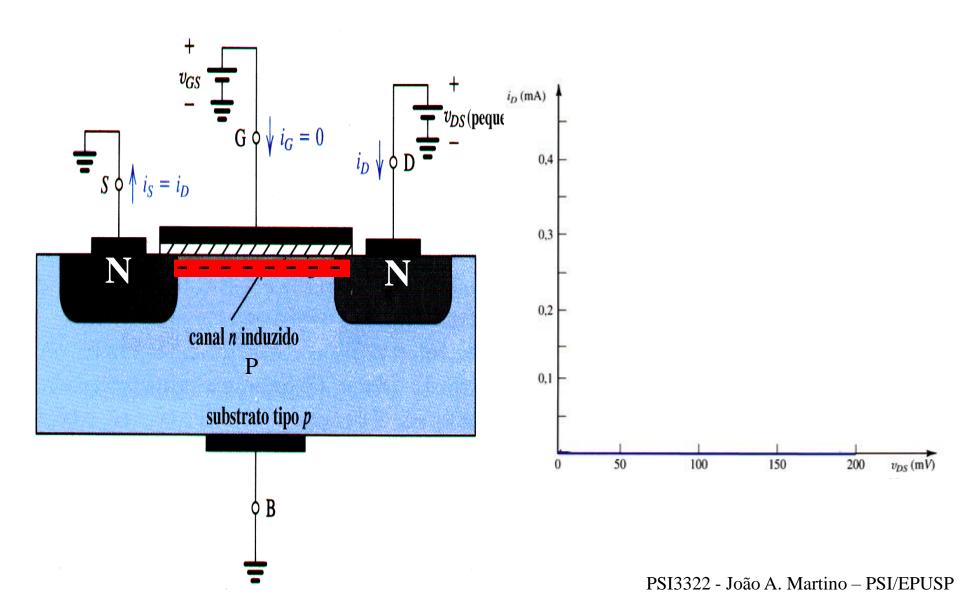

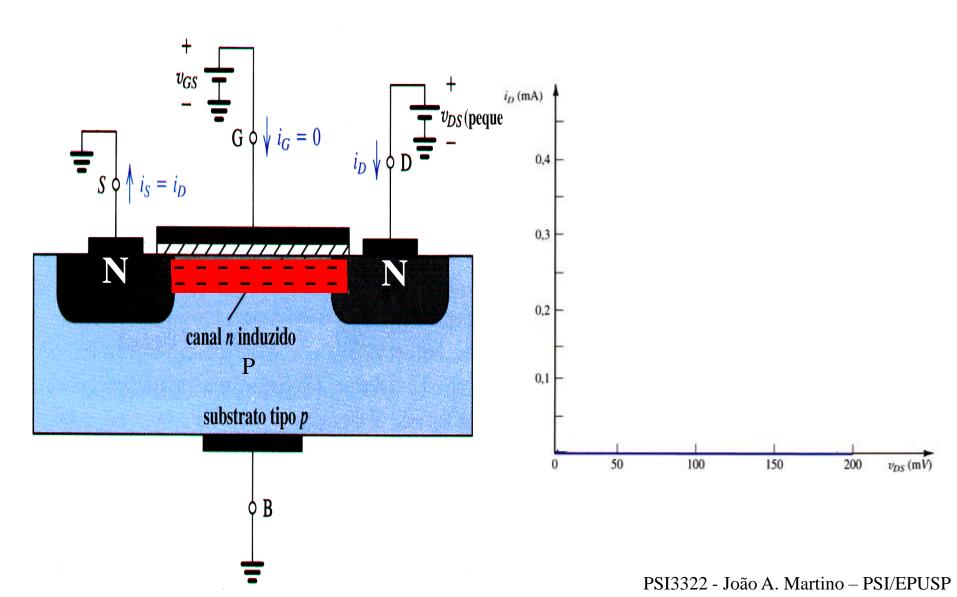

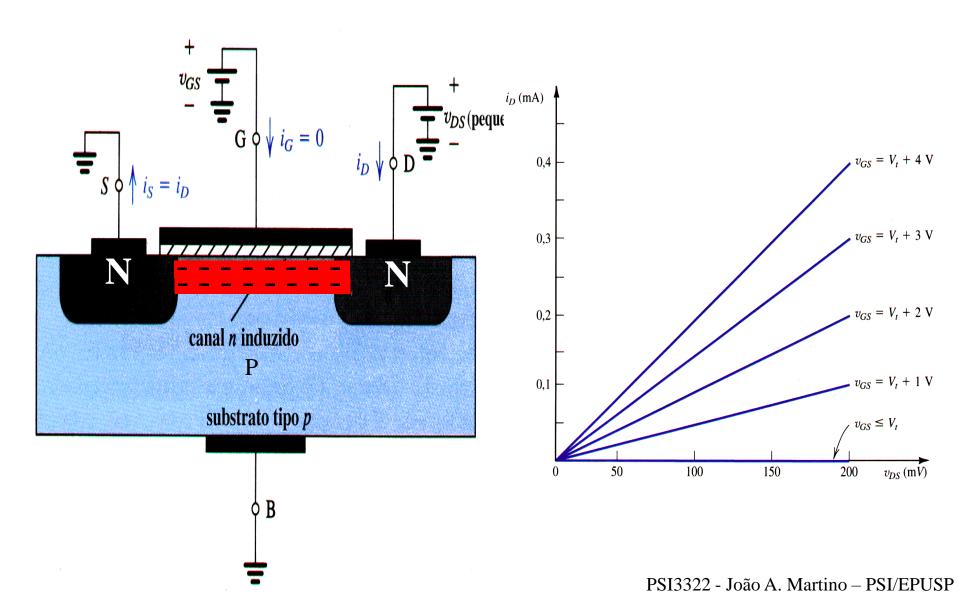

# Aplicando um pequeno valor de $V_{DS}$ (comportamento $\approx$ resistivo)

# Aplicando um pequeno valor de $V_{DS}$ (comportamento $\approx$ resistivo)

## Aplicando um pequeno valor de $V_{DS}$ (comportamento $\approx$ resistivo)

O

UDS

$i_D$

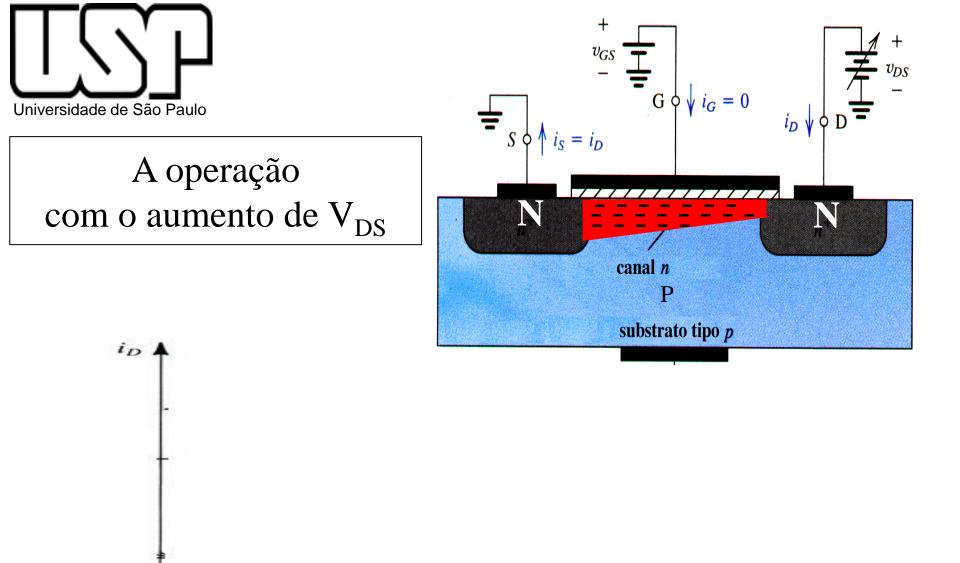

$\begin{array}{c} A \ operação \\ com \ o \ aumento \ de \ V_{DS} \end{array}$

UDS sat

iD I

$\begin{array}{c} A \ operação \\ com \ o \ aumento \ de \ V_{DS} \end{array}$

UDS sat

A operação com o aumento de V<sub>DS</sub>

aumenta com  $v_{DS}$ Praticamente uma linha reta com inclinação proporcional a  $(v_{GS} - V_t)$

A curva entorta porque

a resistência do canal

0

1 513322 - JUAU A. MIAIUIIU - 1 51/LI USP

### Perfil da camada de inversão no canal do transistor nMOS com aumento de V<sub>DS</sub>

### Perfil da camada de inversão no canal do transistor nMOS com aumento de V<sub>DS</sub>

#### Exercício 4.1 (pag. 145)

Para  $V_{DS}$  pequeno  $\rightarrow I_D = K.(V_{GS} - Vt).V_{DS}$ Determine K e a faixa de resistência entre dreno e fonte para  $V_{GS}$  – Vt de 0,5 a 2 V