## SEL0317 – Laboratório de Circuitos Eletrônicos II Tania Regina Tronco

## Prática 6 – Portas Lógicas

MOSFETs, com sua boa transcondutância, capacidade de integração em ultraalta escala e consequentemente grande velocidade devido à maximização da velocidade de resposta, é o componente ideal para confecção de circuitos digitais. Circuitos digitais por sua vez são compostos de milhares de portas lógicas cascateadas, a maior parte feita de poucas topologias básicas que se repetem muitas vezes por digamos, um microprocessador. Uma porta lógica do ponto de vista analógico é um amplificador de alto ganho feito com o intuito de trabalhar na região de saturação ou de corte sempre, com a transição mais breve possível entre os dois estados. Nesta prática serão implementadas algumas topologias simples com MOSFET em lógica NMOS. Lógica NMOS propõe o uso de apenas transistores canal N.

## Implementação

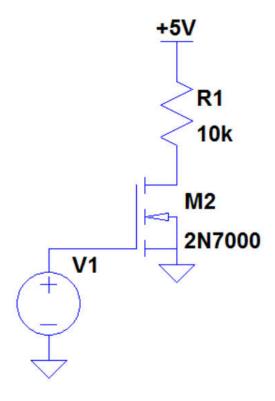

1. Monte o circuito da Figura 1 em bancada. Aplique um sinal DC na porta do transístor com a fonte V1. Varie entre 0 e 5V, medindo a tensão no dreno do transístor. Trace um gráfico da tensão no dreno pela tensão de na porta.

Figura 1 - Inversor NMOS

- 2. Aplique uma onda quadrada de frequência e amplitude adequadas para verificar uma onda quadrada na saída. Sobreponha entrada e saída e copie a tela do osciloscópio.

- 3. Aplique uma onda quadrada de OV a 5V com 1kHz e trace os gráficos de tensão no dreno e corrente no dreno.

- 4. Supondo que a tensão de 0V corresponda a um nível digital 0 e a tensão de 5V a um nível digital 1, monte a tabela verdade do circuito da Figura 1 e discuta como ele se comporta em termos de porta lógica.

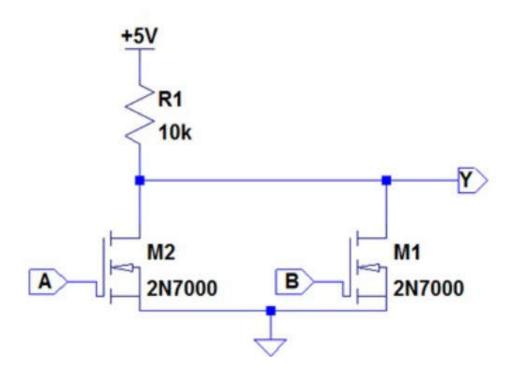

- 5. Monte a porta lógica NMOS da Figura 2 em bancada. Com as tensões de 0 ou 5V nas entradas, descreva o funcionamento desta topologia medindo os níveis de tensão na saída relacionados às tensões de entrada. Monte a tabela verdade desta porta lógica. Qual o nome desta lógica?

Figura 2 - Porta Lógica 2

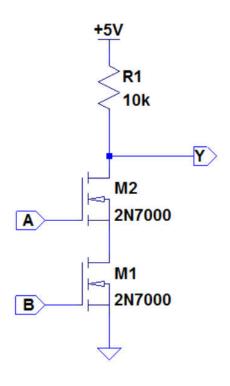

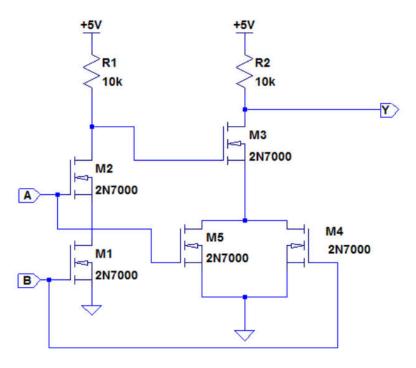

6. Repita o procedimento 5 para as portas lógicas NMOS ilustradas na Figura 3 e Figura 4.

Figura 3 – Porta Lógica 3

Figura 4 – Porta Lógica 4