## SEL 454

Introdução aos Sistemas Digitais

SISTEMAS SEQUENCIAIS BIESTÁVEIS

**Prof. Homero Schiabel**

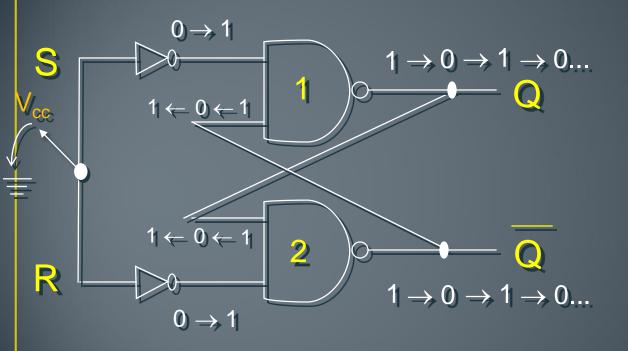

### LATCH RS

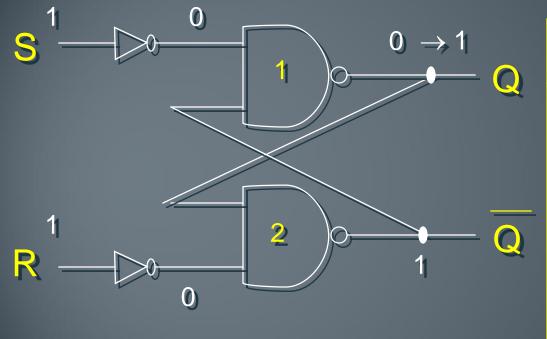

#### Condição Inicial → Q = 0

| S | R | 1   | 2  | Q | Q   |

|---|---|-----|----|---|-----|

| 0 | 0 | 11  | 01 | 0 | 1   |

| 0 | 1 | 11  | 00 | 0 | 1   |

| 1 | 0 | 0 1 | 01 | 1 | 1 * |

|   |   | 0 1 | 11 | 1 | 0   |

| 1 | 1 | 01  | 00 | 1 | 1   |

|   |   | 0 1 | 10 | 1 | 1** |

<sup>\*</sup> Estado instável

<sup>\*\* &</sup>quot;Incompatibilidade" (Est. "proibido")

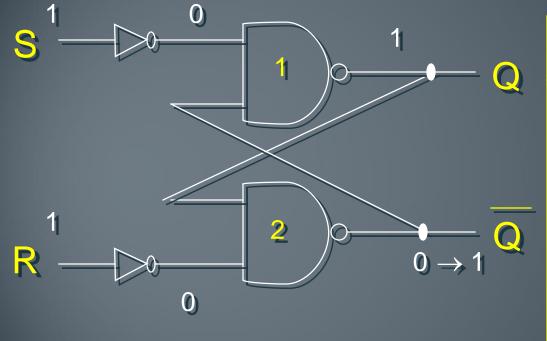

#### Condição Inicial → Q = 1

| S  | R | 1  | 2  | Q | Q   |

|----|---|----|----|---|-----|

| 0  | 0 | 10 | 11 | 1 | 0   |

| 0  | 1 | 10 | 10 | 1 | 1 * |

|    |   | 11 | 10 | 0 | 1   |

| 1  | 0 | 00 | 11 | 1 | 0   |

| 1_ | 1 | 00 | 10 | 1 | 1   |

|    |   |    | 10 | 1 | 1** |

<sup>\*</sup> Estado instável

<sup>\*\* &</sup>quot;Incompatibilidade" (Est. "proibido")

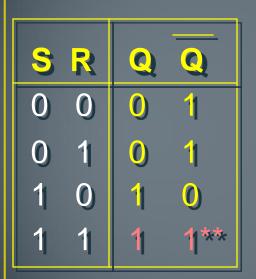

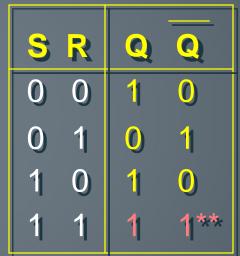

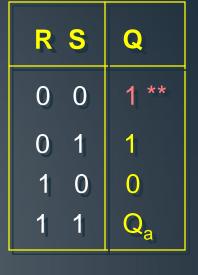

#### Tabela da verdade:

$$Q = 0$$

$$Q = 1$$

#### Condição de memória!

\*\* "Incompatibilidade" (Est. "proibido")

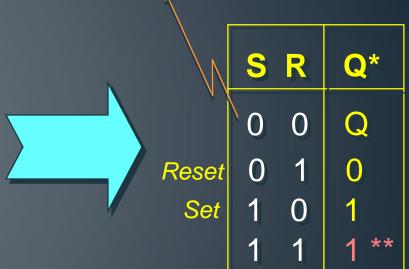

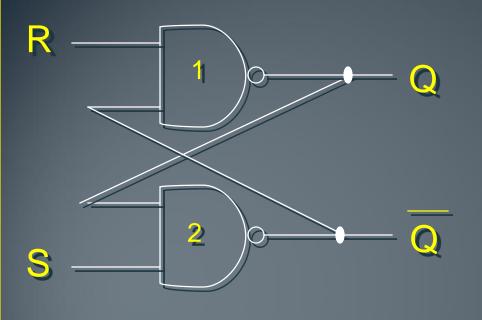

# Mas... Por que "Estado proibido" (S=R=1)?

#### Condição de memória

| S | R | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\ |  |

|---|---|----------------------------------------|--|

| 0 | 0 | Q                                      |  |

| 0 | 1 | 0                                      |  |

| 1 | 0 | 1                                      |  |

| 1 | 1 | 1 **                                   |  |

\*\* "Incompatibilidade" (Est. "proibido")

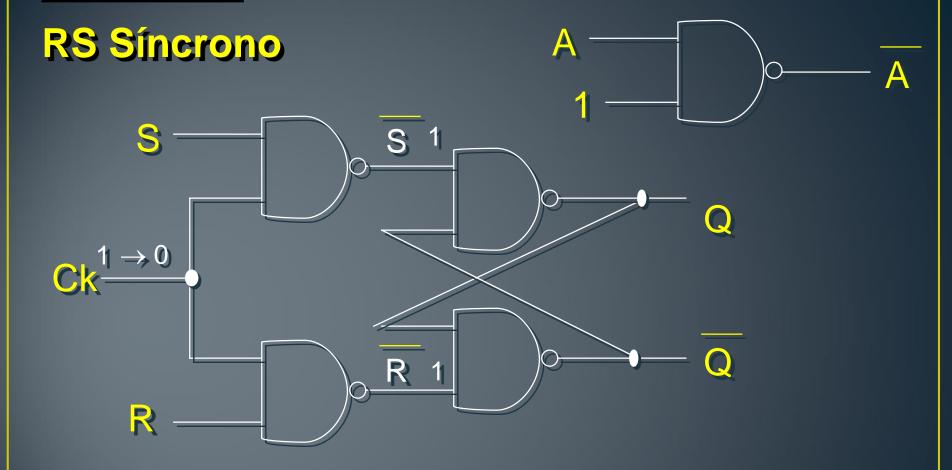

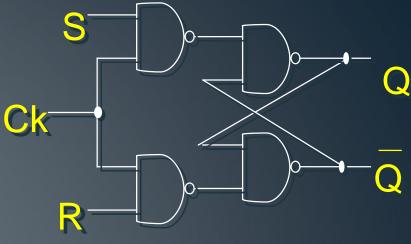

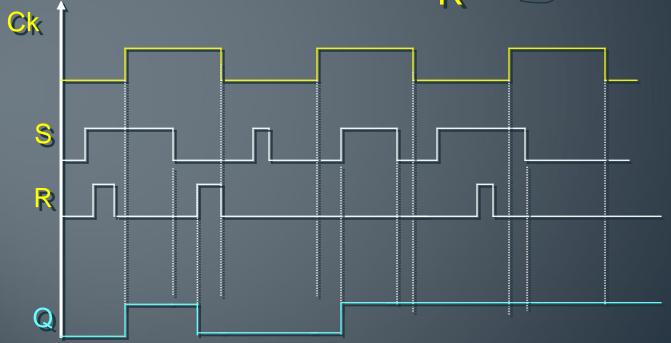

- Para Ck=0 → Q e Q não "sentirão" eventuais variações nas entradas

- Para Ck=1 → funcionamento normal (portas de entrada habilitadas)

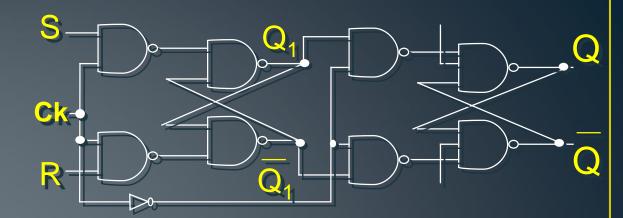

#### **RS Síncrono**

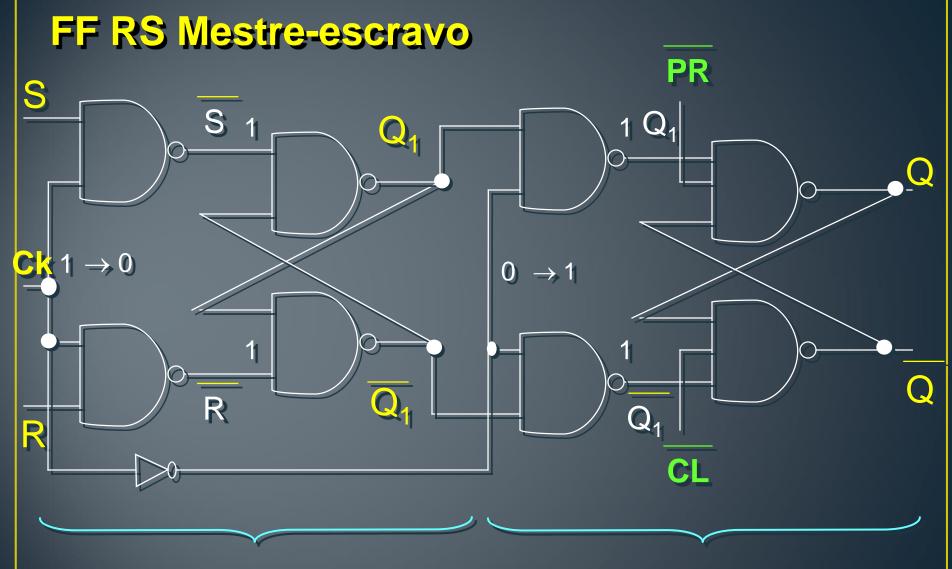

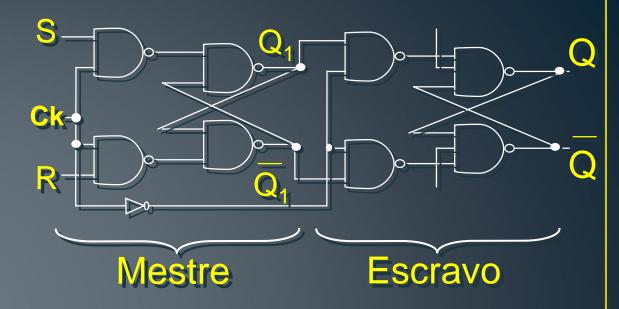

Mestre

Escravo

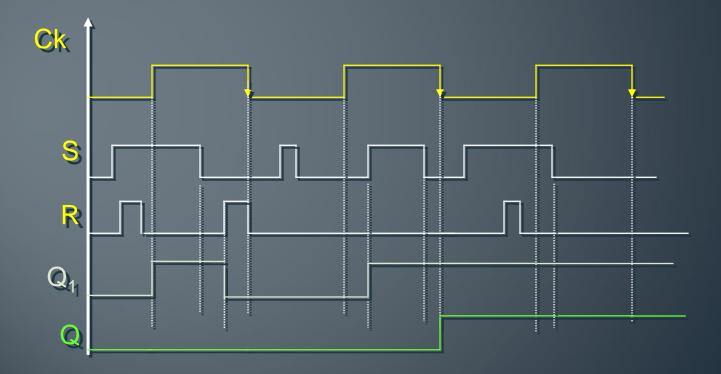

- Ck=1 → Q₁ e Q₁ respondem às variações de S e R (circuito Mestre habilitado) → entradas do circuito Escravo: desabilitadas → Q e Q = ctes)

- Ck=1→0 → Q₁ e Q₁ passam adiante (circuito Escravo habilitado) e podem afetar Q e Q → entradas do circuito Mestre: desabilitadas

- $Ck=0 \rightarrow Q_1 e \overline{Q}_1 = ctes \rightarrow Q e \overline{Q} = ctes$

Ck

Controle

Estabilidade ?

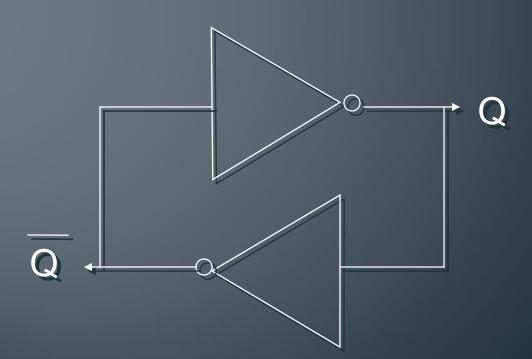

| R | 1 | Q        |

|---|---|----------|

| S | 2 | <u>Q</u> |

| R: | S | Q    |

|----|---|------|

| 0  | 0 | Qa   |

| 0  | 1 | 1    |

| 1  | 0 | 0    |

| 1  | 1 | 1 ** |