# **INTRODUCTION - FACTORY PROCESSES**

RIT is supporting three different CMOS process technologies. The older p-well CMOS has been phased out. The SMFL-CMOS process is used for standard 5 Volt Digital and Analog integrated circuits. This is the technology of choice for teaching circuit design and fabricating CMOS circuits at RIT. The SUB-CMOS and ADV-CMOS processes are intended to introduce our students to process technology that is close to industry state-of-the-art. These processes are used to build test structures and develop new technologies at RIT.

RIT p-well CMOS (1995) RIT SMFL-CMOS (2004) RIT Subµ-CMOS (2000) RIT Advanced-CMOS (2003)

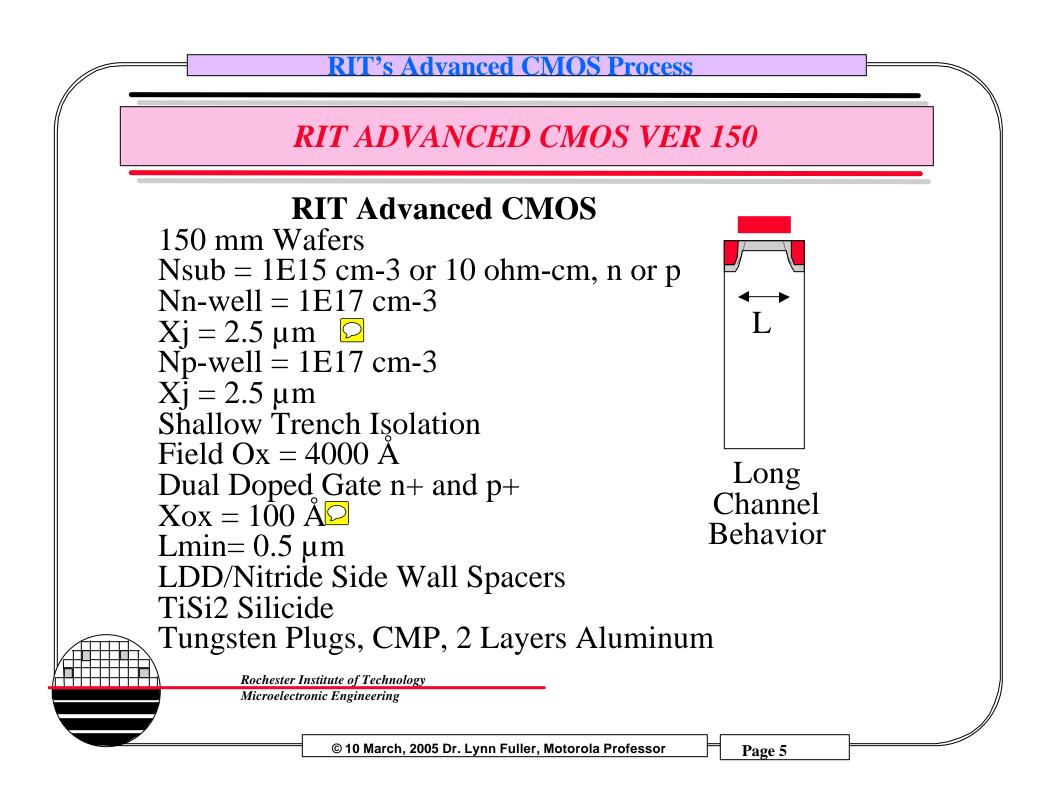

$\lambda = 4 \ \mu m$  $\lambda = 1 \,\mu m$  Lmin = 2  $\mu m$  $\lambda = 0.25 \,\mu m$

$Lmin = 8 \mu m$  $\lambda = 0.5 \,\mu m$  Lmin = 1.0  $\mu m$  $Lmin = 0.5 \mu m$

**Rochester Institute of Technology** Microelectronic Engineering © 10 March, 2005 Dr. Lynn Fuller, Motorola Professor Page 3

## **INTRODUCTION**

### **Advanced Processes:**

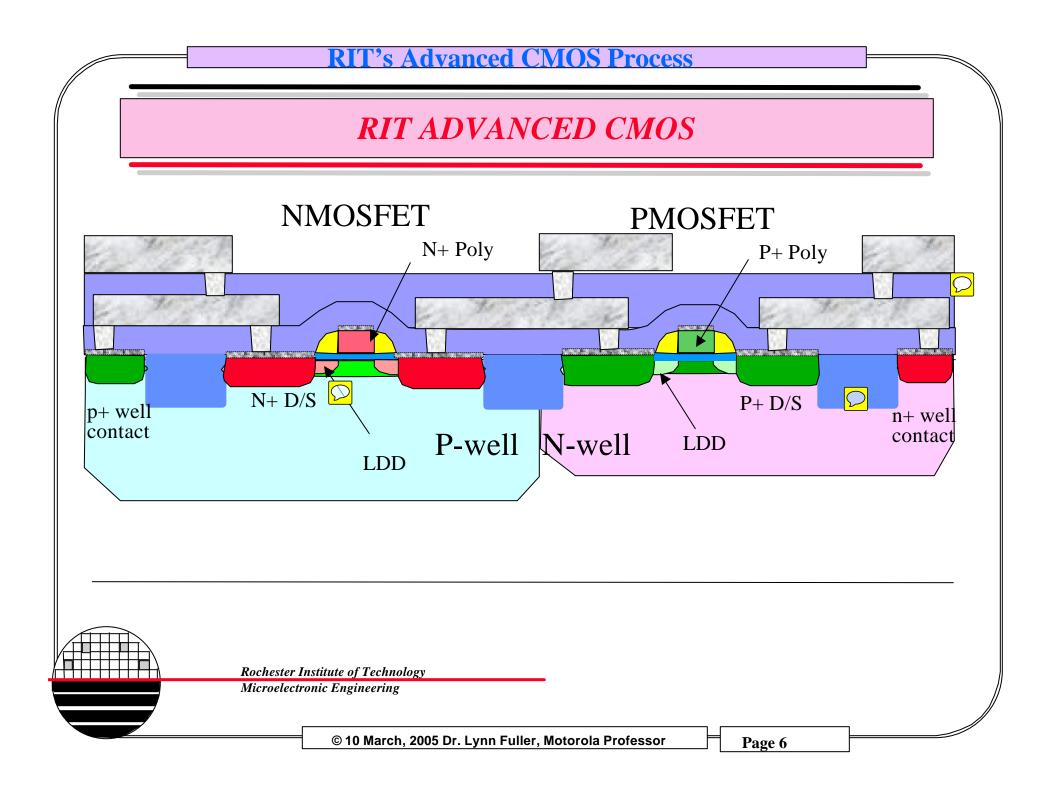

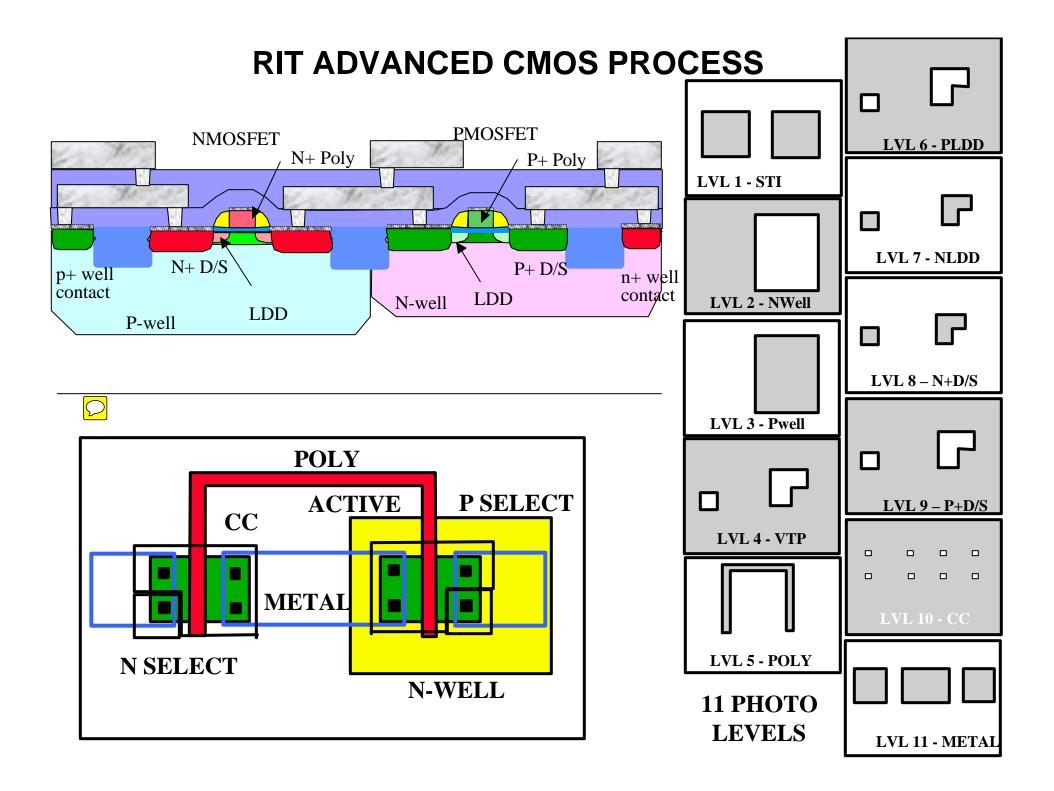

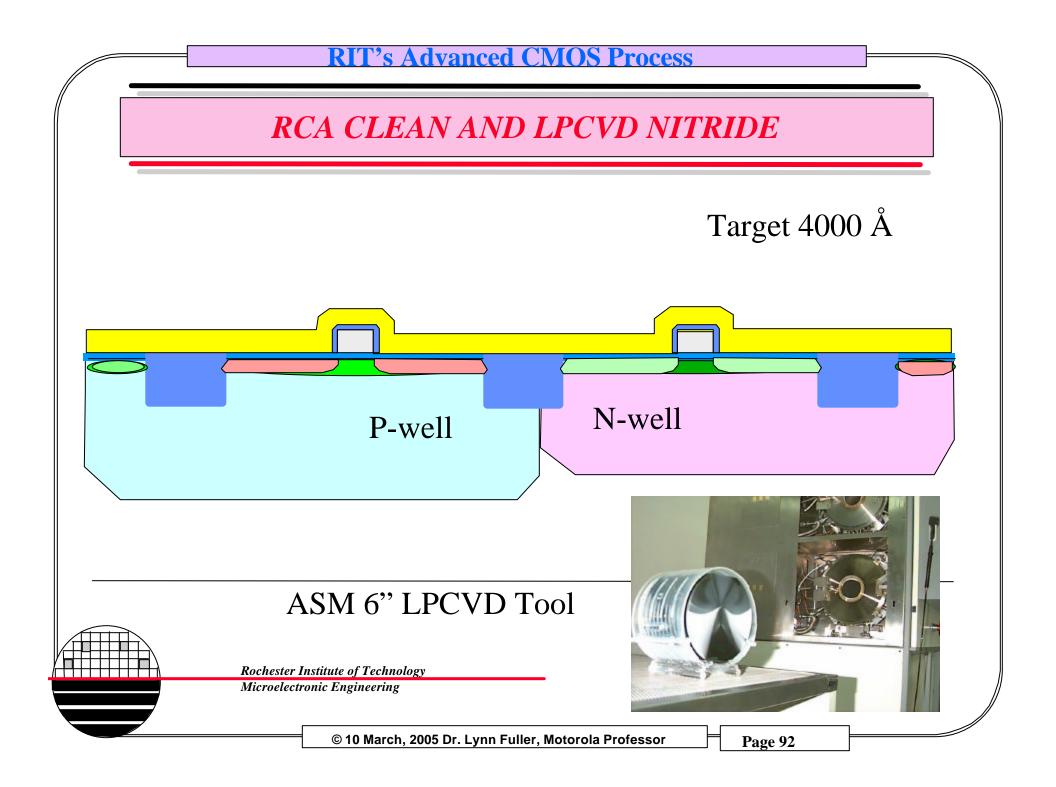

Shallow Trench Etch with Endpoint Trench PECVD TEOS fill and CMP Silicide TiSi2, Recipes for Rapid Thermal Processor Dual Doped Gate, Ion Implant and Mask Details Anisotropic Poly Etch 100 Å Gate Oxide Recipe with N2O Nitride Spacer, New Anisotropic Nitride Etch Aluminum Metal, W Plags Deposition, CMP of Oxide New Test Chip New Masks, Canon and ASML New Stepper Jobs, Canon and ASML Create MESA Process, Products, Instructions, Parameters

Rochester Institute of Technology

Microelectronic Engineering

## ASML 5500/90 STEPPER

KrF Excimer Laser Steppe  $\lambda = 248 \text{ nm}$ NA = 0.52,  $\sigma = 0.6$ Resolution = 0.7  $\lambda$  / NA = ~0.3  $\mu$ m 20 x 20 mm Field Size Depth of Focus =  $k_2 \lambda/(NA)^2 \sim 0.64 \mu$ m 6''x6'' Masks

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

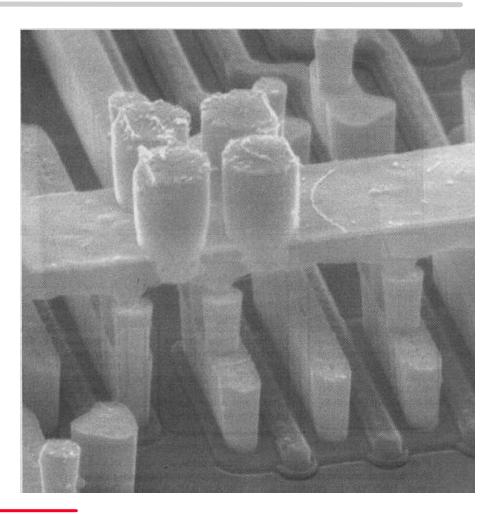

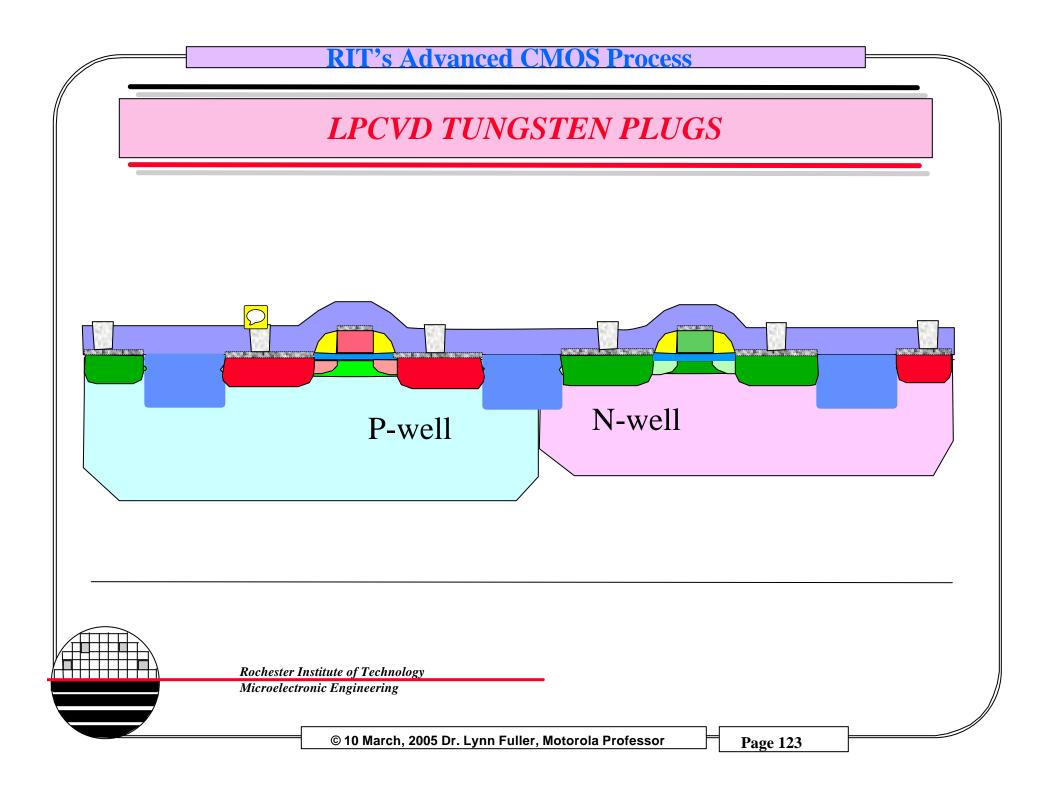

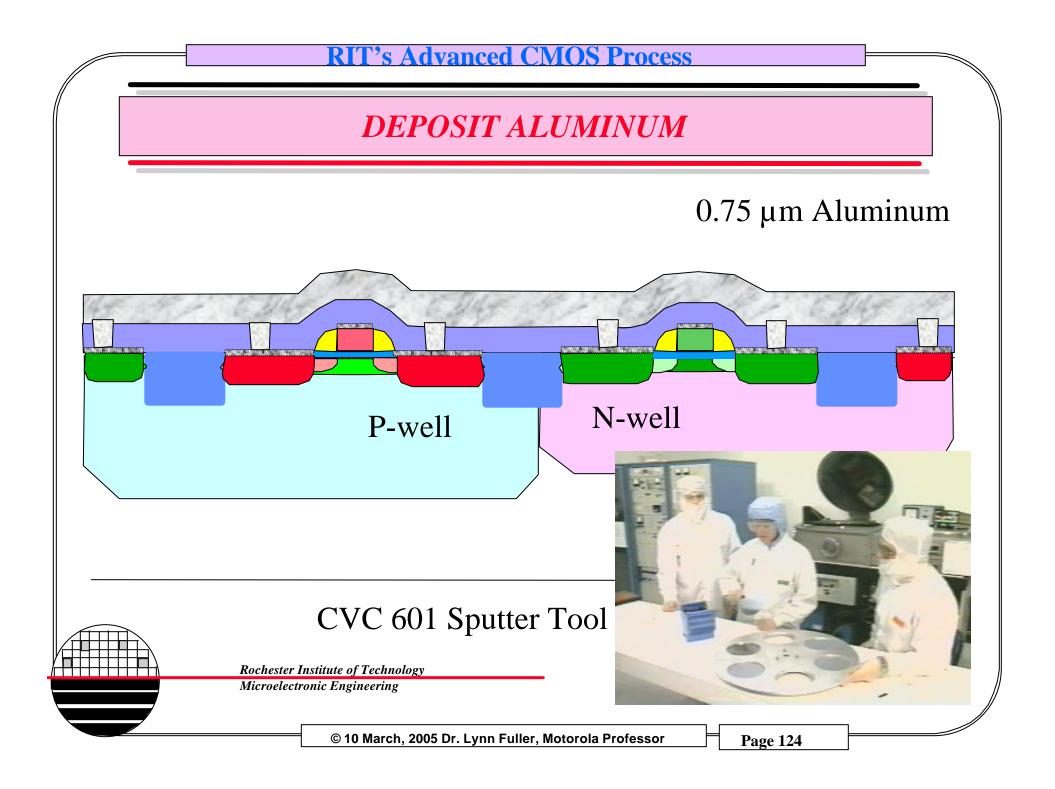

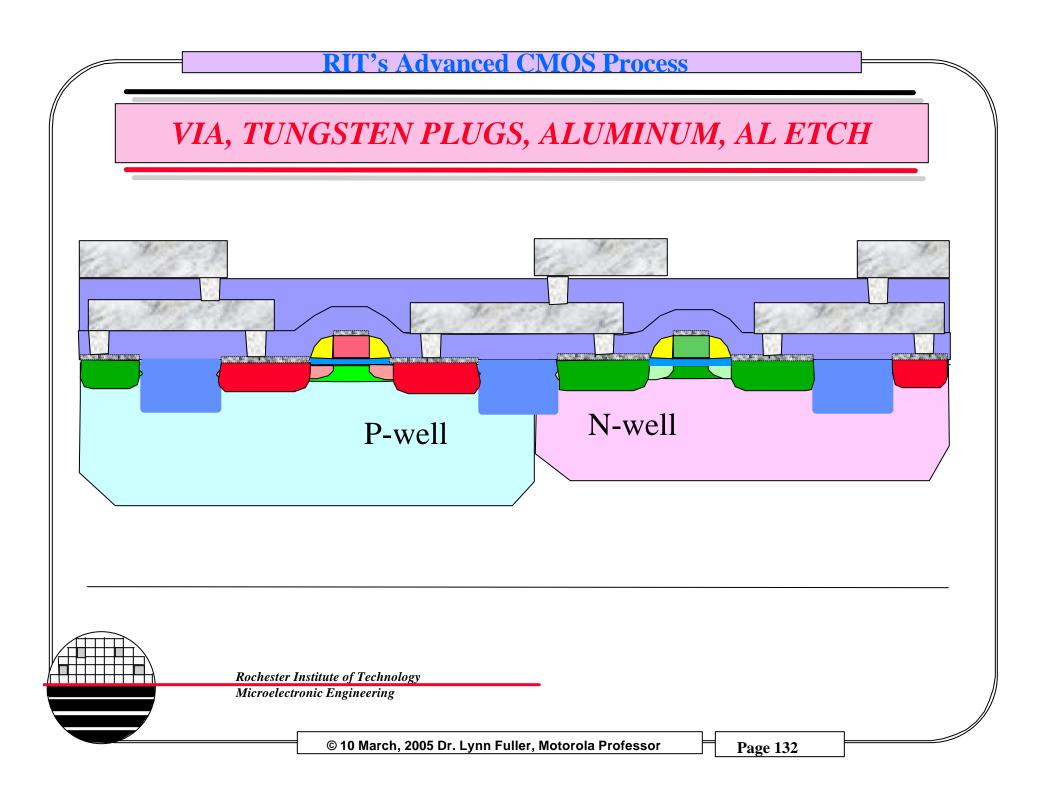

MULTI- LAYER ALUMINUM, W PLUGS, CMP, DAMASCENE OF LOCAL W INERCONNECT

Multi-layer aluminum interconnect with tungsten plugs, CMP, and damascene of local tungst interconnect.

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

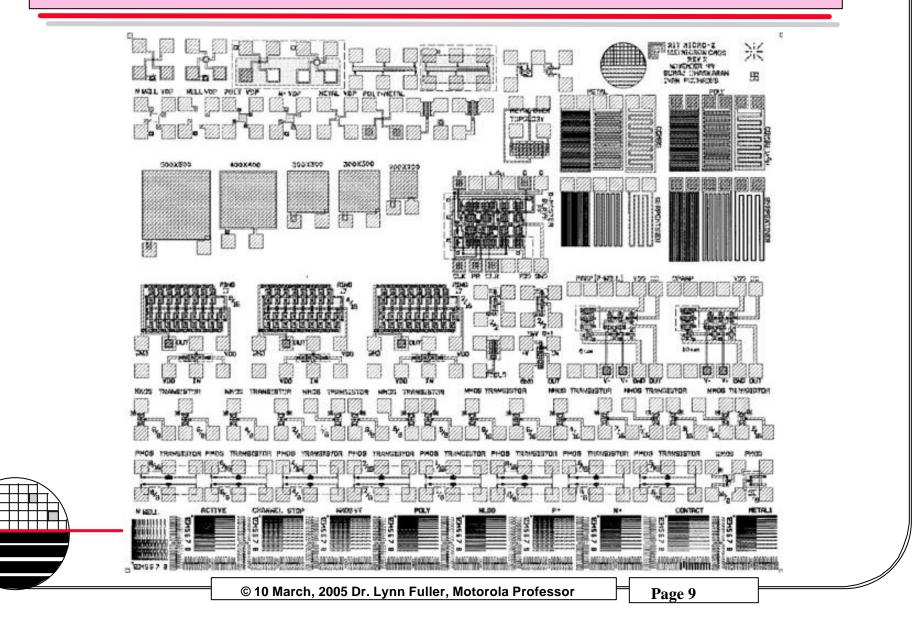

### **ADVANCED CMOS TEST STRUCTURES**

## MASK ORDER

|                     | Semiconductor                                                     | & Micros                  | ystems Fabrication L                                                                                                                                              |                                                                                            |                                                                     | -                                    | Order R      | equest     |  |  |

|---------------------|-------------------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------|--------------------------------------|--------------|------------|--|--|

|                     | Name                                                              |                           | Customer In                                                                                                                                                       |                                                                                            |                                                                     |                                      |              |            |  |  |

|                     | Company<br>Department<br>Street Address                           | 4                         | Dr. Lynn Fulle<br>Mxroel                                                                                                                                          | ectro                                                                                      | nic E                                                               | ngine                                | Ining        | 5          |  |  |

|                     | City, State and<br>Phone Number<br>Project Code<br>E-mail Address | Zip Cod                   | e (                                                                                                                                                               | <u>،</u> `                                                                                 | - 475                                                               | -20                                  | 35           |            |  |  |

|                     | Order Date<br>Order Due Date                                      |                           | 1, 103<br>Mask by 4181                                                                                                                                            | arch 31,<br>03, 2                                                                          |                                                                     | sk by                                | 4/15         | 103        |  |  |

|                     | SEE PAGE 2<br>Design Name<br>Number of Desi                       |                           | Mask Infor<br>NSTRUCTIONS C<br>adv cm/8<br>s in Lavout                                                                                                            | N CRE                                                                                      | ATING                                                               | YOUR                                 | GDS          | FILE       |  |  |

|                     | Number of Masl<br>Cell Layout Size                                | k Levels                  |                                                                                                                                                                   |                                                                                            |                                                                     | Y:<br>Y:                             | µm<br>µm     |            |  |  |

|                     | Fracture Resolu<br>Scale Factor<br>Orientation                    | tion                      | <                                                                                                                                                                 | 10.5µm                                                                                     |                                                                     | р<br>П                               | m            |            |  |  |

|                     | Rotation<br>Plate Size<br>Number of Leve<br>Array                 | ls on Pla                 | te                                                                                                                                                                | None<br>5 inch sq<br>None<br>Array v                                                       |                                                                     | □<br>ws and                          | colu         | mns        |  |  |

|                     |                                                                   |                           |                                                                                                                                                                   |                                                                                            |                                                                     |                                      |              |            |  |  |

|                     | -                                                                 |                           | Details for Each                                                                                                                                                  | Mask La                                                                                    | ver                                                                 |                                      |              |            |  |  |

|                     | Mask Level<br>Name                                                | Mask<br>Level             | Details for Each<br>Design Layer<br>Name(s)                                                                                                                       | Mask La<br>Design<br>Layer<br>#(`s)                                                        |                                                                     | Field<br>Type                        | Bias<br>(µm) | CD<br>(µm) |  |  |

|                     |                                                                   | Level                     | Design Layer                                                                                                                                                      | Design<br>Layer                                                                            | Boolean                                                             | 10.000                               | (µm)         |            |  |  |

|                     | Name                                                              | Level                     | Design Layer<br>Name(s)<br>Active - avea, I<br>(INV) N-well + C<br>P-well + C                                                                                     | Design<br>Layer<br>#(`s)<br>3                                                              | Boolean<br>Function<br>OR<br>OR<br>OR                               | Type                                 | (µm)         |            |  |  |

|                     | Name<br>STI<br>NWELL                                              | Level<br>#<br>/           | Design Layer<br>Name(s)<br>Active - avea, I<br>(INV) N-well + C<br>P-well + C<br>N-well - I<br>Active avea - C                                                    | Design<br>Layer<br>#(`s)<br>3<br>51<br>52                                                  | Boolean<br>Function<br>OR<br>OR<br>OR<br>OR<br>OR                   | Type                                 | (µm)         |            |  |  |

|                     | Name<br>STI<br>NWELL<br>PWELL                                     | Level<br>#<br>/<br>2      | Design Layer<br>Name(s)<br>Active - avea, I<br>(INV) N-well + C<br>P-will + C<br>N-will + C<br>Active - avea - C<br>(INV) N-well + I<br>N-implent + C             | Design<br>Layer<br>#('s)<br>3<br>51<br>52<br>7<br>53<br>1<br>53<br>1<br>54                 | Boolean<br>Function<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR | Type                                 | (µm)         |            |  |  |

|                     | Name<br>STI<br>NWELL                                              | Level<br>#<br>/<br>2<br>3 | Design Layer<br>Name(s)<br>Active - avea, I<br>(INV) N-well - C<br>P-will, C<br>N-will, T<br>Active avea. C<br>(INV) N-well, I                                    | Design<br>Layer<br>#('s)<br>3<br>51<br>52<br>7<br>53<br>1                                  | Boolean<br>Function<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR             | Type<br>Clay<br>Davk                 | (µm)         |            |  |  |

| Rochester Institute | Name<br>STI<br>NWELL<br>PWELL                                     | Level<br>#<br>2<br>3<br>4 | Design Layer<br>Name(s)<br>Active - avea, I<br>(INV) N-well & C<br>P-well & C<br>N-well & T<br>Active avea. C<br>(INV) N-well & T<br>N-impleach &<br>P-impleach & | Design<br>Layer<br>#('s)<br>3<br>51<br>52<br>7<br>53<br>1<br>53<br>1<br>54<br>5<br>5<br>55 | Boolean<br>Function<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR<br>OR       | Type<br>Clav<br>Dark<br>Dark<br>Dark | (µm)         | (µm)       |  |  |

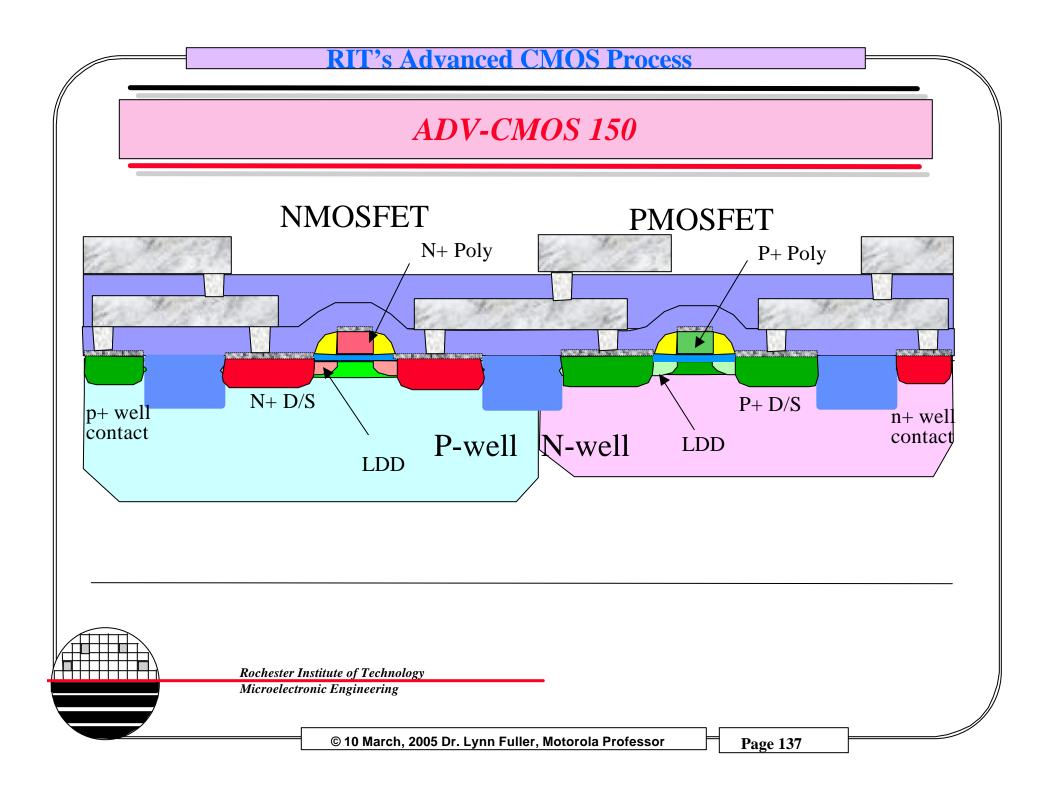

### **ADV-CMOS 150 PROCESS**

CMOS Versions 150, one level Metal

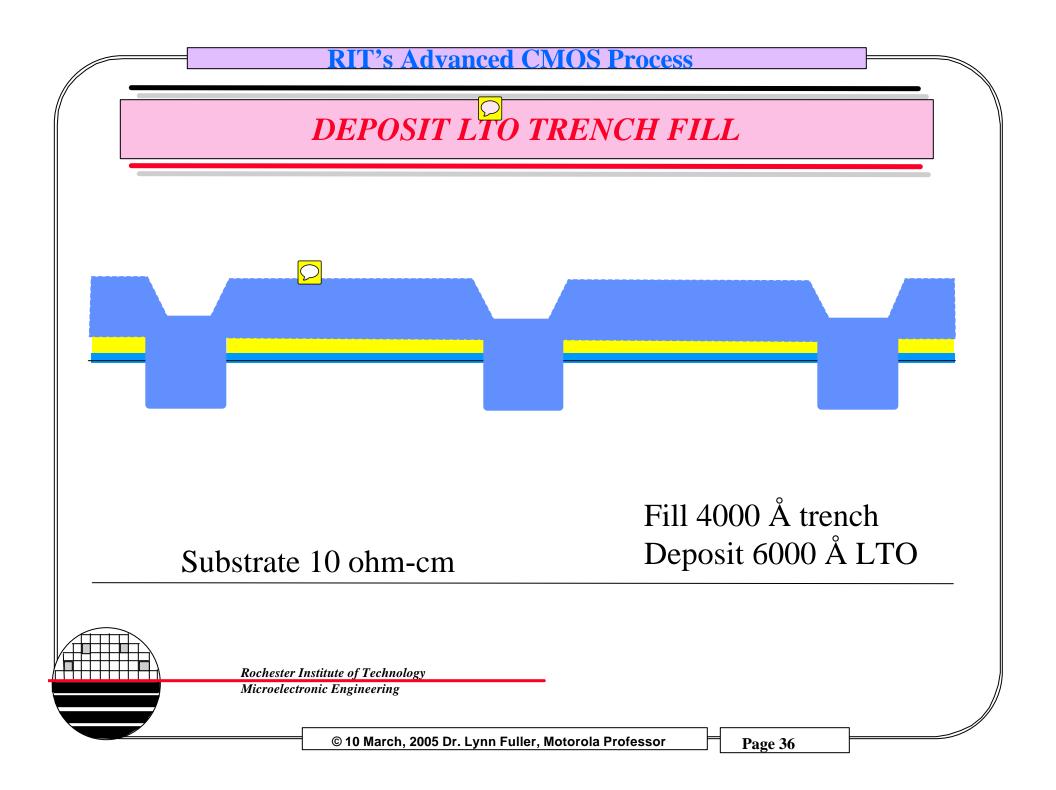

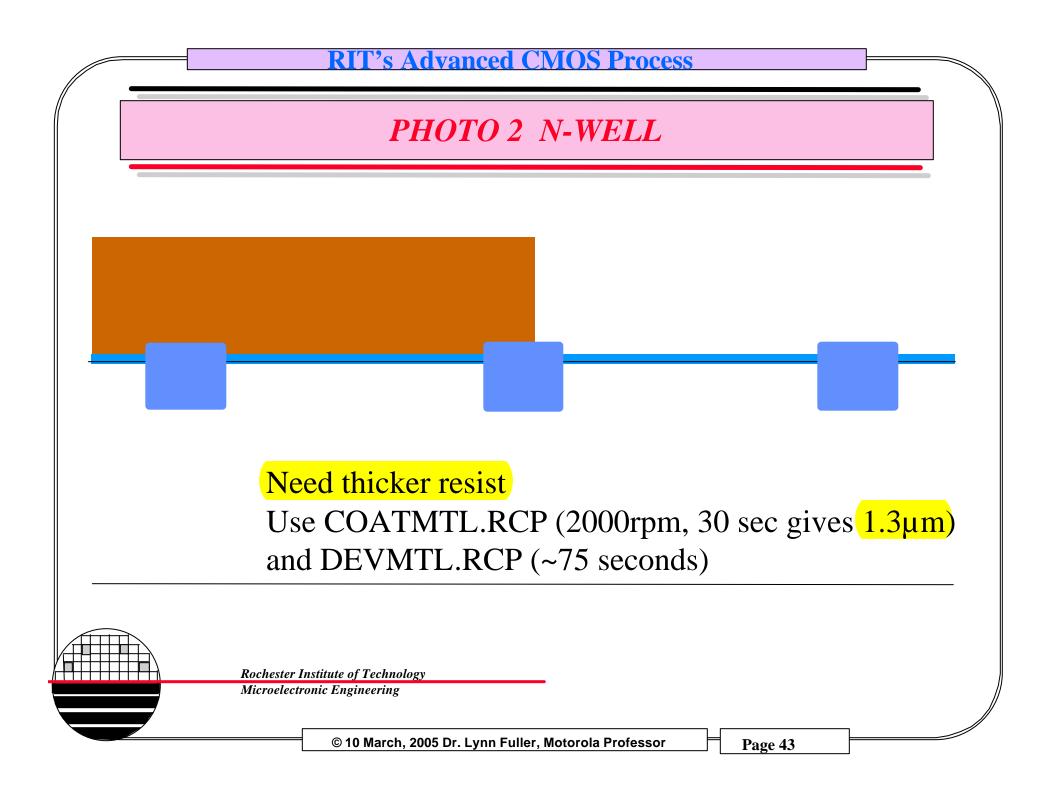

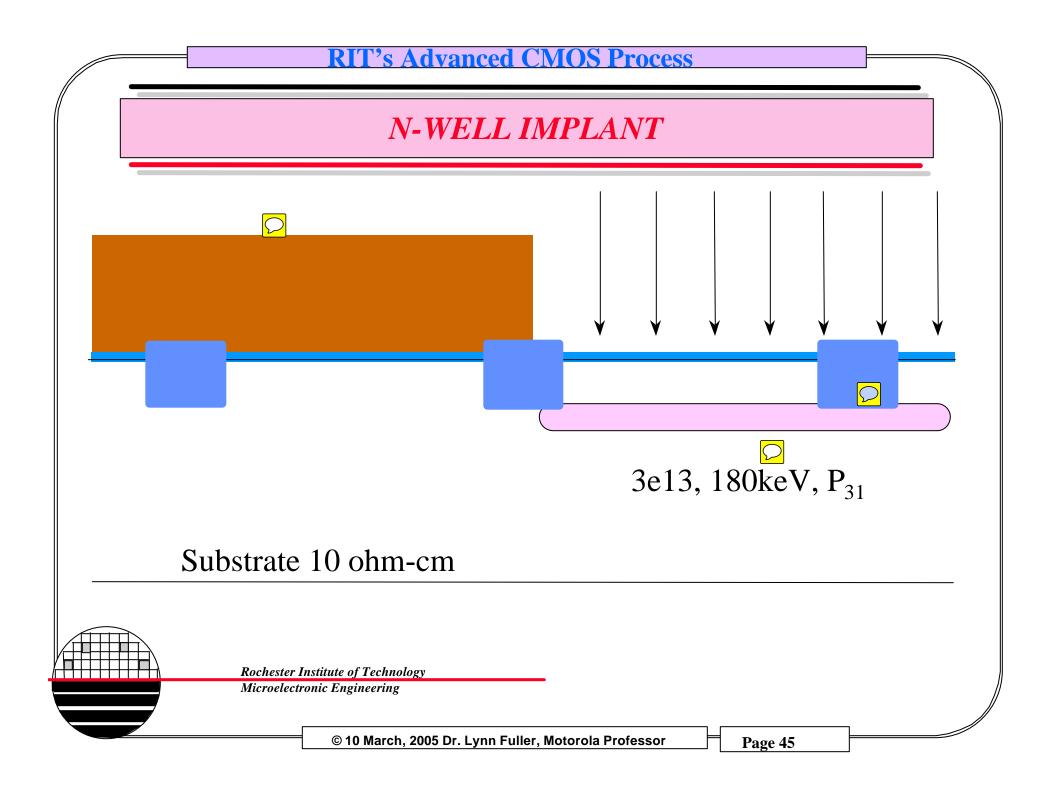

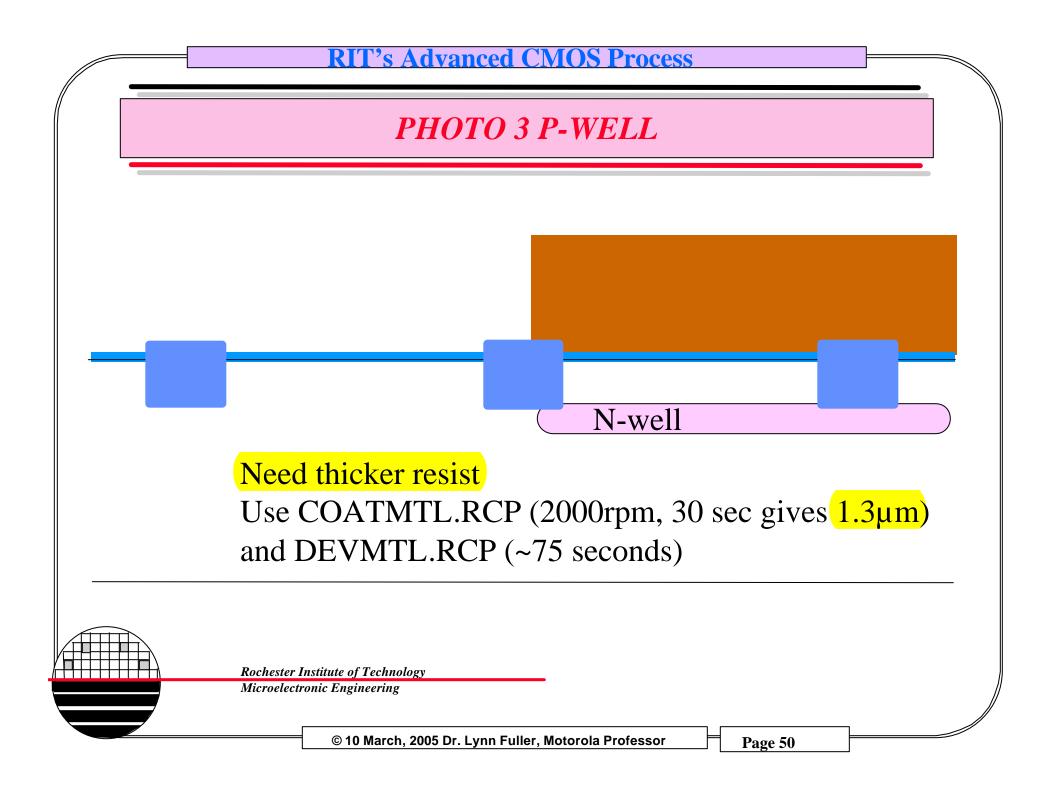

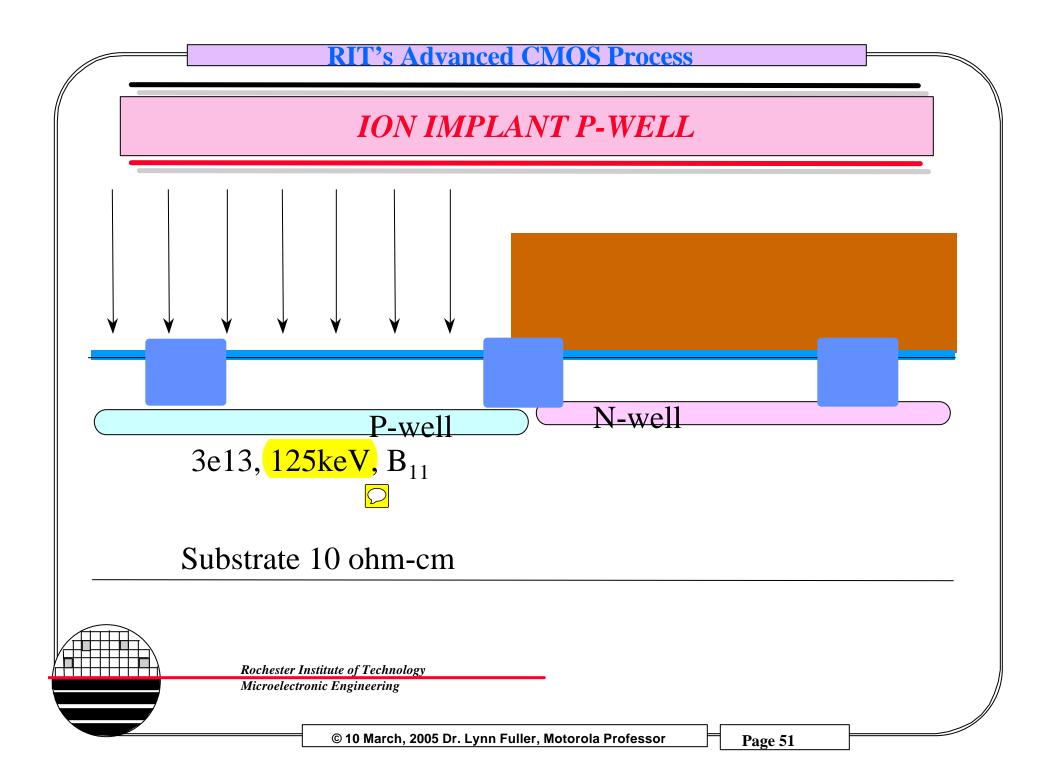

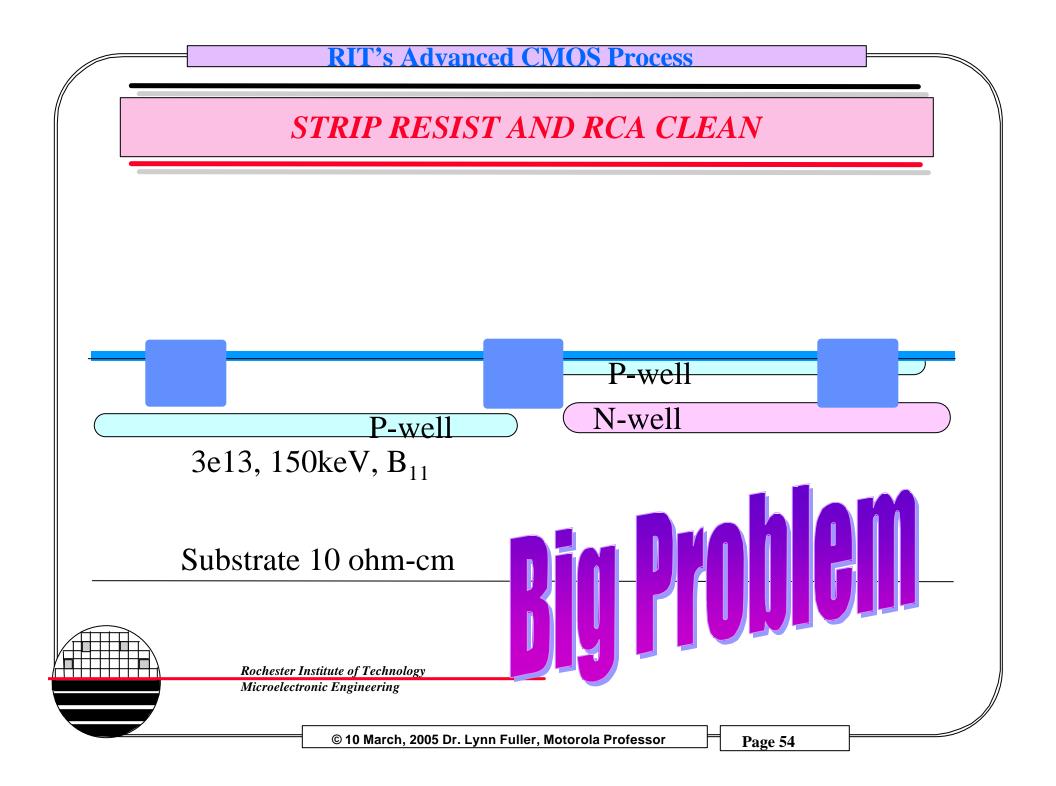

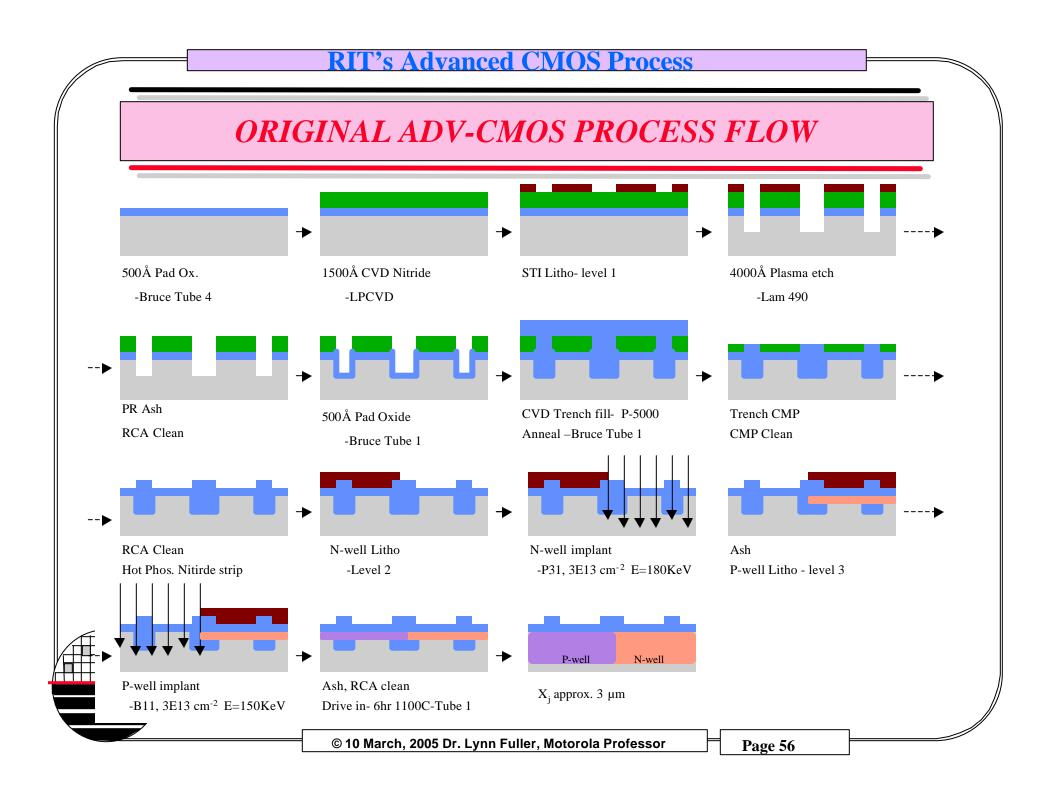

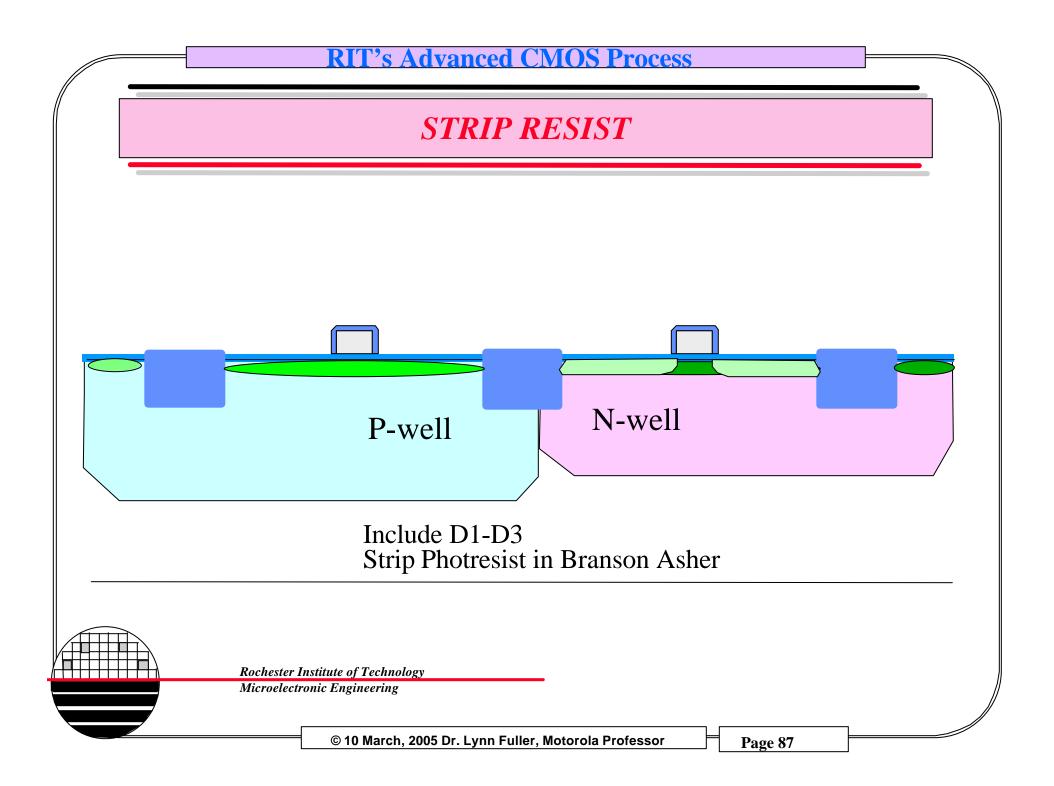

1. ID01 2. DE01 3. CL01 4. OX05--- pad oxide 500 A 5. CV02- 1500 Å 6. PH03 –1- STI 7. ET29 etch shallow trench, 4000A 8. ET07-ash 9. CL01 10. OX05 - pad oxide, 500 A 11. CV03 – CVD oxide trench fill 11.1 OX07 - Anneal 12. CM01 – Trench CMP 13. CL02 - CMP Clean 14. CL01-rca clean 15. ET19 hot phos 16. PH03-2-n-well 17. IM01 3E13, P31, 180 KeV 18. ET07-ash 19. PH03 – 3 – p-well 20. IM01 – 3E13, B11, 150KeV 21. ET07 -ash

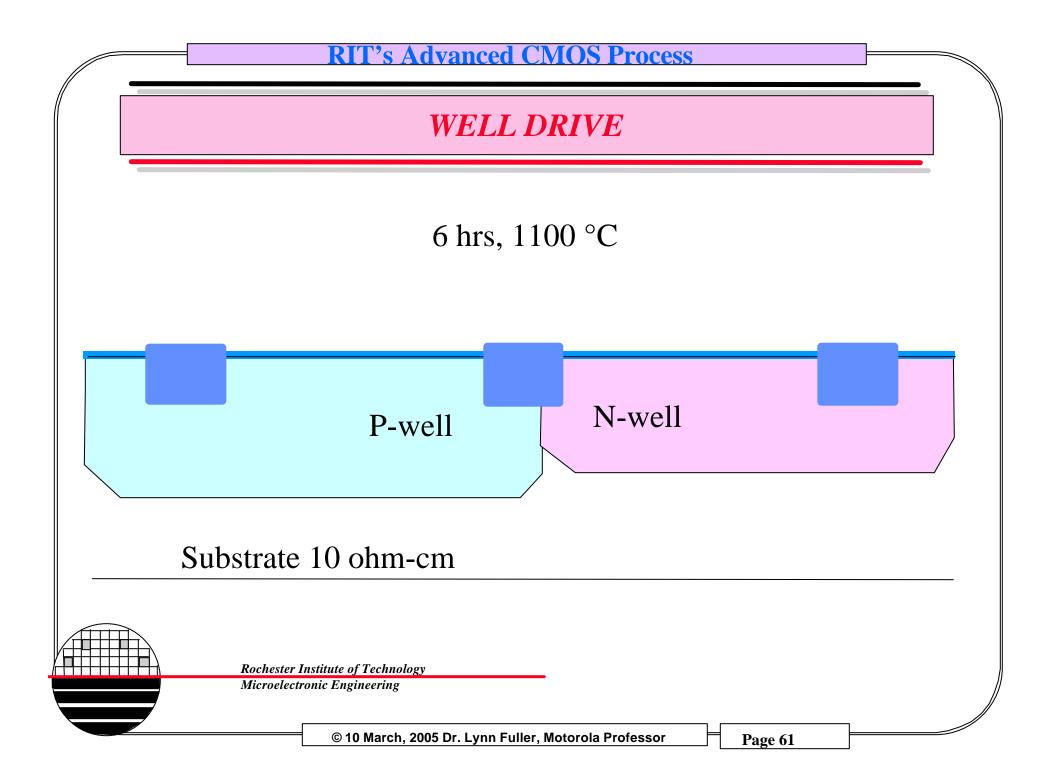

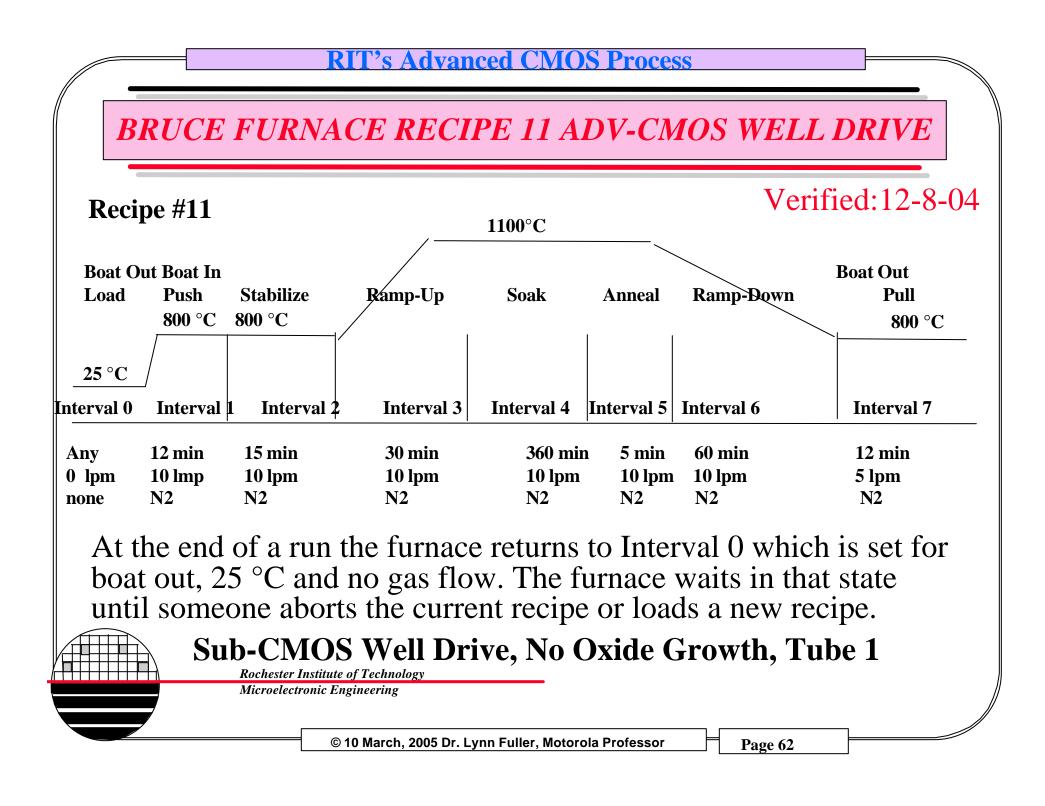

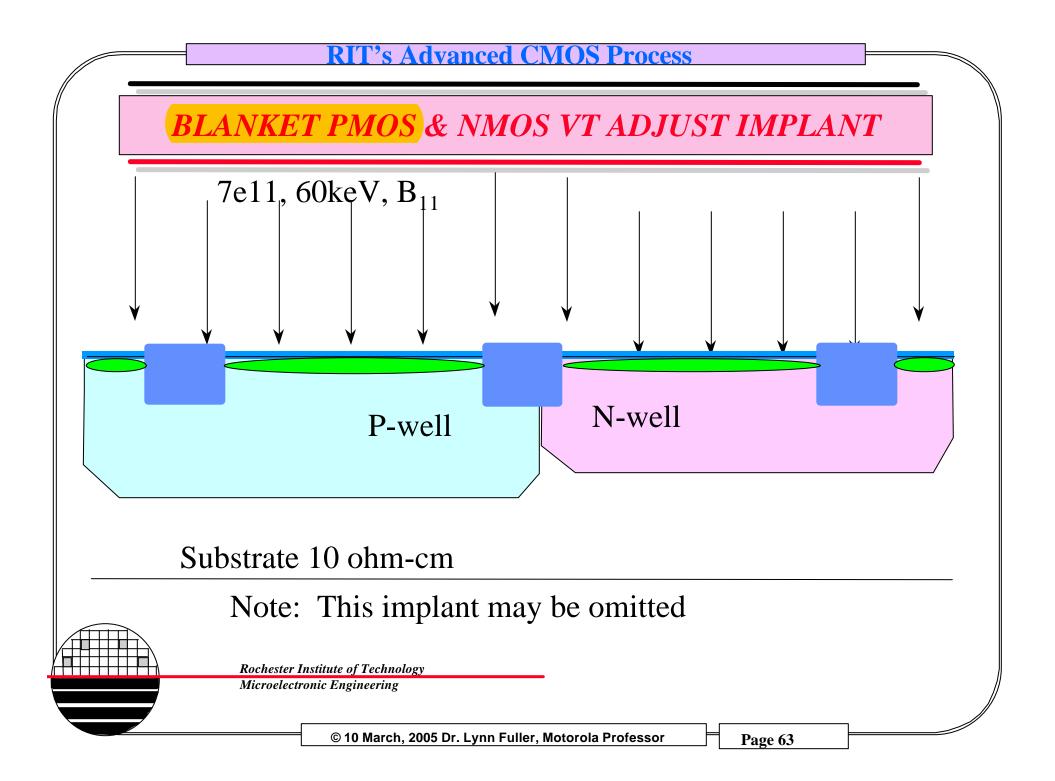

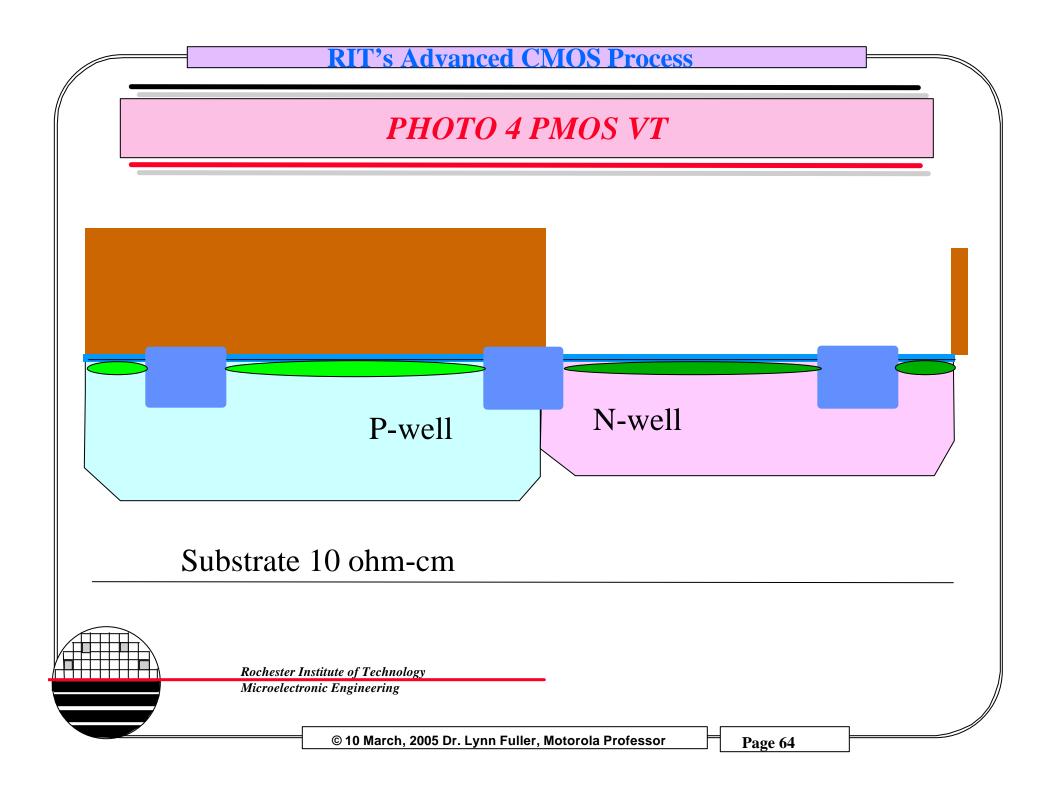

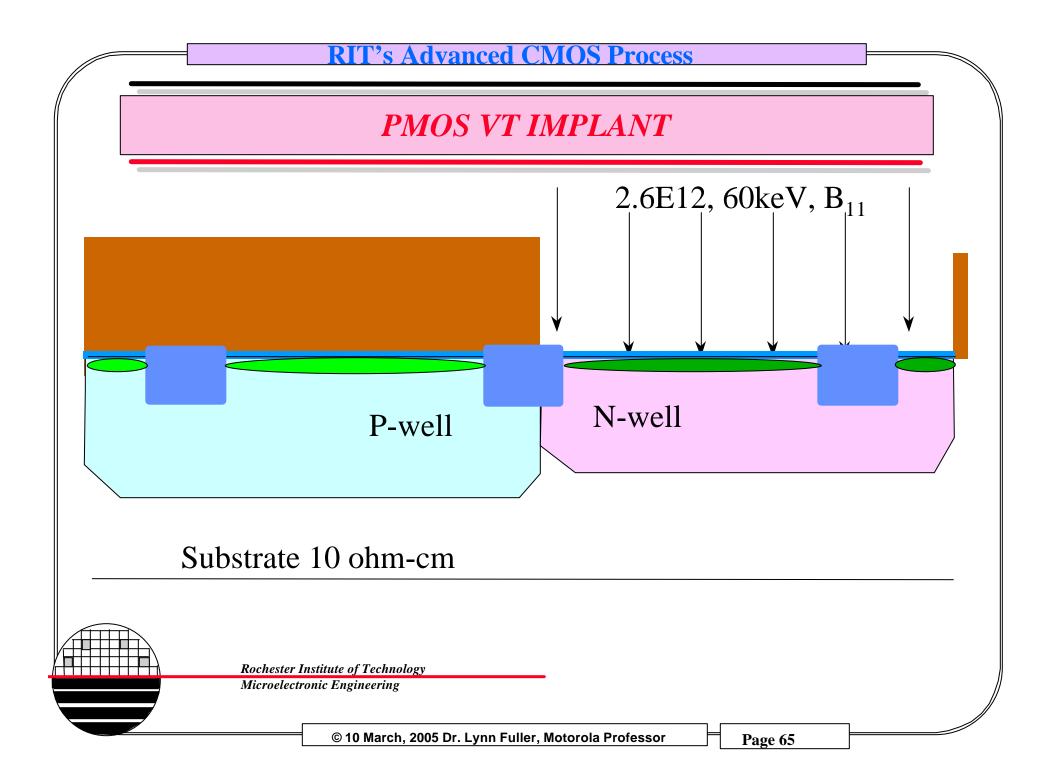

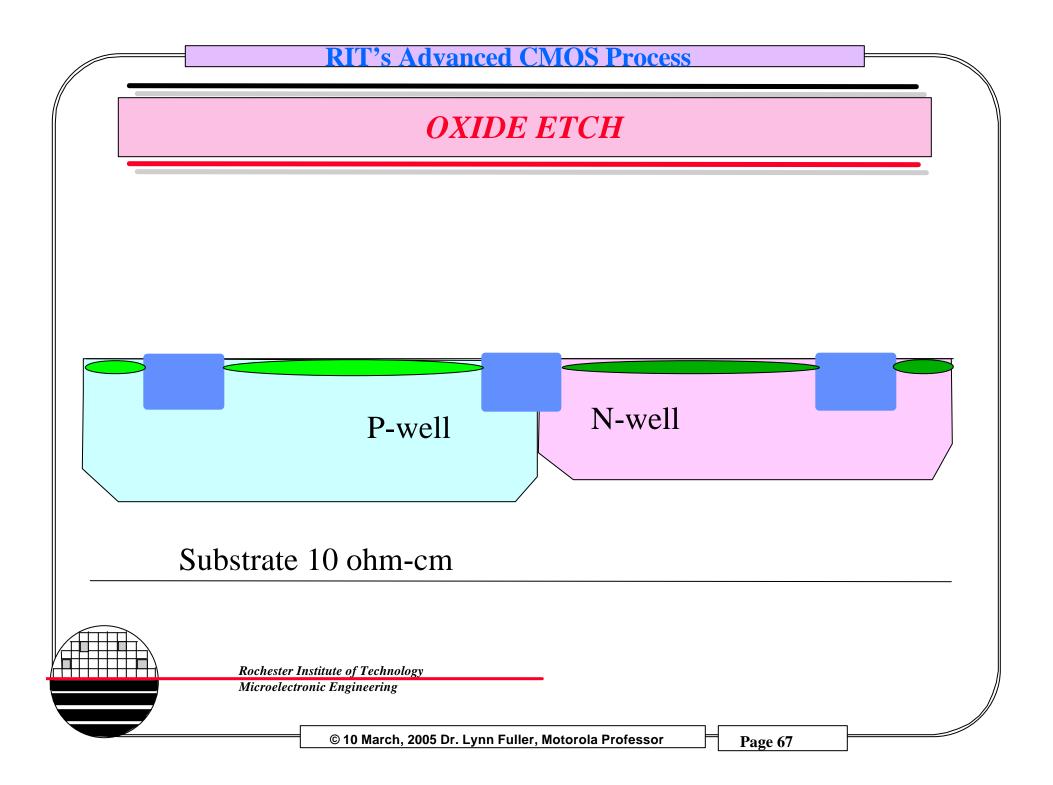

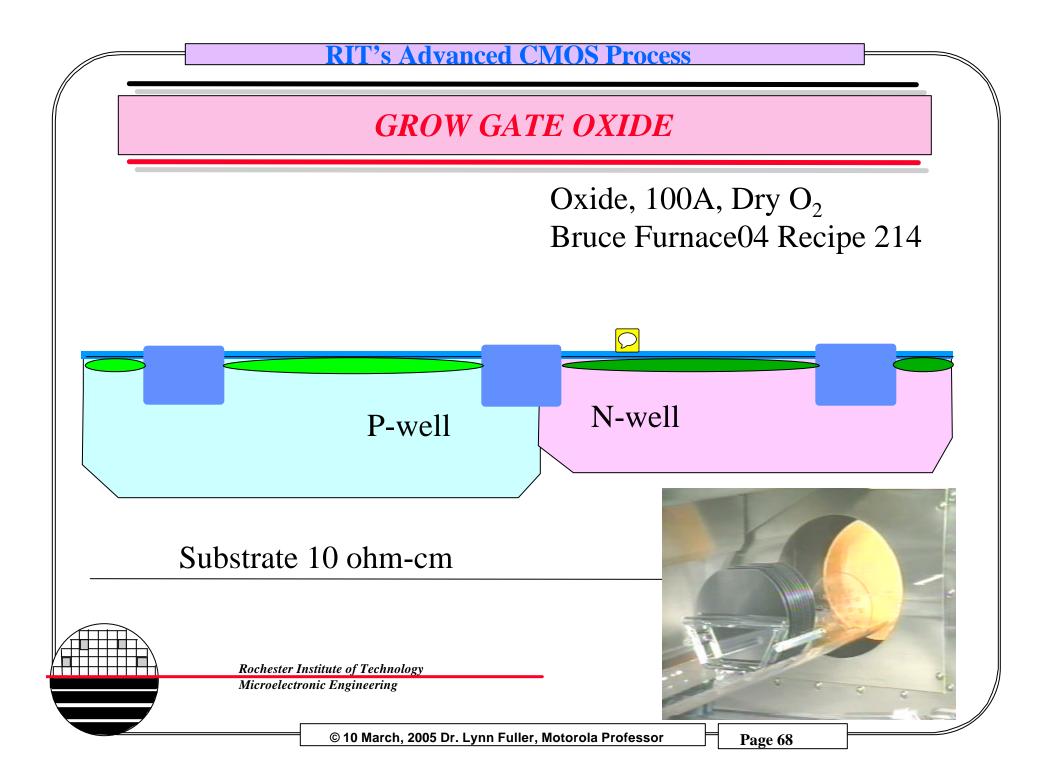

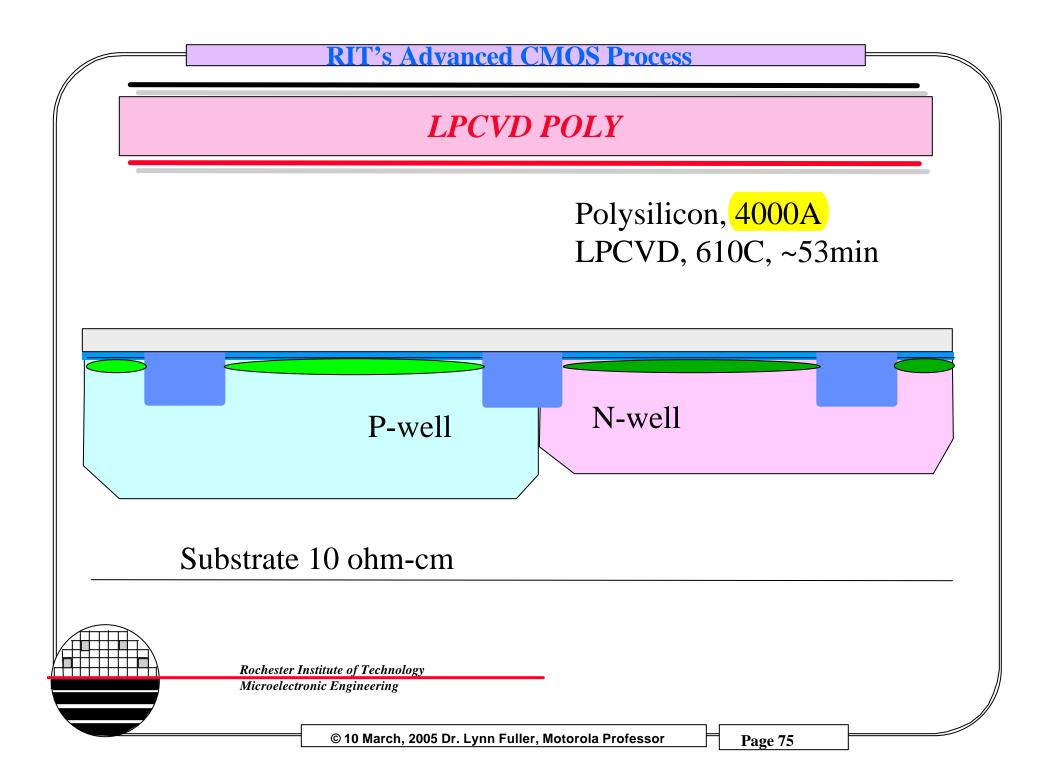

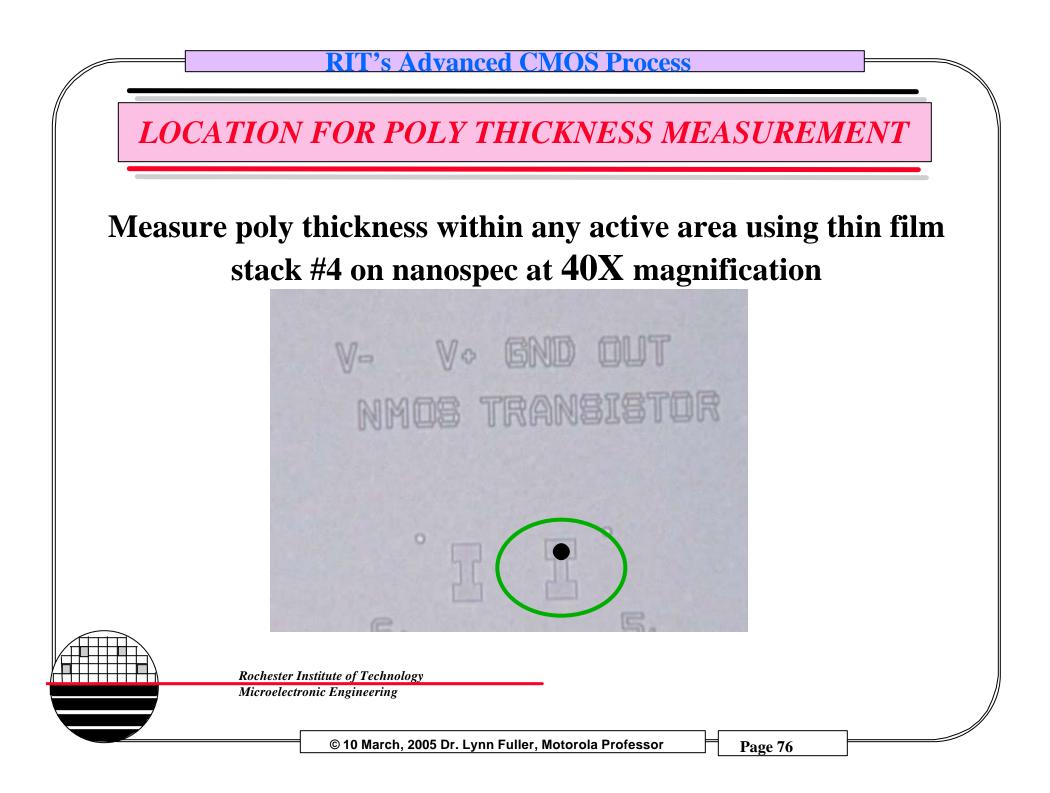

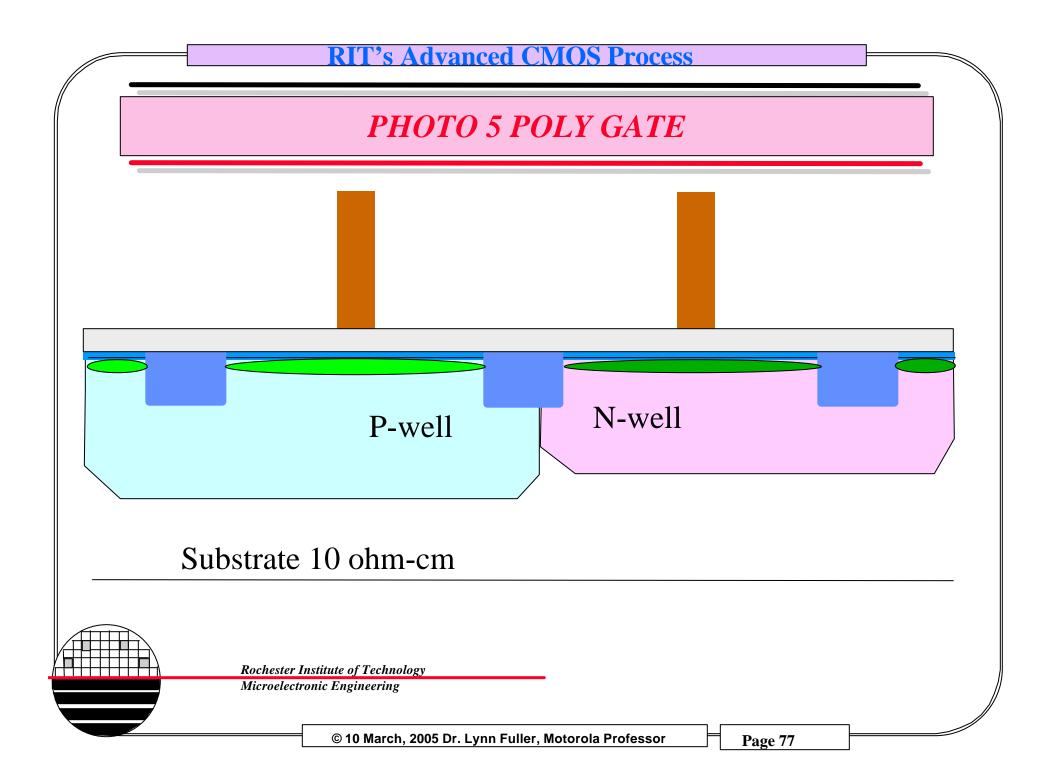

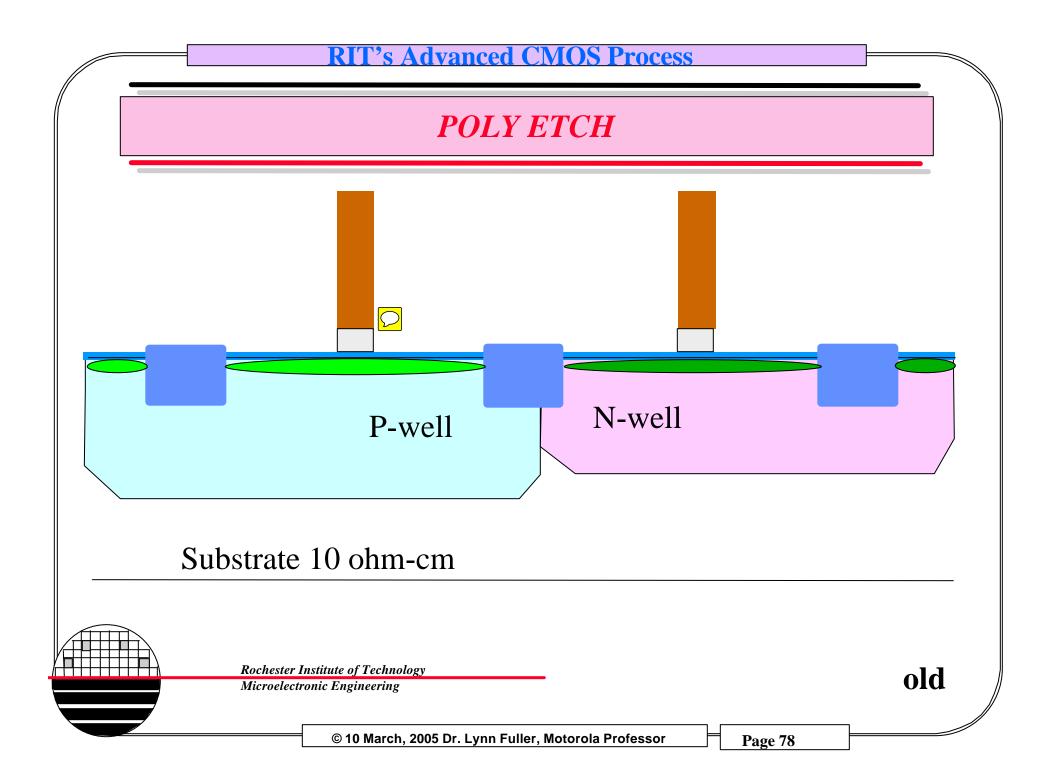

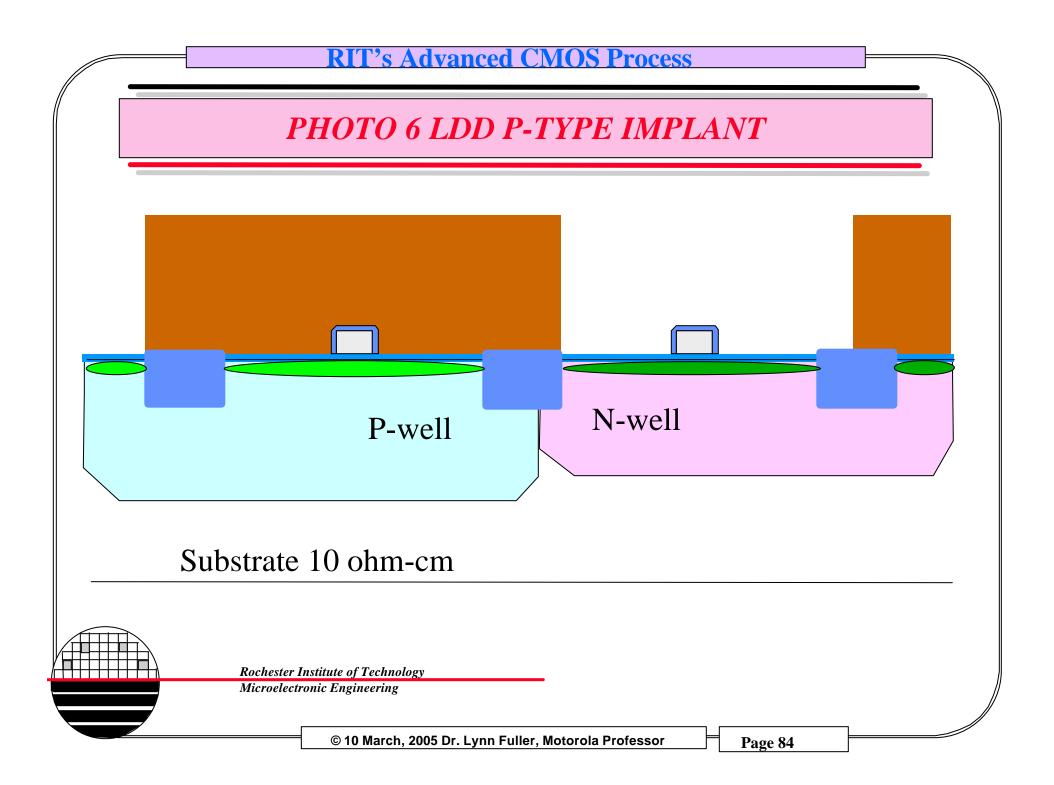

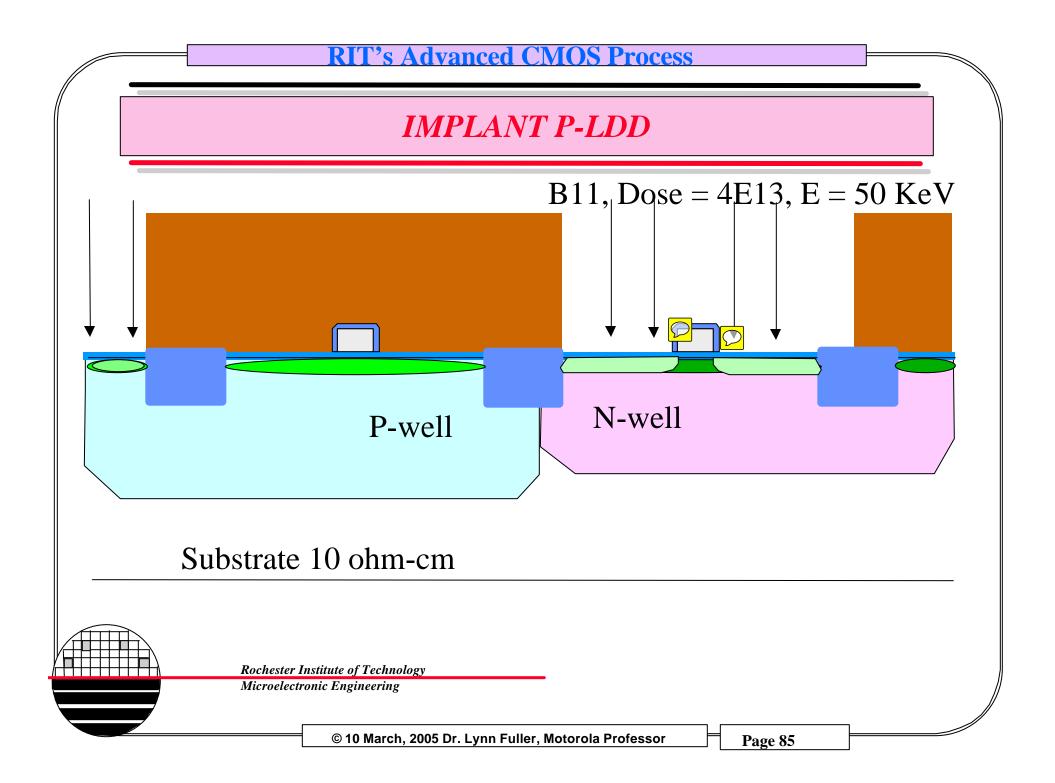

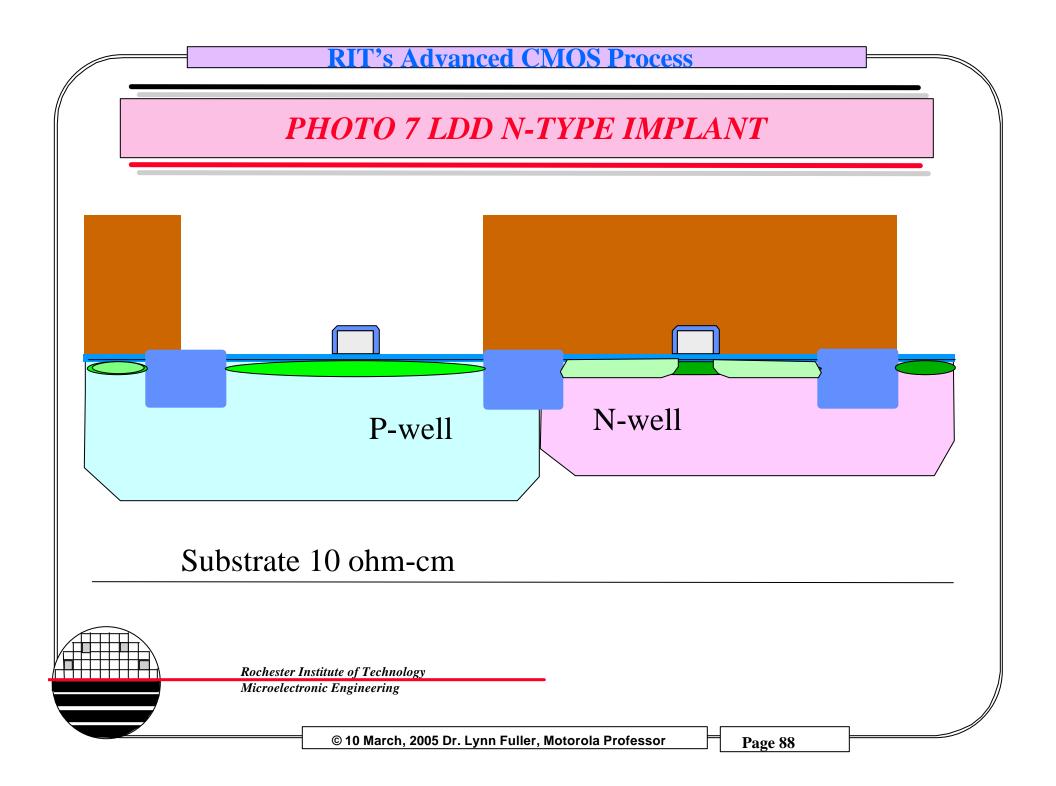

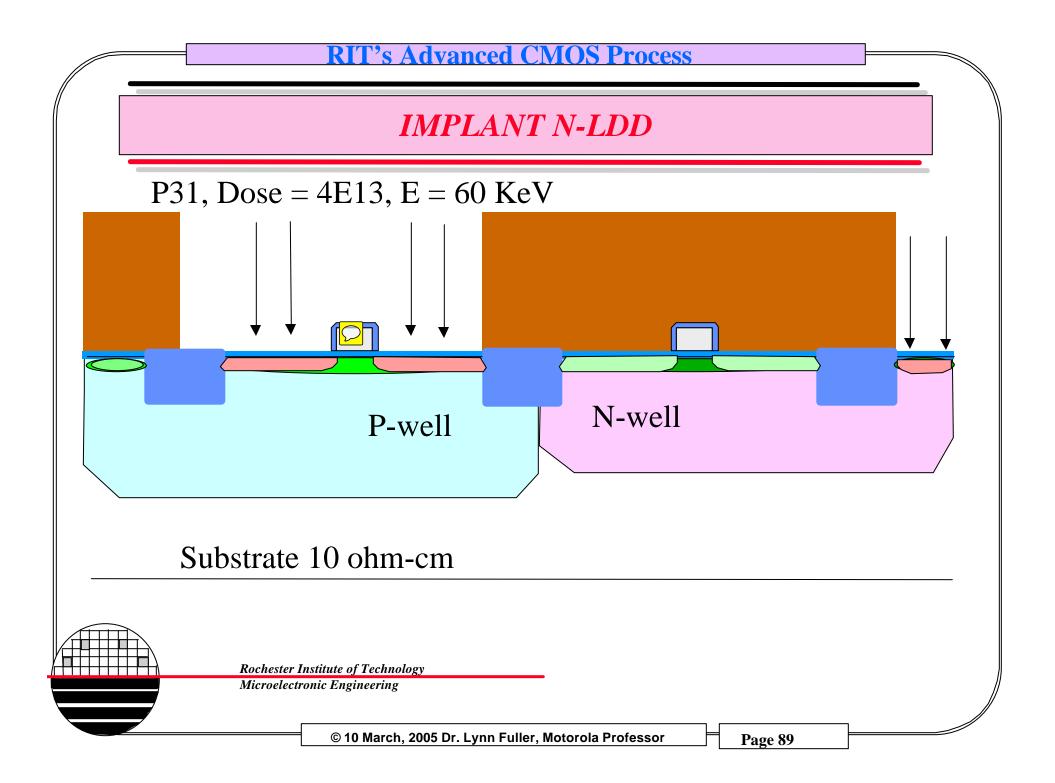

22. CL01 23. OX06 well drive. 6hr 1100C 24. IM01 blanket implant 25. PH03 – 4 - VT adjust 26. IM01 adjust 27. ET07 28. CL01 29. ET06 oxide etch 30. OX06 gate oxide 31. CV01 poly dep 32. PH03 - 5 - poly 33. ET08 poly etch 34. ET07 35 CL01 36 OX05 pad oxide 37. PH03 -6- p LDD 38. IM01 p LDD 39. ET07 40. PH03 –7- n LDD 41. IM01 n LDD 42. ET07

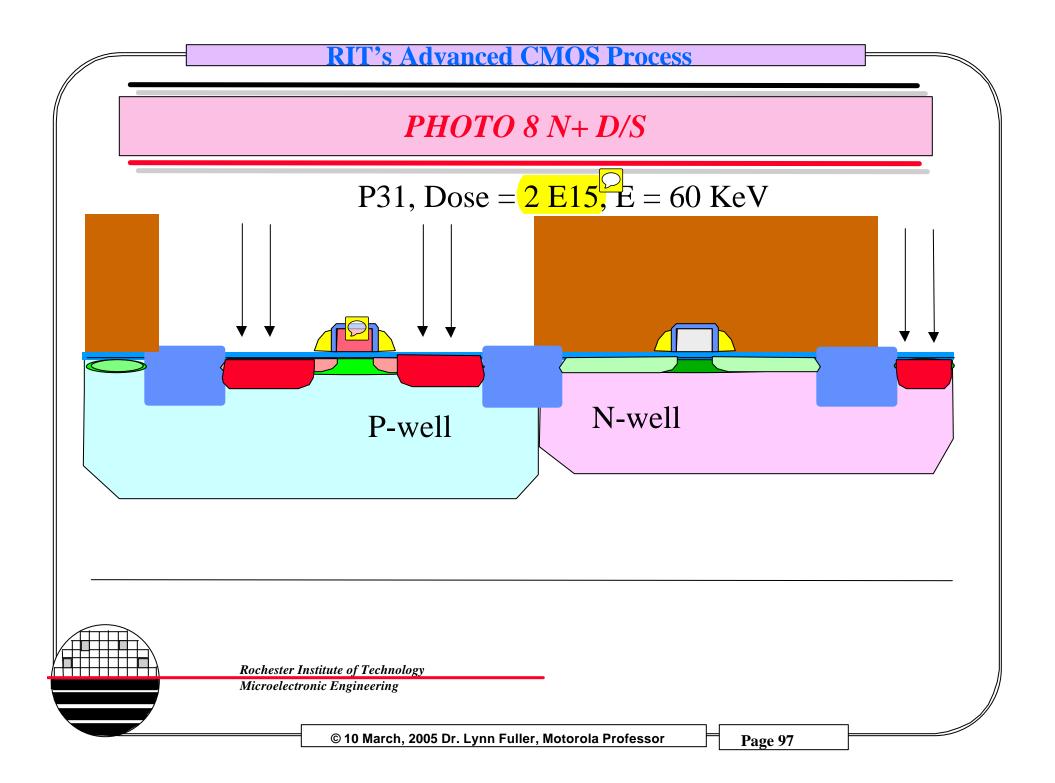

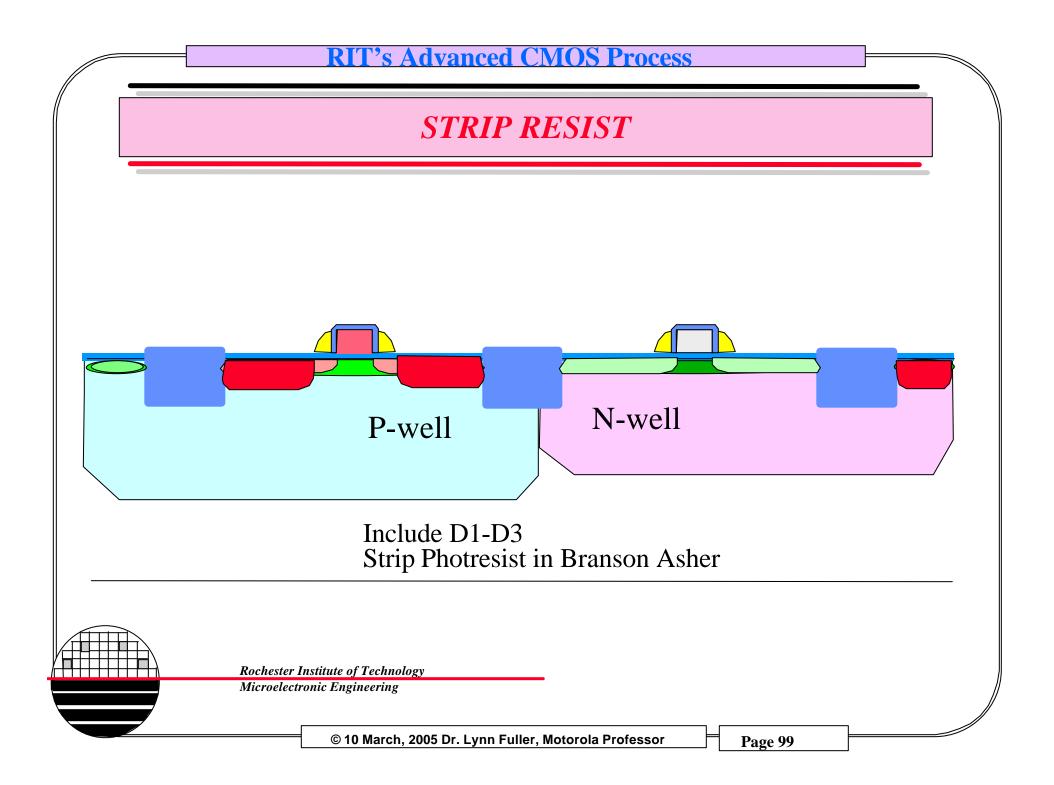

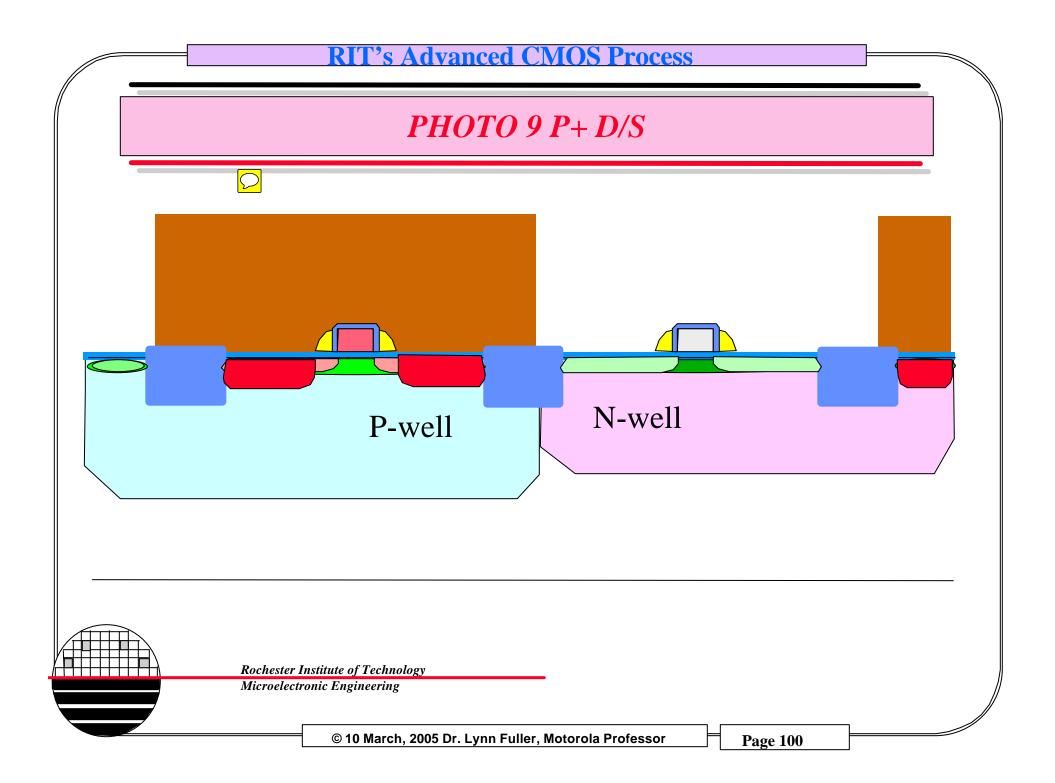

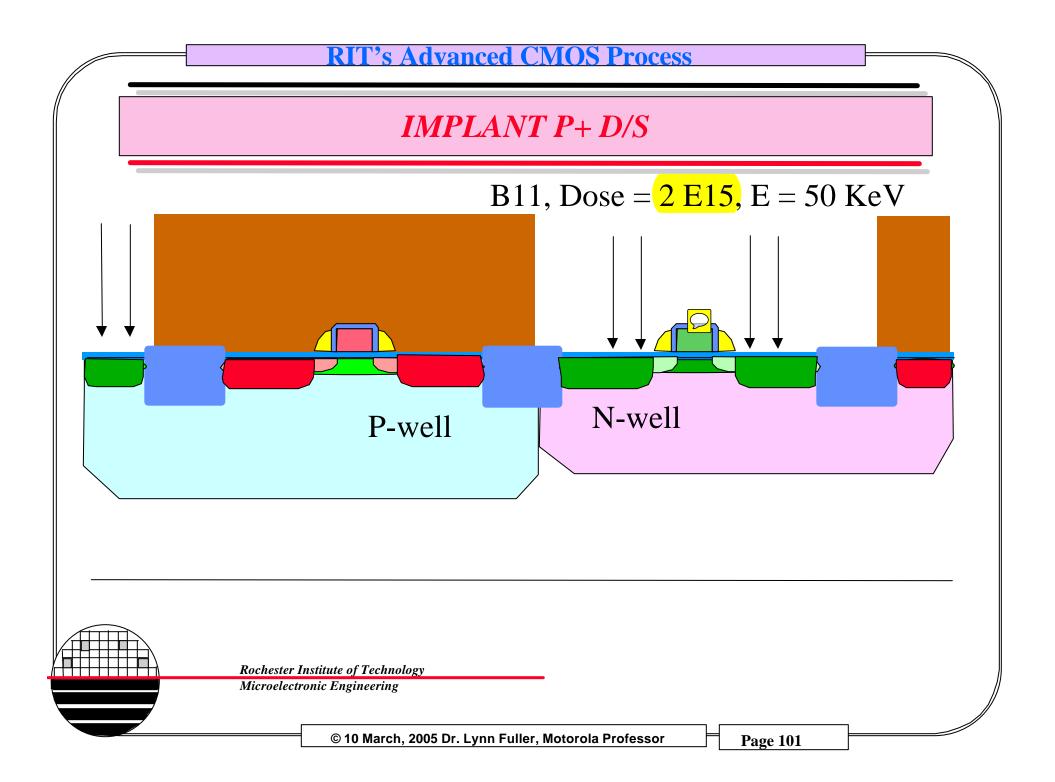

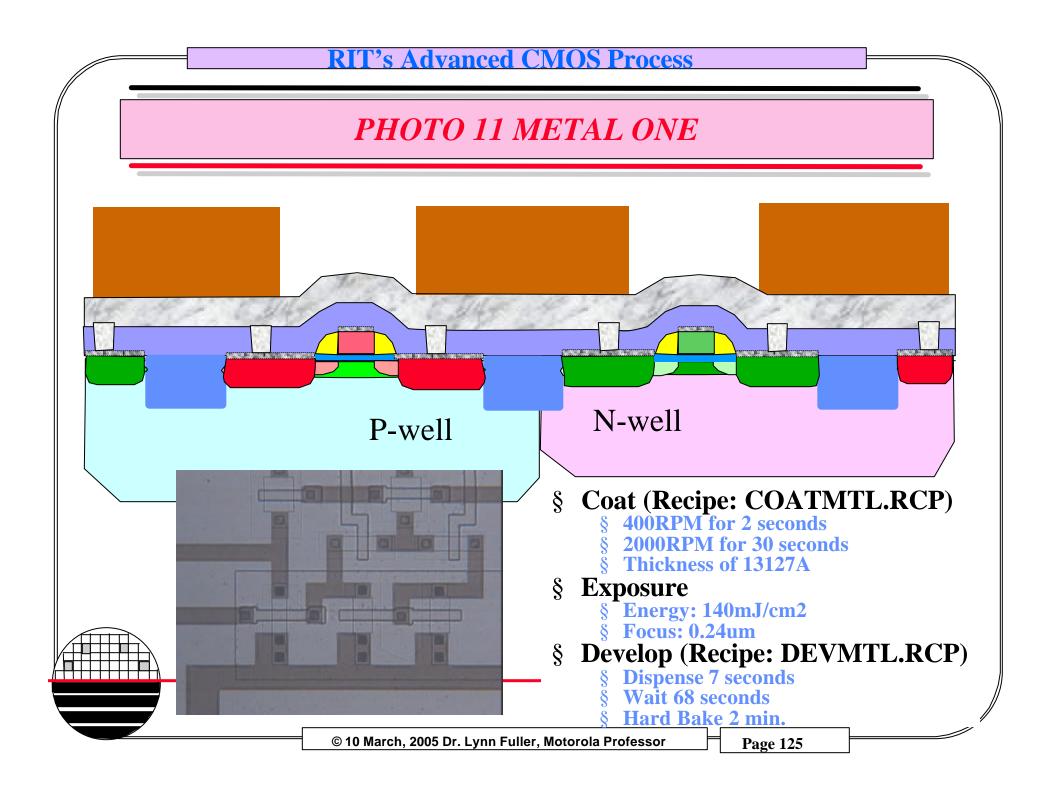

44. CV02 nitride spacer dep 45. ET39 spacer etch 46. PH03 – 8 - N+D/S 47. IM01 - N + D/S48. ET07 49. PH03 – 9- P+ D/S 50. IM01 - P + D/S51. ET07 52. CL01 53. OX08 – DS Anneal 54. ME03 HF dip & Co/Ti 55. RT01 56. ET11 Ti Etch 57. RT02 58. CV03 – LTO 59. PH03 – 10 CC 60. ET10 61. ET07 62. CL01 62.1 CV04 W Plugs 63 ME01 Aluminum

64. PH03 -11- metal

65. ET15 plasma Al Etch

66. ET07

67. SI01

68. SEM1

69. TE01

70. TE02

71. TE03

72. TE04

(Revision 9-20-04)

Rochester Institute of Technology

Microelectronic Engineering

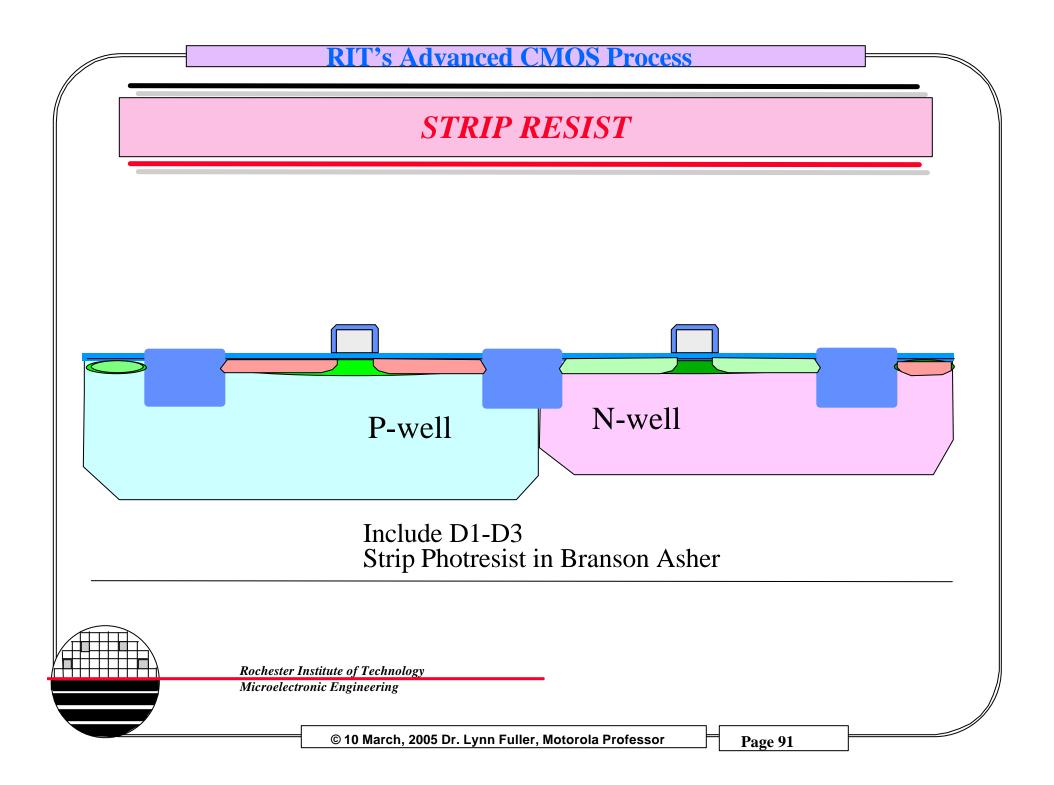

43. CL01

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

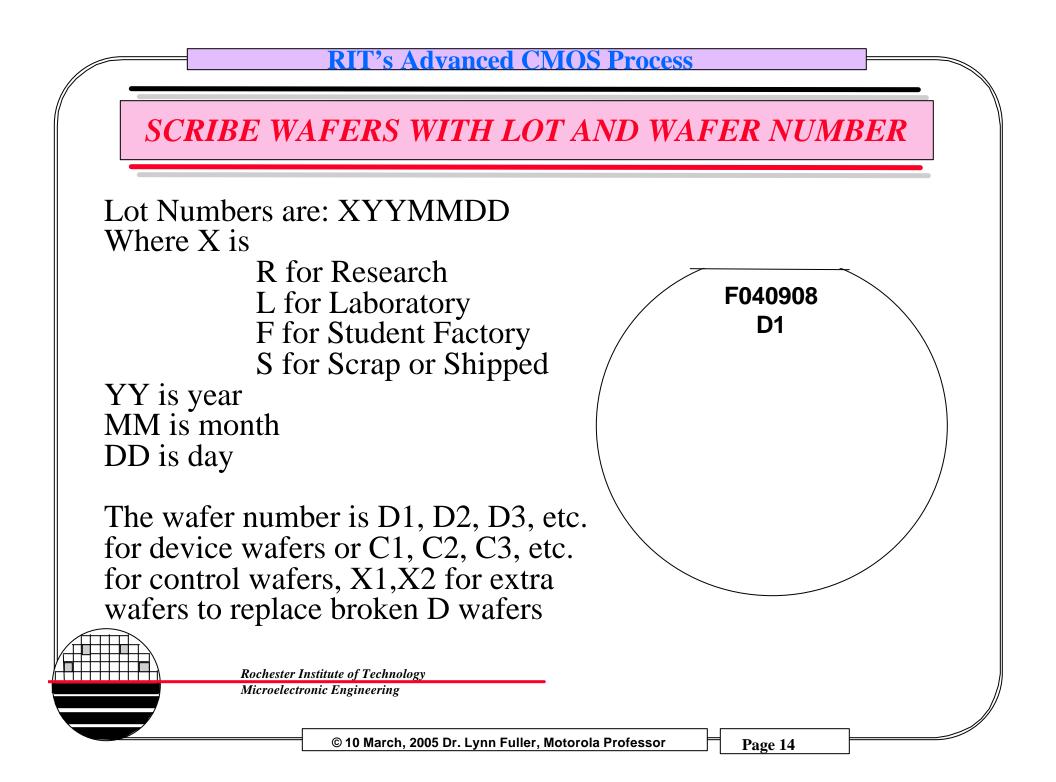

## **MEASURE WAFER SHEET RESISTANCE**

LotID, WaferID

Oper | Rogr [ Squp ] :

RunDate

Racip Name

Wafer No.

RaferDia

SdgeExcluss

CDE ResMap

Rumfitle

ProbePoints: 49 #dood: 48 Rs Avg 105.301 Obms/sg

DataRejectSigna: 3.0

StdDev 10.5959 10.0634 BBgnam30.1699 bin 90.039 Max 130.19 Range 40.186 (Mx-Mm)/Occ+0n) 19.239 (-)/2Av 19.076 Lain:14.49% Imax:23.64% (-)/Av 38.139 Gradients: R/2=7.6524 (-)/Av 38.139 Marit: 61.6 218 42.6 89.6 Bane 10.05 Idv/Ms 0.74m Vanadz 14.3m

Adatu-49 Ba Spaning = 1/3 Sigma

126.493

122.961

119.429 115.897 112.365 108.833 105.301 FileHame: C:\4F\CDE\_Demo.prj\6in49pt.rep\3220R081.Rest

COM Reshap Demo Recipes

PO21111D1 MyWafer

CDB | Customer [Realisp]

Flat

DualFrbCnfg

FollowNajorFlat

101.769

58.2367

94.7049

10:05 02/20/05

100

8.0

CDM\_Demo 6in49pt

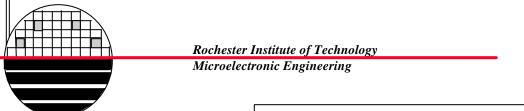

### CDE Resistivity Mapper

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

Page 15

Rho=Rhos x t

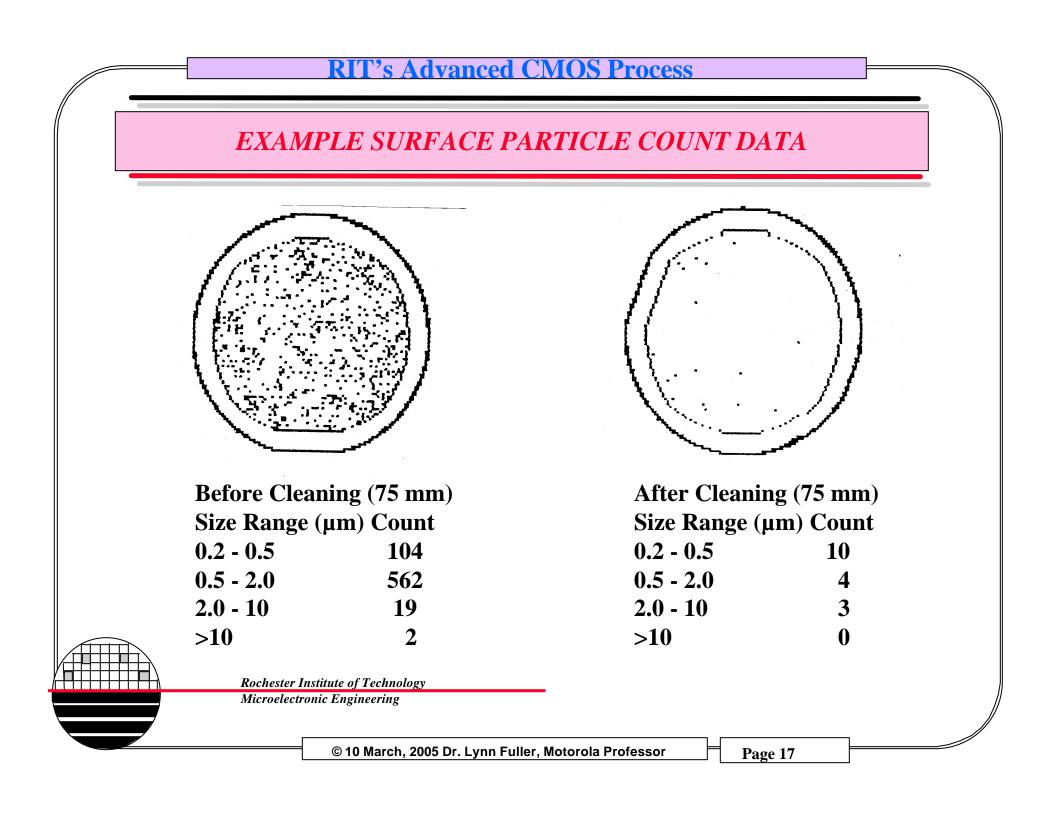

### **TENCORE SURF SCAN**

Gives total surface particle count and count in 4 bins <0.5, 0.5 to 2.0, 2.0-10, >10. Bin boundary can be selected. Edge exclusion eliminated count from near the edge of the wafer.

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

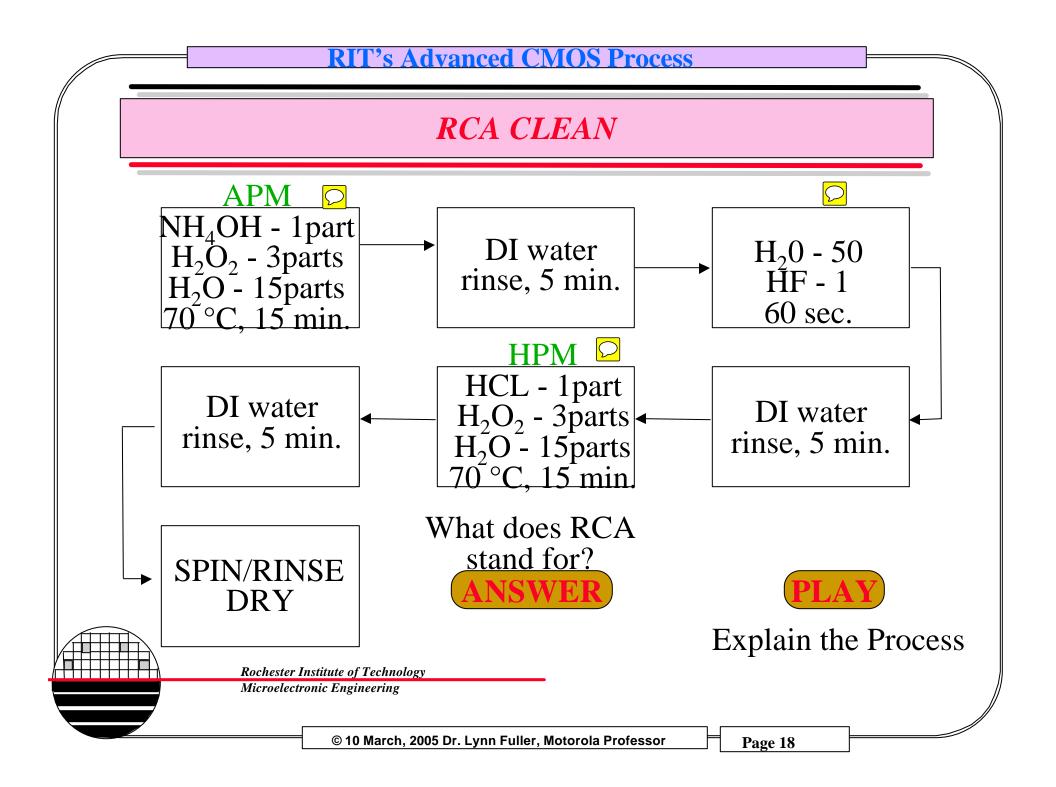

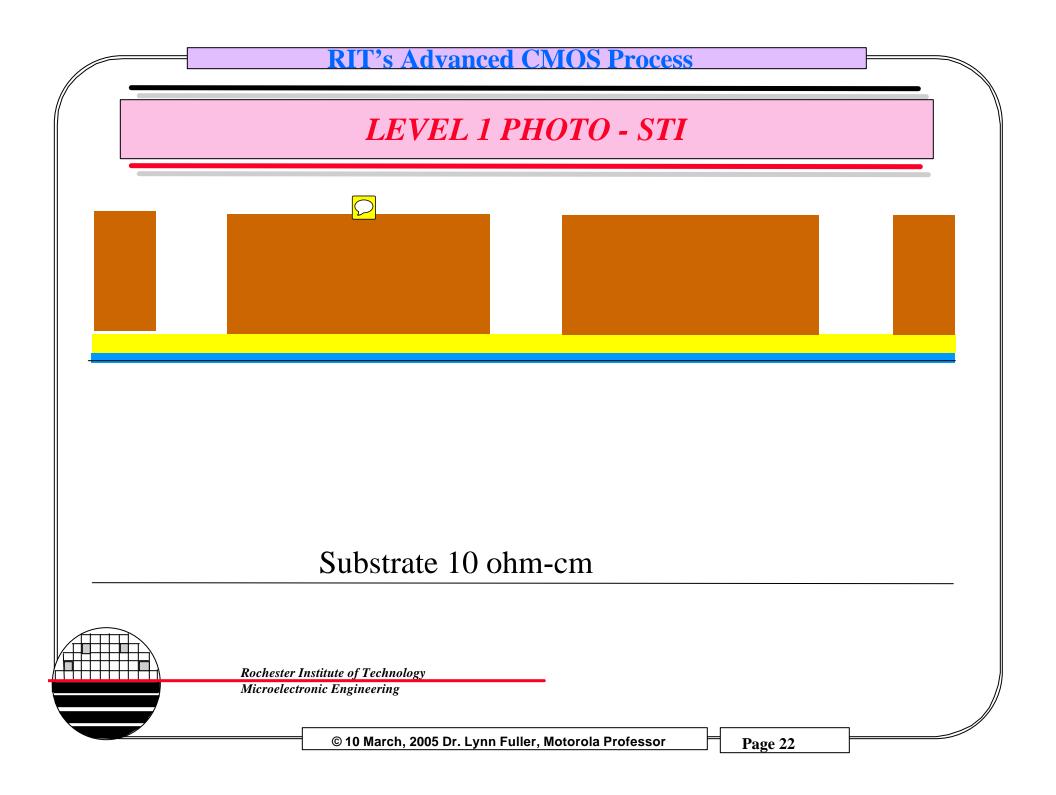

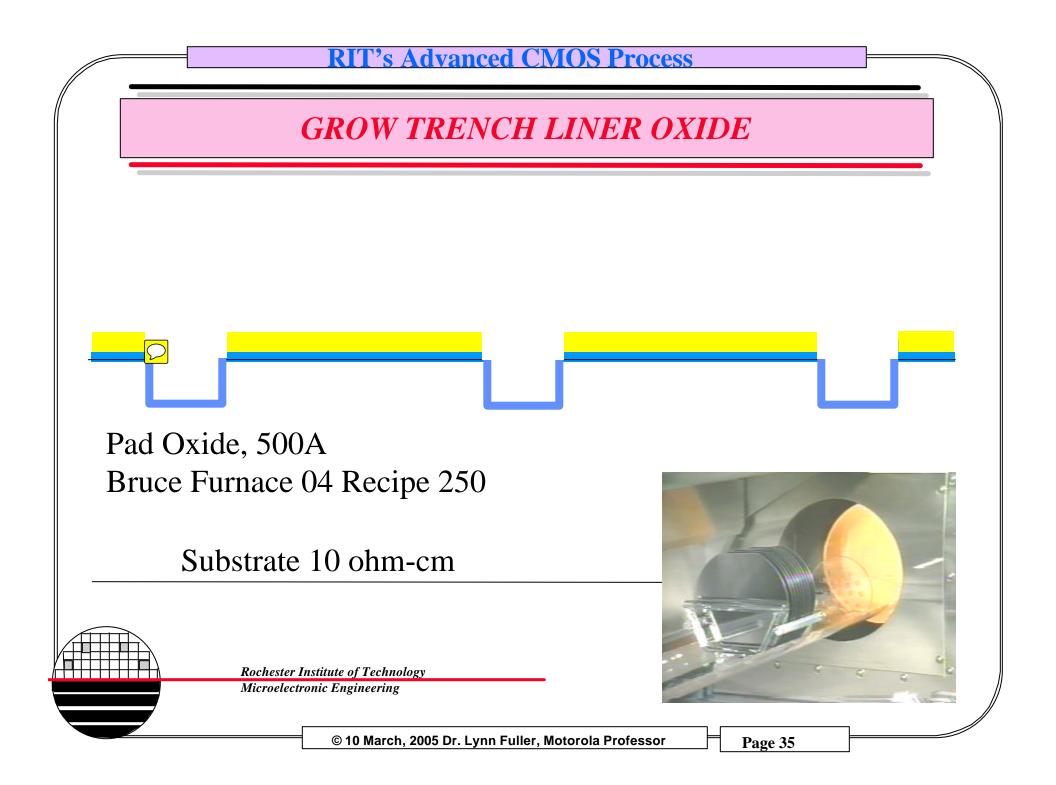

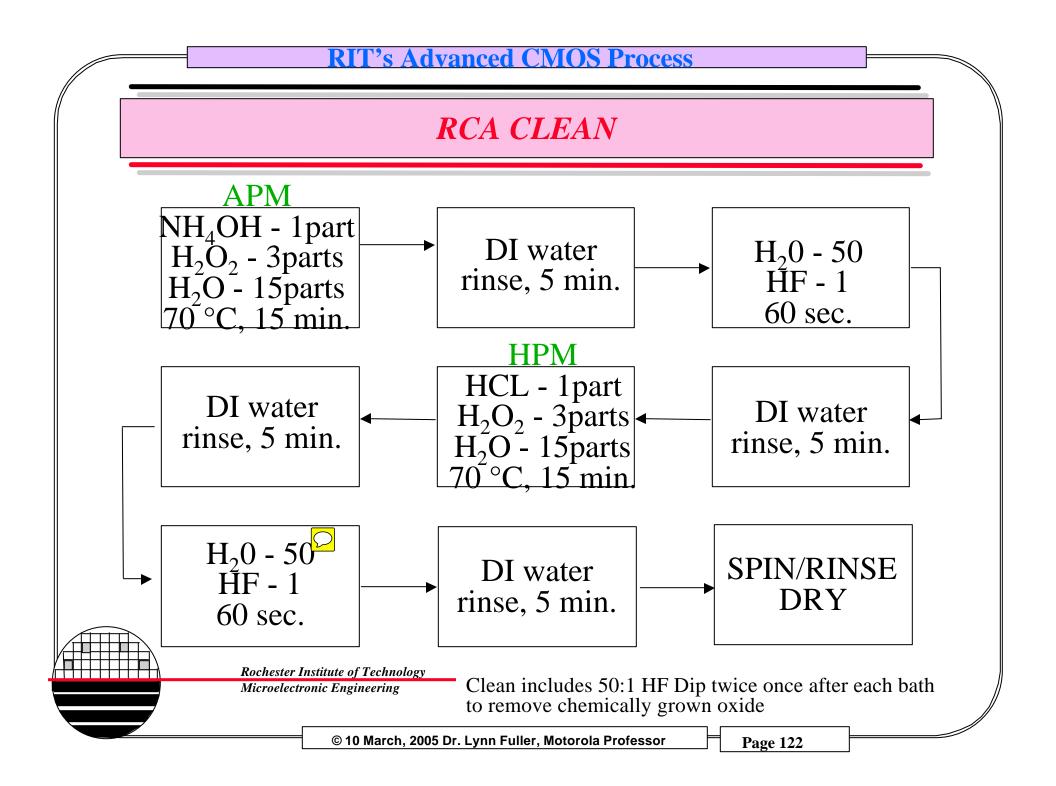

## RCA CLEAN AND PAD OXIDE GROWTH

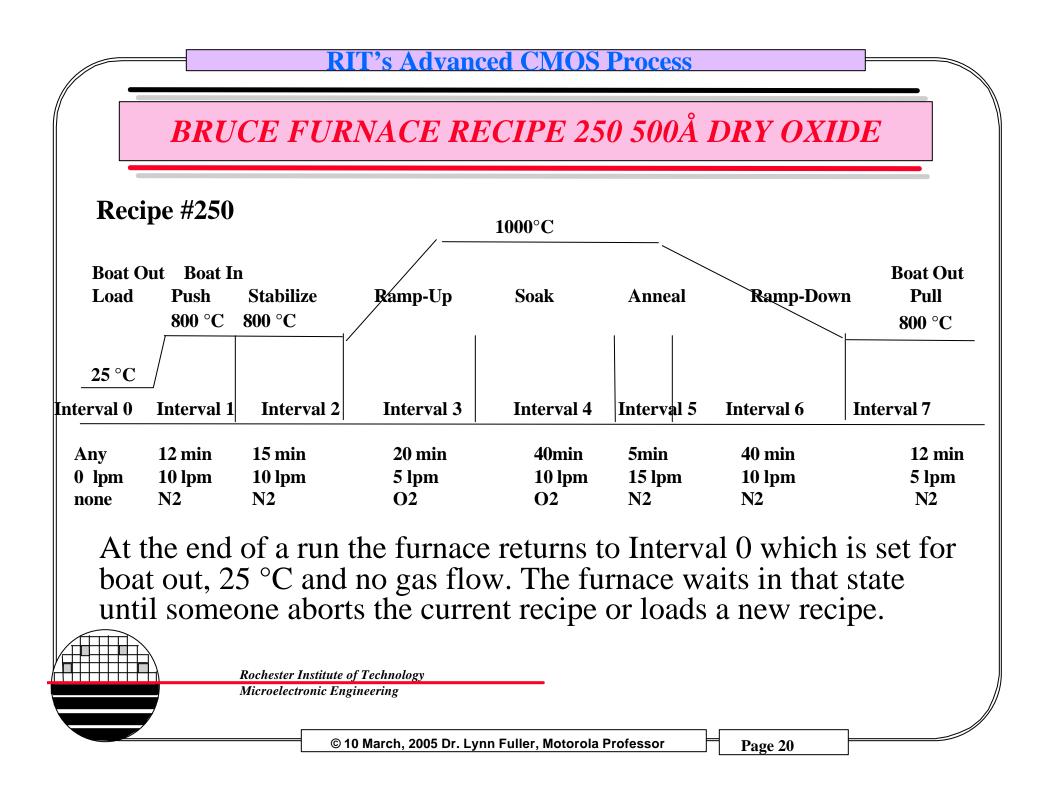

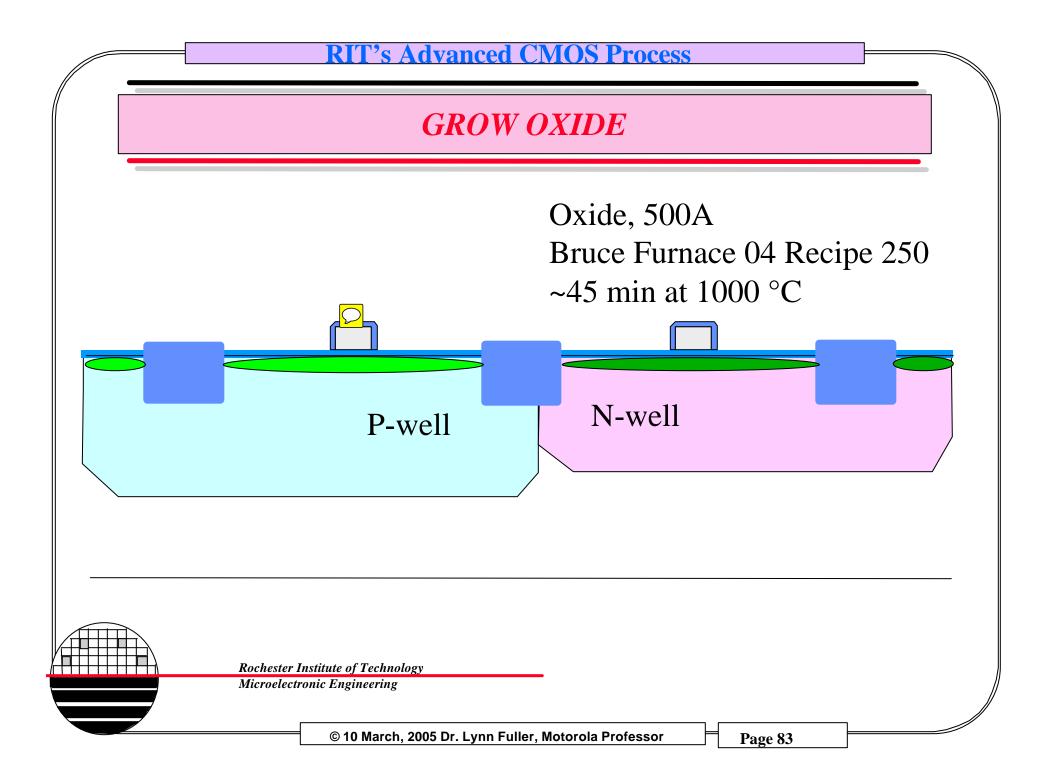

## Pad Oxide, 500A Bruce Furnace 04 Recipe 250 ~45 min at 1000 °C

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

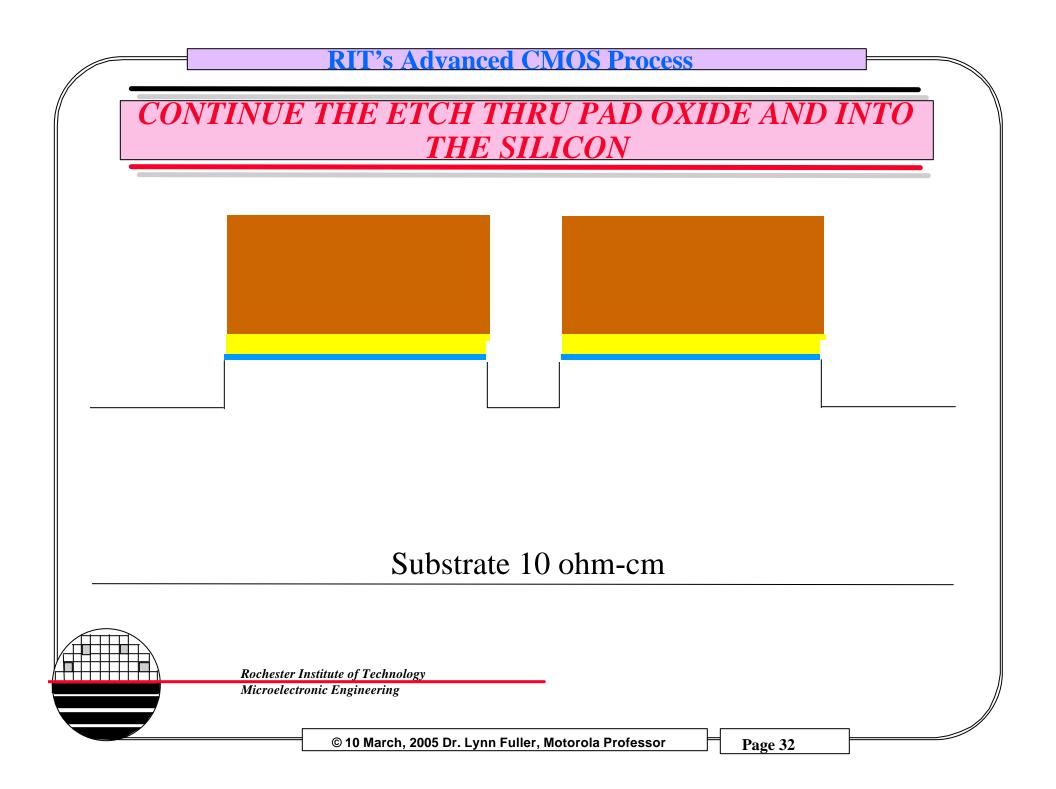

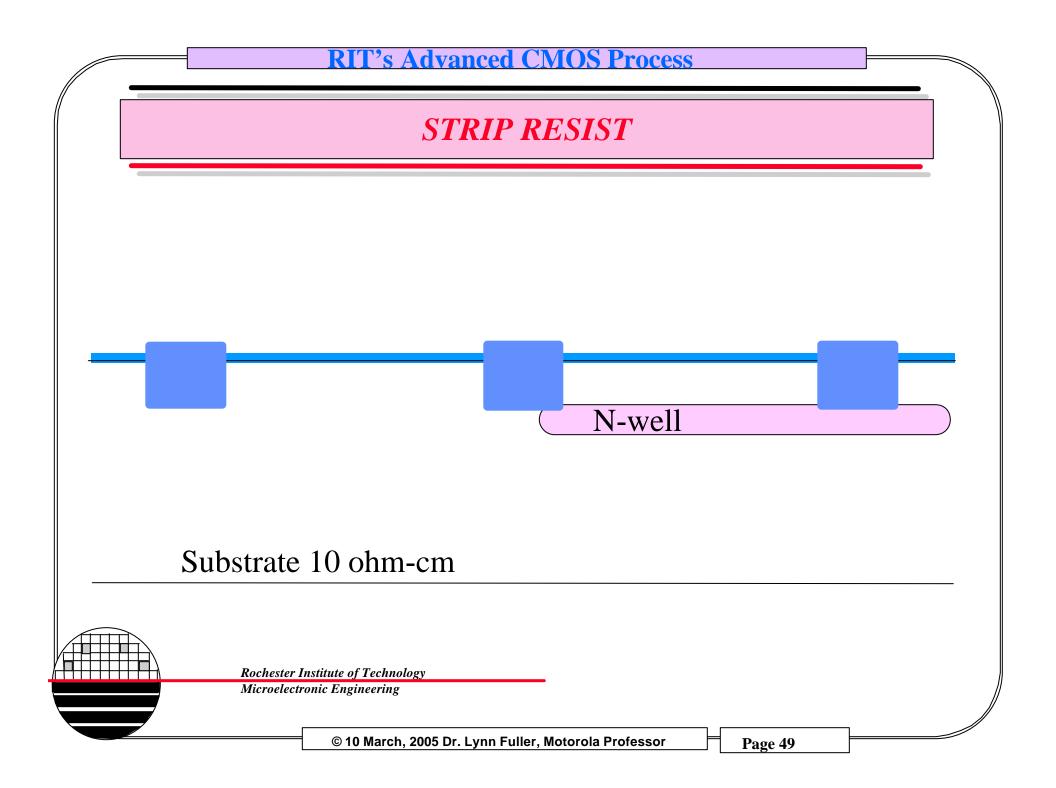

Substrate 10 ohm-cm

Rochester Institute of Technology Microelectronic Engineering

**RIT's Advanced CMOS Process DEPOSIT SILICON NITRIDE** Recipe Nitride 810 Nitride, 1500A LPCVD, 810C, ~30min Substrate 10 ohm-cm

> Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

# SSI COAT AND DEVELOP TRACK FOR 6" WAFERS

## SSI coat and develop track

Rochester Institute of Technology

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

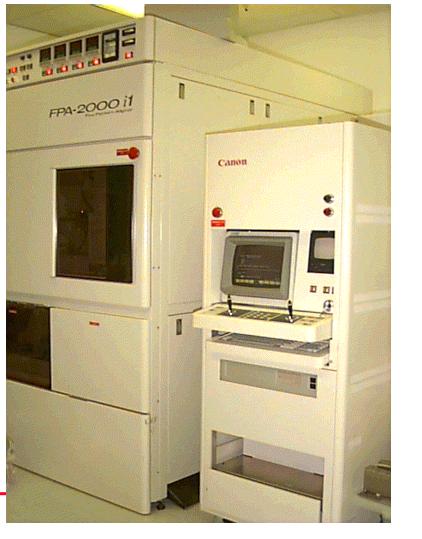

## CANON FPA-2000 i1 STEPPER

```

i-Line Stepper \lambda = 365 \text{ nm}

NA = 0.52, \sigma = 0.6

Resolution = 0.7 \lambda / NA = ~0.5 \mum

20 x 20 mm Field Size

Depth of Focus = k_2 \lambda/(NA)^2

= 0.8 \mum \square

Rochester Institute of Technology

Microelectronic Engineering

```

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

## ASML 5500/90 STEPPER

KrF Excimer Laser Stepper  $\lambda = 248 \text{ nm}$  $NA = 0.52, \sigma = 0.6$ Resolution = 0.7  $\lambda$  / NA = ~0.3  $\mu$ m 20 x 20 mm Field Size Depth of Focus =  $k_2 \lambda/(NA)^2$ ~ 0.64 µm **Rochester Institute of Technology**

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

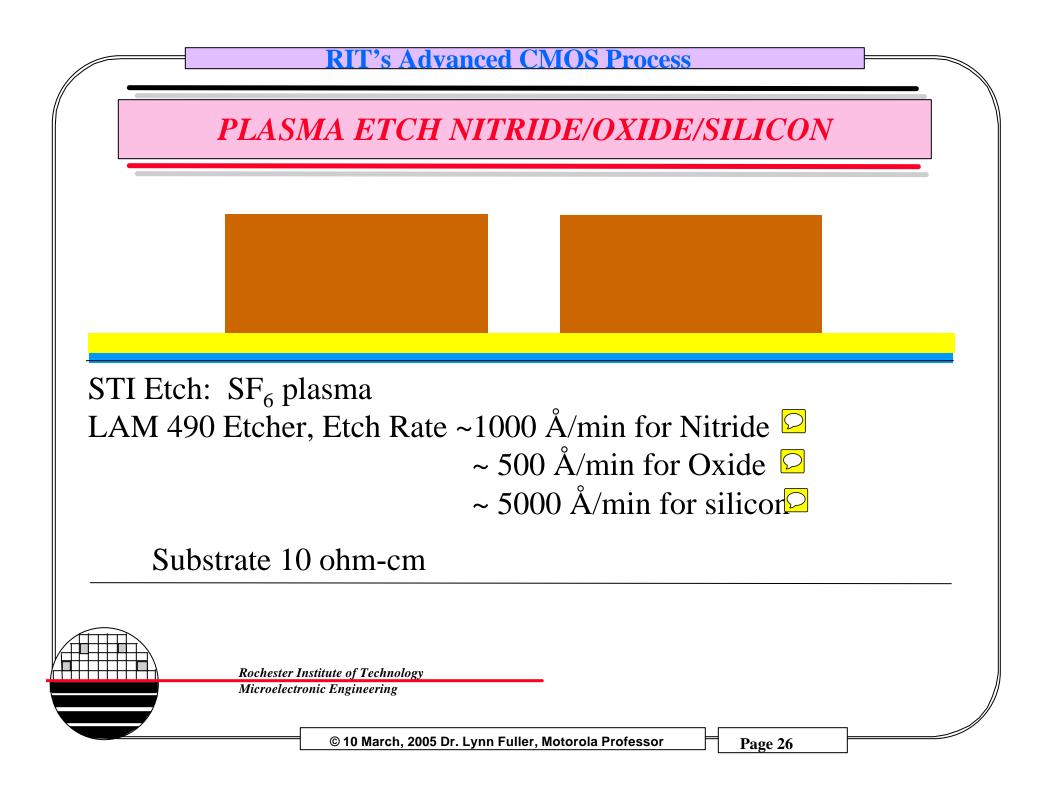

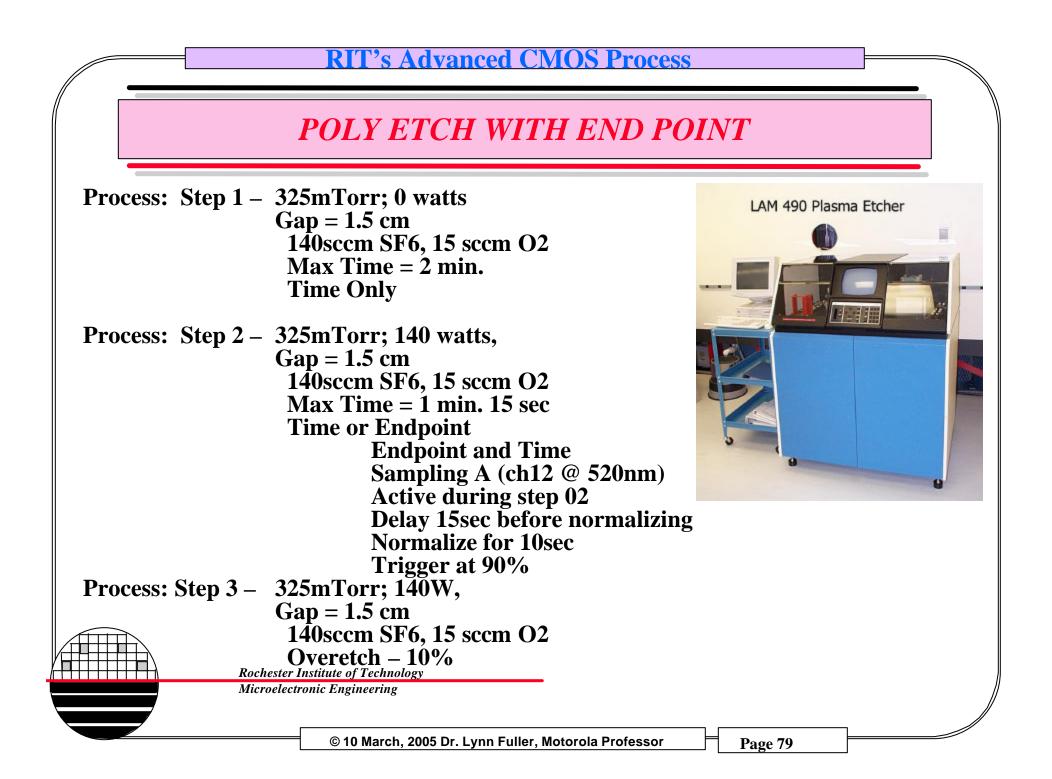

# PLASMA ETCH TOOL

Lam 490 Etch Tool Plasma Etch Nitride (~ 1500 Å/min) SF6 flow = 200 sccm Pressure= 260 mTorr Power = 125 watts Time=thickness/rate

Use end point detection capability This system has filters at 520 nm and 470 nm. In any case the color of the plasma goes from pink/blue to white/blue once the nitride is removed.

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

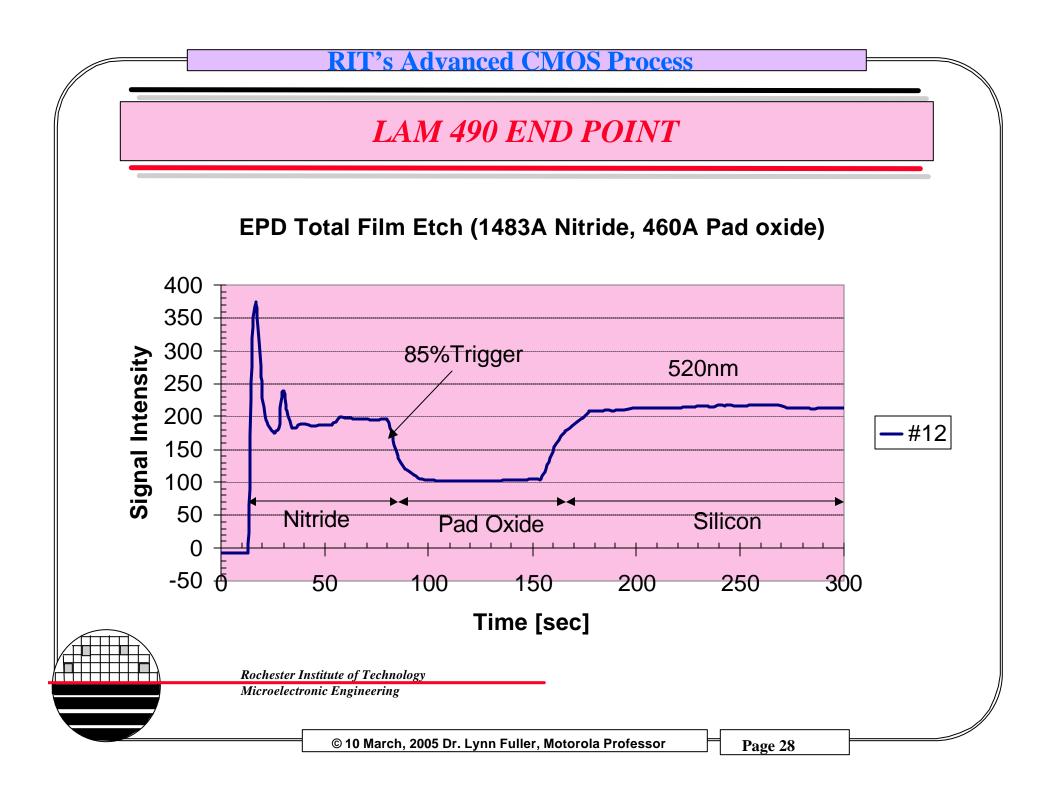

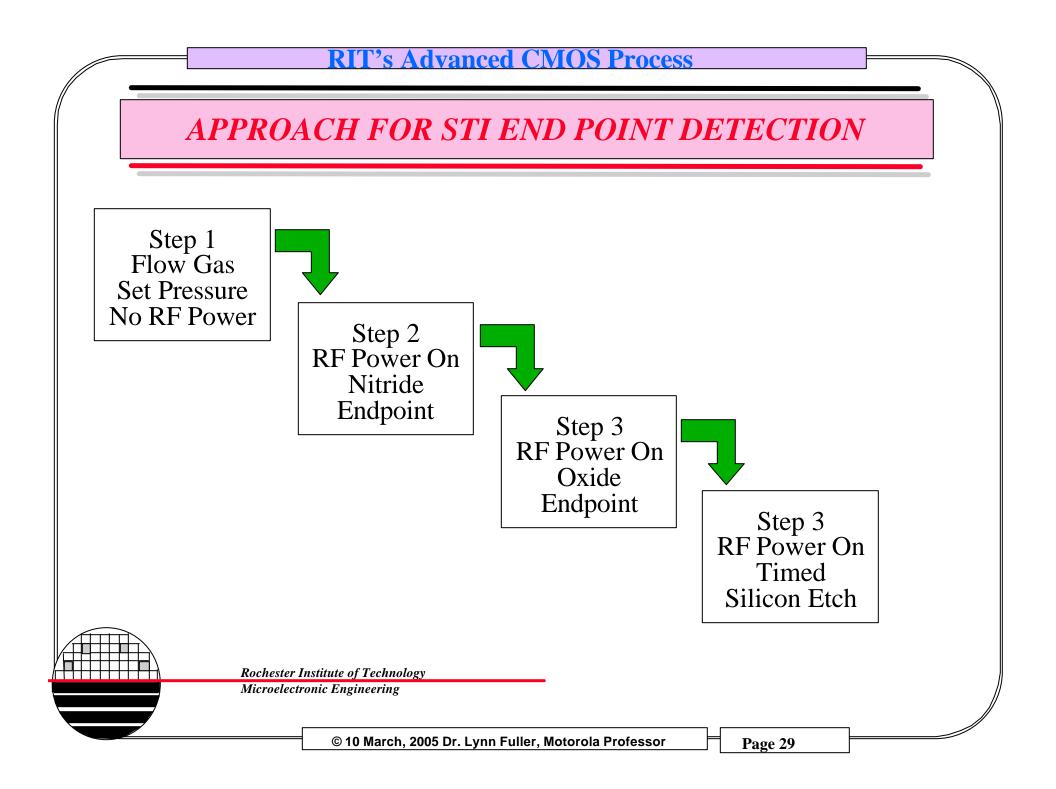

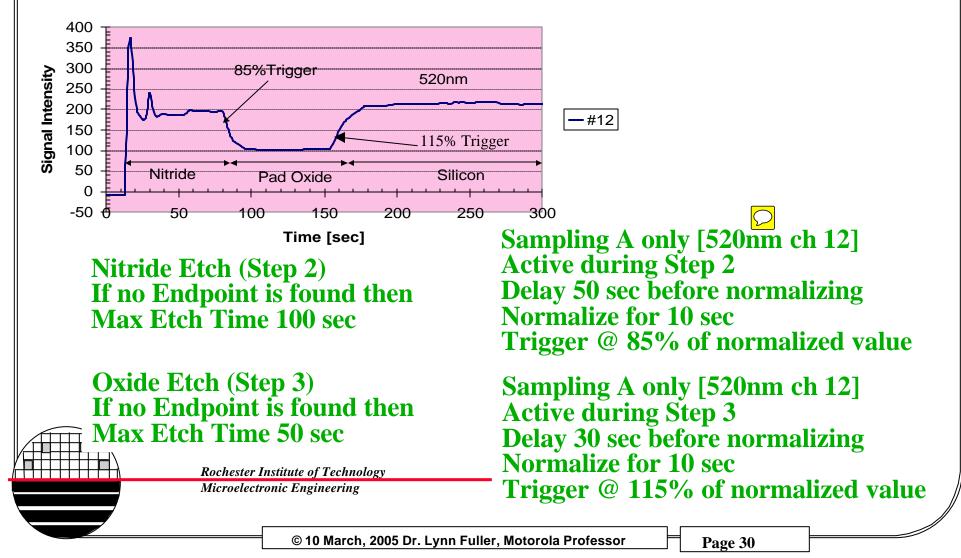

## **SELECTING LAM 490 END POINT PARAMETERS**

EPD Total Film Etch (1483A Nitride, 460A Pad oxide)

### FINALIZE STI ETCH RECIPE

- Process: Step 1 260mTorr; 0 watts 200sccm SF6, Max Time = 2 min Time Only

- Process: Step 2 260mTorr; 125 watts, 200sccm SF6, Max Time = 1min 40sec Endpoint and Time Sampling A (ch12 @ 520nm) Active during step 02 Delay 50sec before normalizing Normalize for 10sec Trigger at 85%

- Process: Step 3 260mTorr; 125 watts, 200sccm SF6, Max Time = 50sec Endpoint and Time Sampling A (ch12 @ 520nm) Active during step 03 Delay 30sec before normalizing Normalize for 10sec Trigger at 115%

- Process: Step 4 260mTorr; 125W, 200sccm SF6, Time Only, Max Time = 50 sec

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

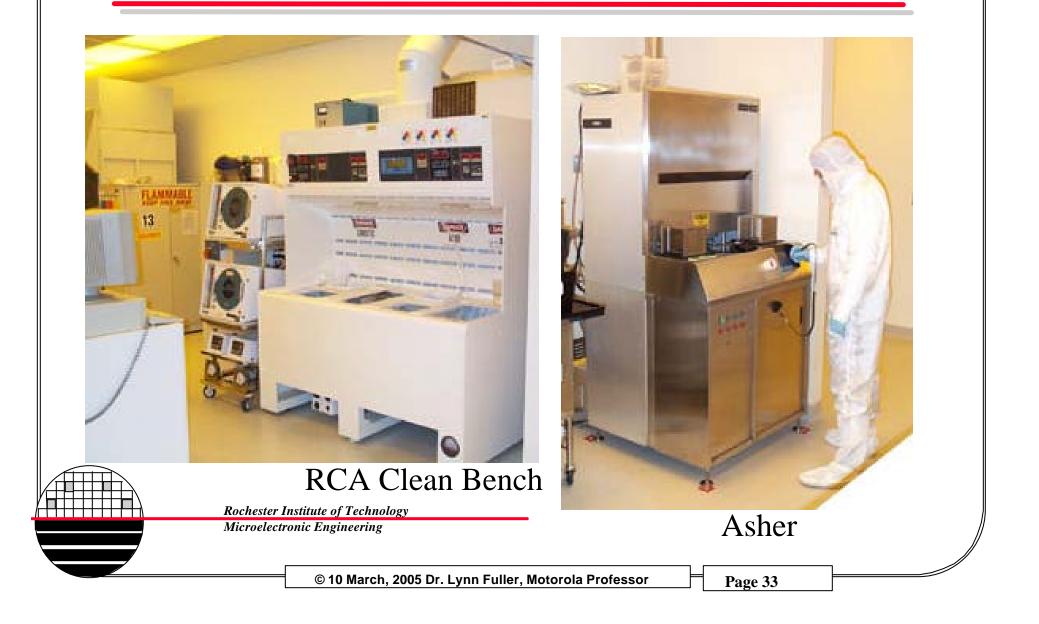

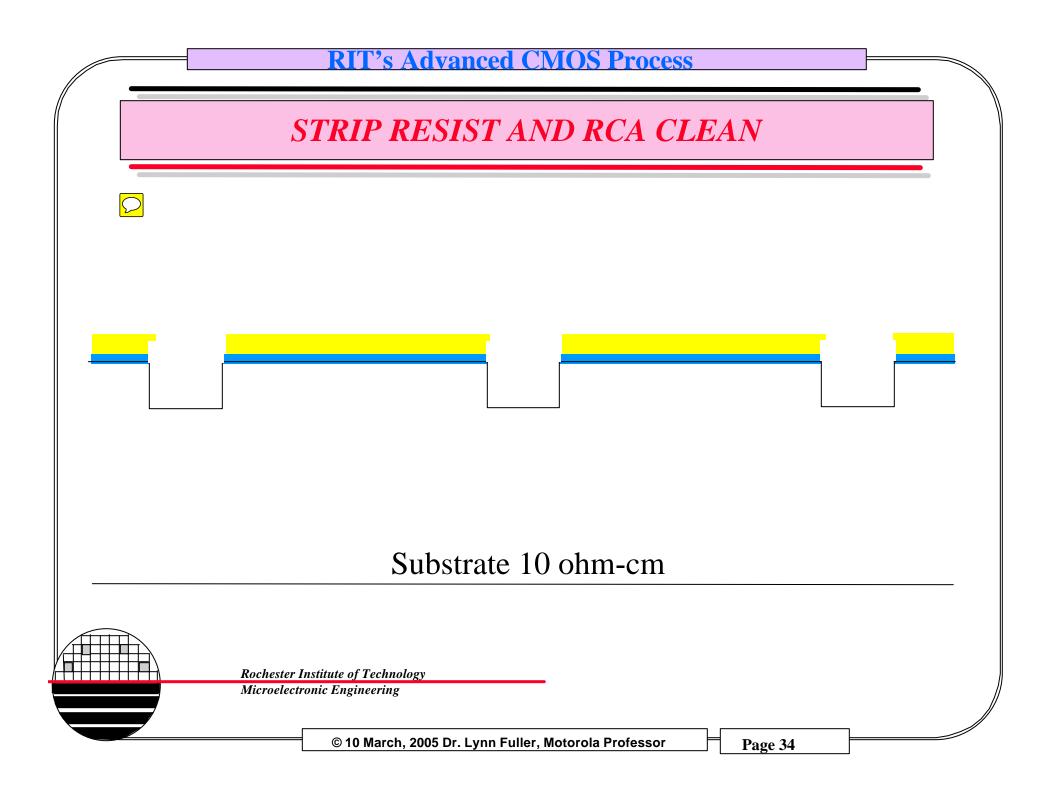

## MEGASONIC RCA CLEAN, SRD & ASHER

# **PECVD OXIDE FROM TEOS**

TEOS Program: (Chamber A) Step 1 Setup Time = 15 sec Pressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RFPower = 0 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 2 – Deposition  $\hat{\text{Dep Time}} = 55 \text{ sec } (5000 \text{ Å})$ Pressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RF Power = 205 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 3 – Clean Time = 10 secPressure = Fully Open Susceptor Temperature=390 C Susceptor Spacing= 999 mils RF Power = 50 watts TEOS Flow = 0 sccO2 Flow = 285 scc

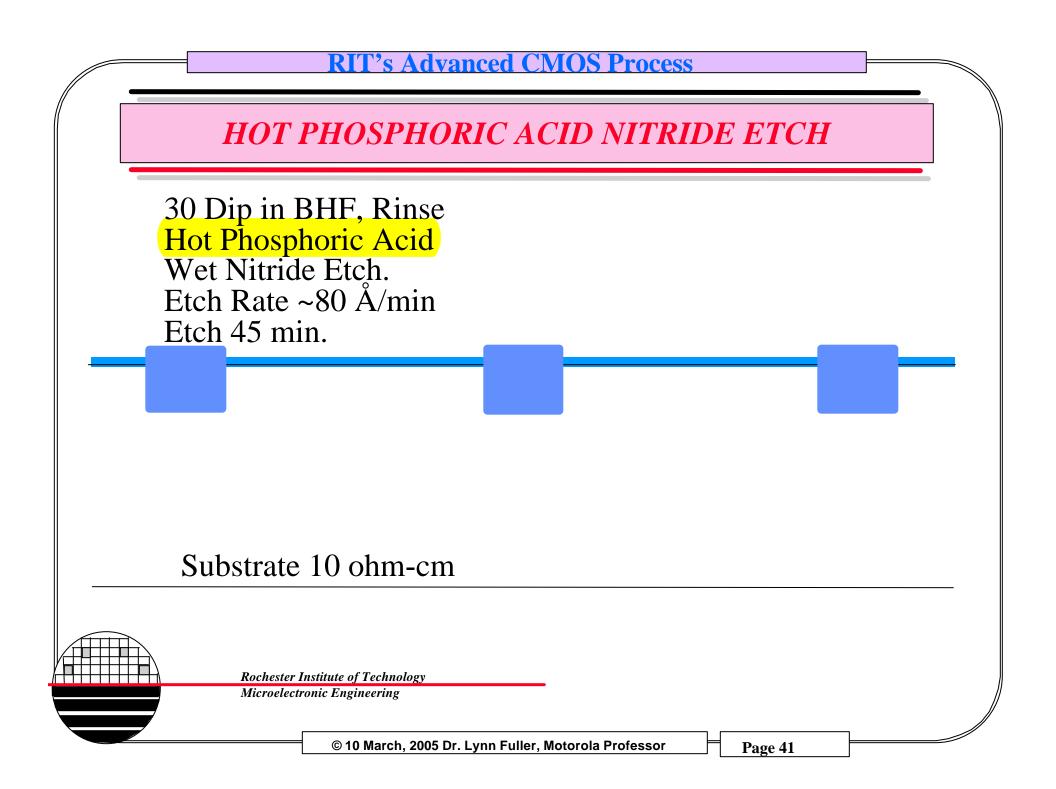

### HOT PHOSPHORIC ACID ETCH BENCH

KOH / Hot Phos Bench

- Include D1-D3

- Warm up Hot Phos pot to 175°

- Use Teflon boat to place wafers in acid bath

- 3500Å +/-500 → 90 minutes

- 1500Å +/- 500 → 45 minutes

- Etch rate of ~80 Å/min

- Rinse for 5 minutes in Cascade Rinse

- SRD wafers

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

# VARIAN 350 D ION IMPLANTER (4" AND 6" WAFERS)

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

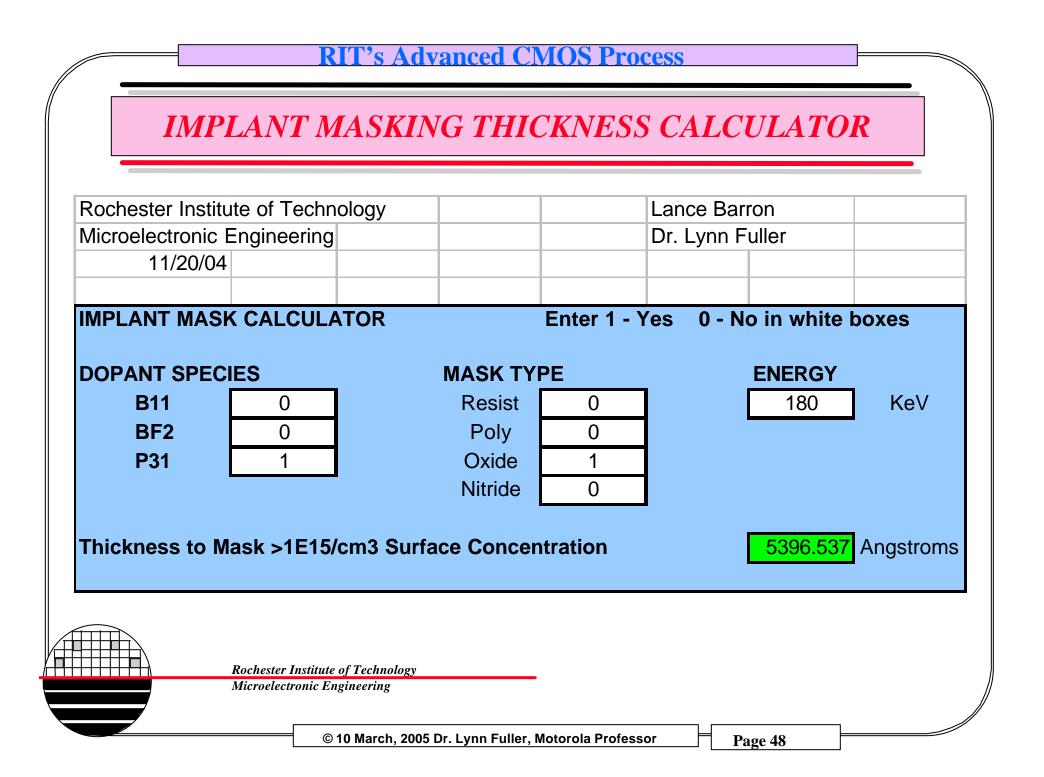

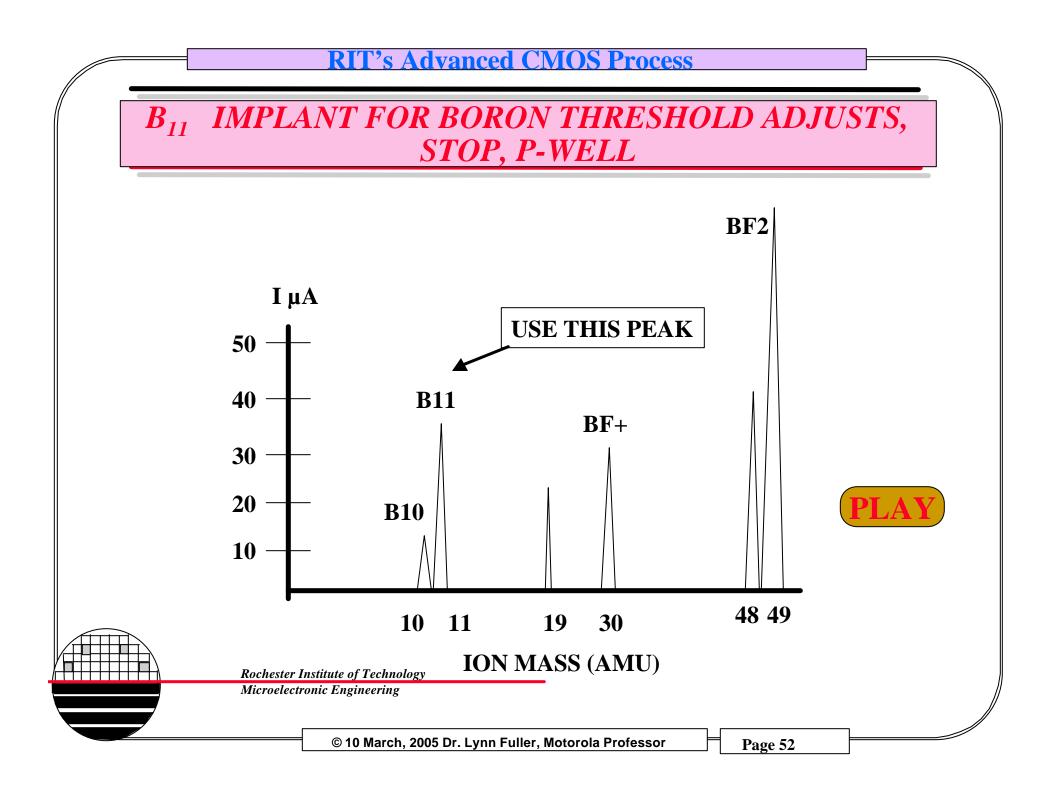

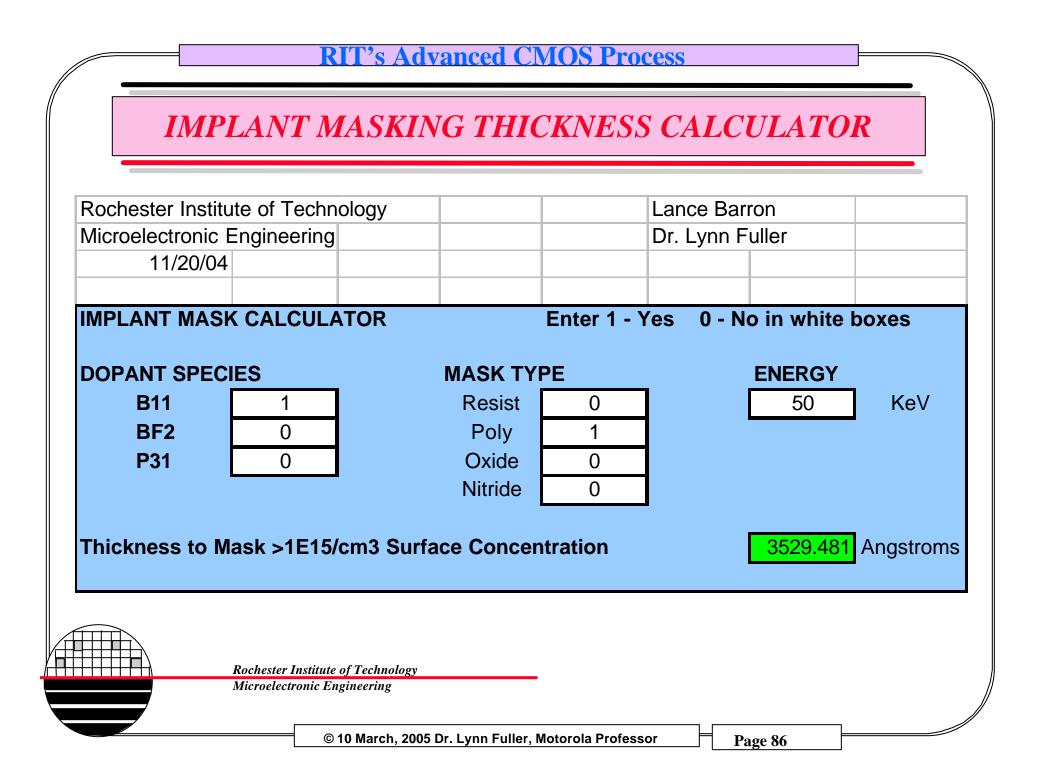

#### **RIT's Advanced CMOS Process IMPLANT MASKING THICKNESS CALCULATOR** Lance Barron **Rochester Institute of Technology** Microelectronic Engineering Dr. Lynn Fuller 11/20/04 IMPLANT MASK CALCULATOR Enter 1 - Yes 0 - No in white boxes **DOPANT SPECIES MASK TYPE** ENERGY **B11** Resist 0 KeV 1 125 BF2 0 0 Poly **P31** 0 Oxide 1 Nitride 0 Thickness to Mask >1E15/cm3 Surface Concentration 5371.71 Angstroms **Rochester Institute of Technology** Microelectronic Engineering © 10 March, 2005 Dr. Lynn Fuller, Motorola Professor Page 53

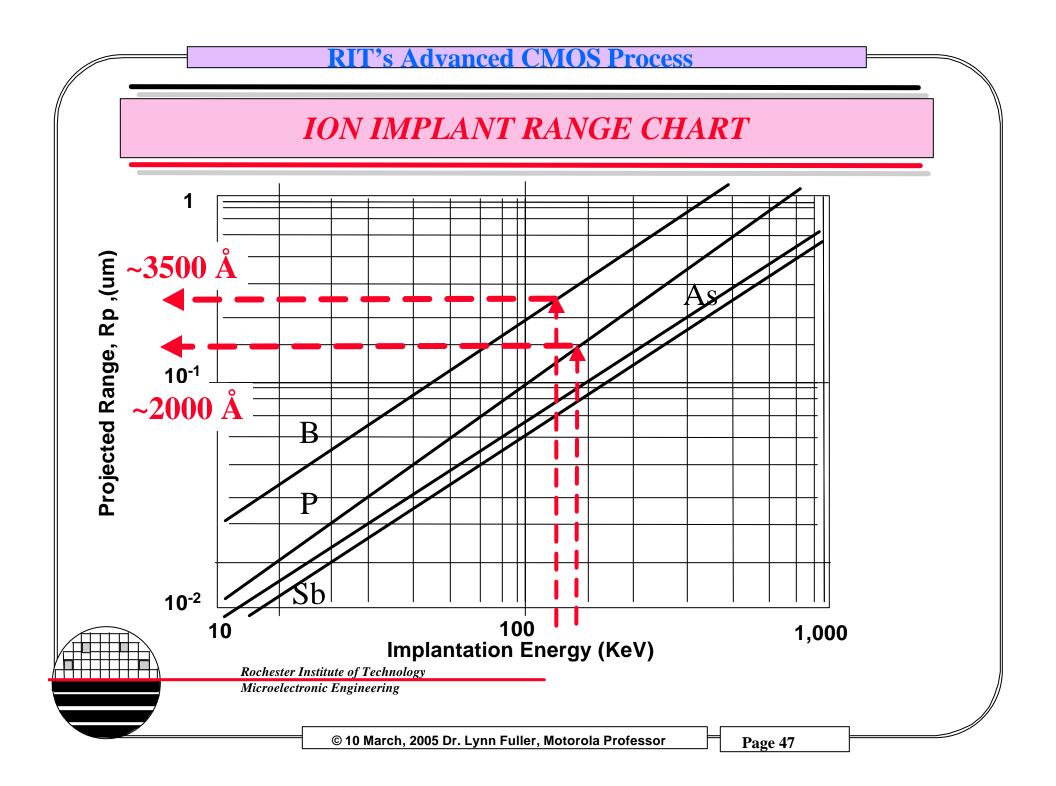

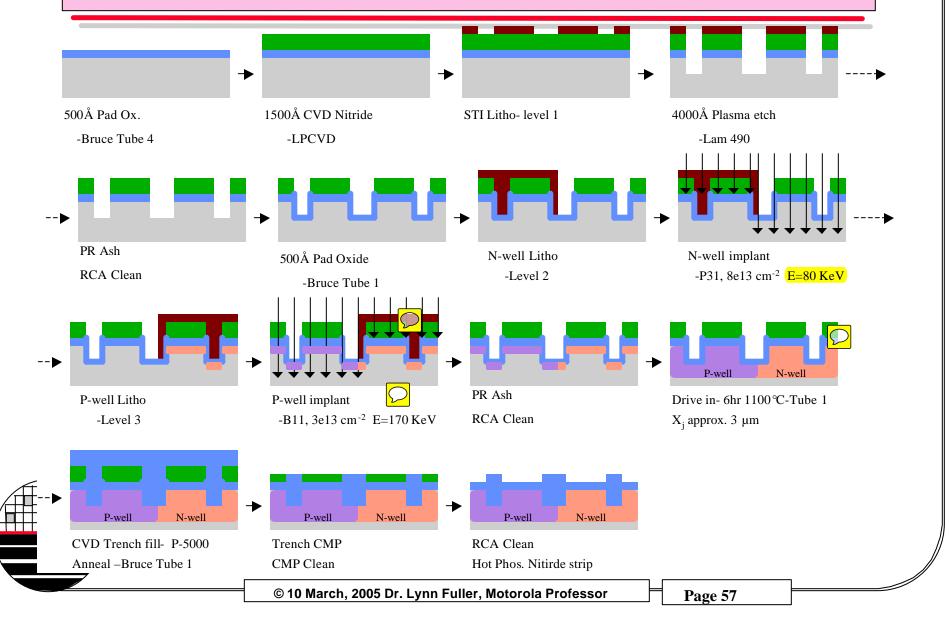

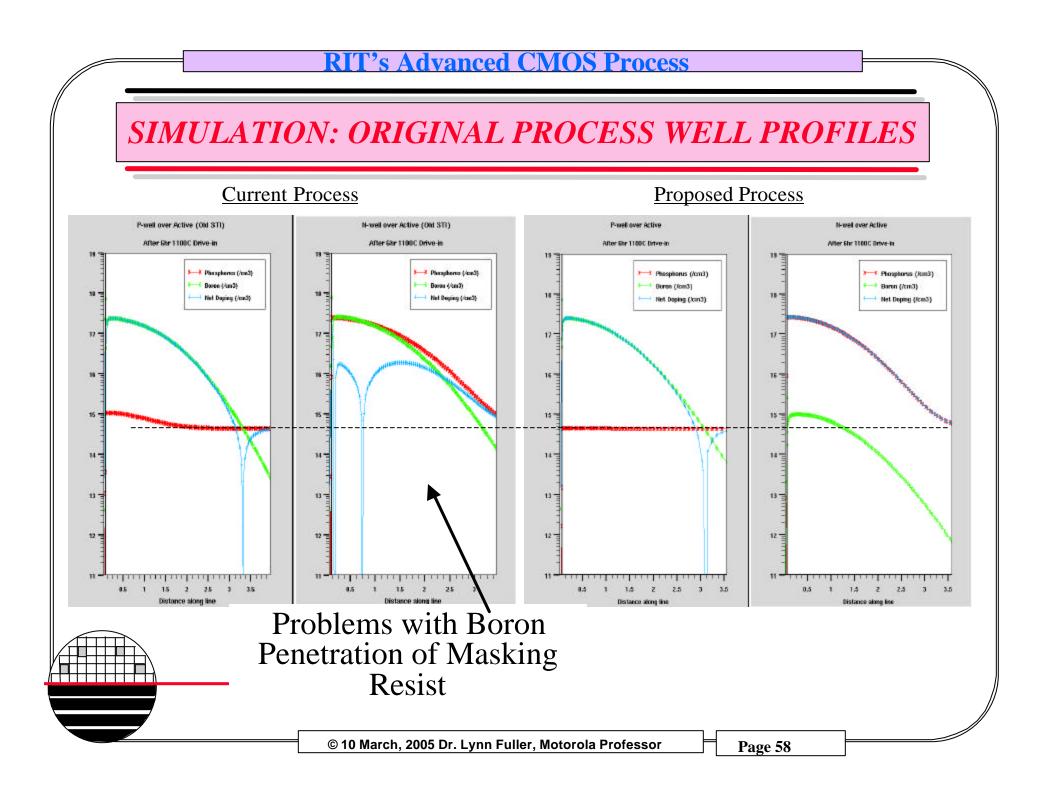

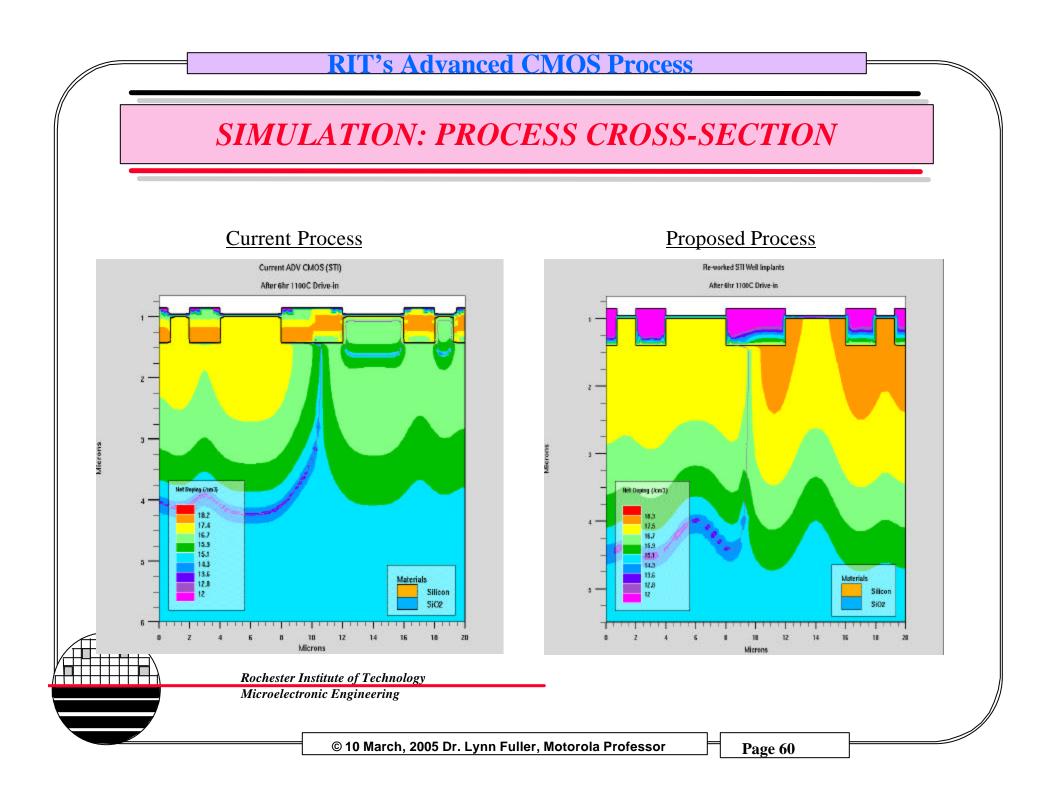

### ALTERNATIVE APPROACH FOR WELL FORMATION IN ADVANCED CMOS PROCESS

The current Adv-CMOS process calls for ion implanting the well through the filled trenches. This requires exact trench depths, exact CMP stop, and high energy implants. The normal photoresist is not thick enough to block these high energy implans, 180KeV for P31 and 150KeV for B11. This project investigated implanting the wells prior to trench fill and CMP. Using SILVACO ATHENA simulations a set of implant conditions was determined to give a well with the correct surface concentration, well junction depth and sheet resistance. The wells also need to be continuous under the trench isolation so that several devices can be placed in a single well with a single well potential. In addition our ion implanter has difficulty at high energy so lower energy implants would be useful.

Rochester Institute of Technology Microelectronic Engineering Jonathan Reese February 22, 2005

### WELL PARAMETERS

|               | Design<br>Parameters | Old Process<br>Simulation | New Process<br>Simulation |        |

|---------------|----------------------|---------------------------|---------------------------|--------|

| N well        |                      |                           |                           |        |

| Dose          | 3E13                 | 3E13                      | 3E13                      |        |

| Energy        |                      | 180                       | 170                       | Lower  |

| Surface Conc. | ~1E17                | 2.4E17                    | 1.08E17                   | Better |

| N well Xj     | ~3.0                 | 4.0#                      | 3.5                       | Better |

| P well        |                      |                           |                           |        |

| Dose          | 3E13                 | 3E13                      | 8E13                      |        |

| Energy        |                      | 150                       | 80                        | Lower  |

| Surface Conc. | ~1E17                | 3.6E16                    | 1.0E17                    | Better |

| P well Xj     | ~3.0                 | 3.3                       | 3.1                       | Better |

# If Boron penetration into N-well can be eliminated

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

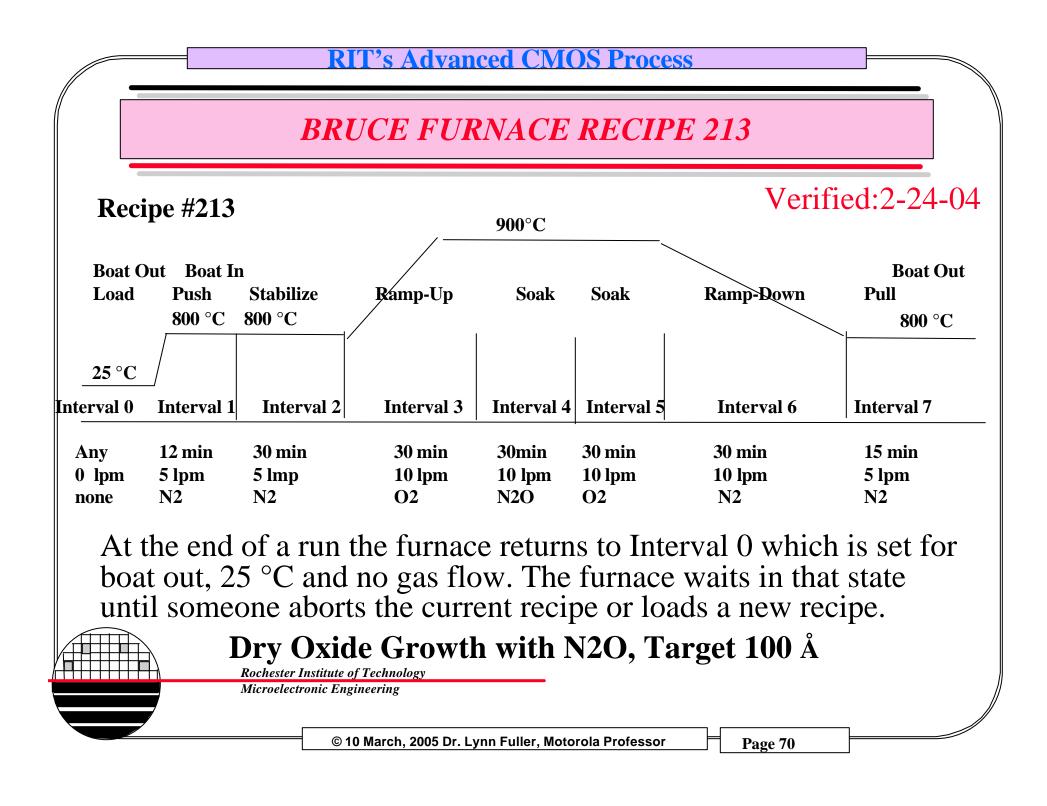

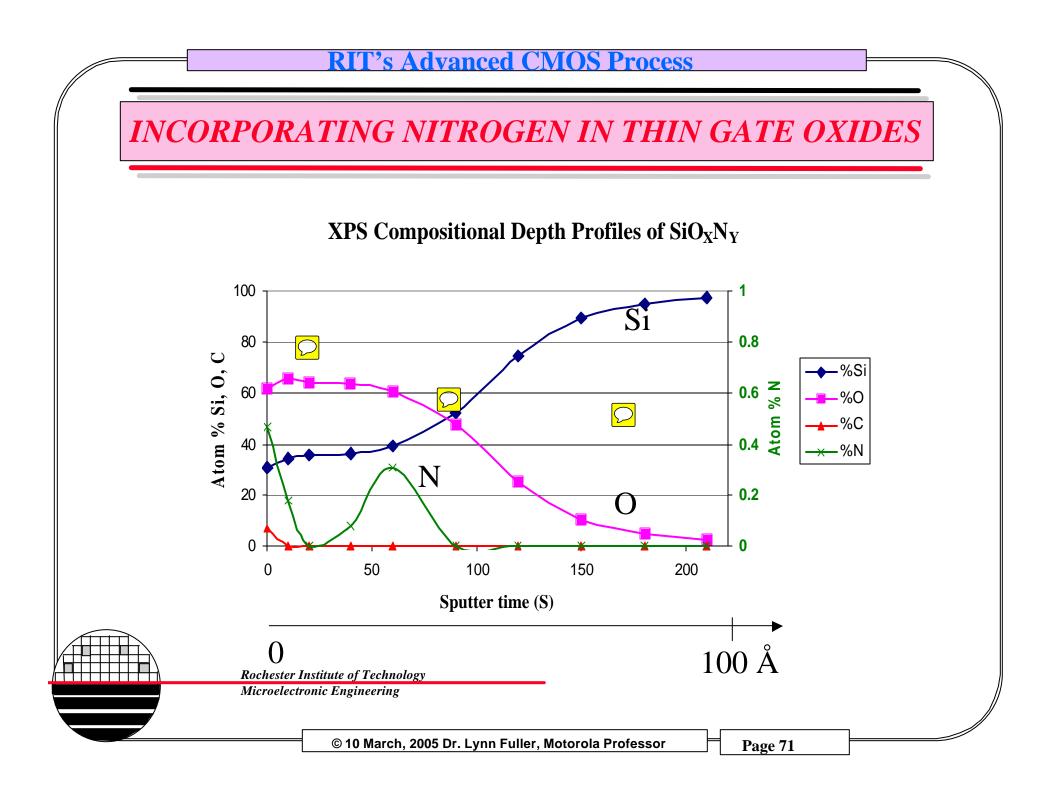

## **INCORPORATING NITROGEN IN THIN GATE OXIDES**

In todays deep sub-micron transistors the pMOSFET normally has p+Poly for the gate material. The gate oxide is 100Å or less. The p+ dopant is normally Boron and Boron diffuses quickly (compared to Phosphorous) through oxides. Since the gate oxides are thin this could allow Boron to diffuse through the gate oxide and dope the channel causing the transistors to not function correctly. If some nitrogen is incorporated in the gate oxide the diffusion of Boron is much lower. This project involved developing a gate oxide recipe that will result in nitrogen incorporation in the gate oxide. The recipe included 30 min anneal in N2, 30 min oxynitride growth in N2O and 30 min oxide growth in O2, all at 900 °C. The gate oxides were evaluated at RIT using the ellipsometer (looking for index of refraction in between 1.45 (oxide) and 2.00 (nitride) and thickness near 100Å. The same wafers were also sent to Kodak for XPS analysis to give information on nitrogen content in the oxide.

Rochester Institute of Technology

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

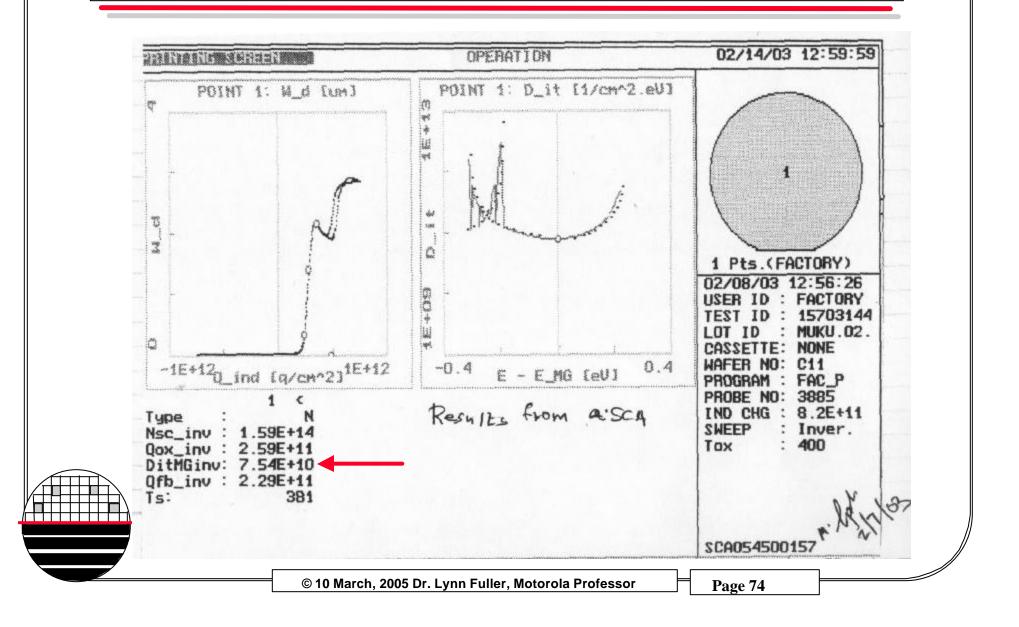

**RIT's Advanced CMOS Process** MEASURE C1 AND C2 ON SCA-2500 **Login: FACTORY Password: OPER** <F1> Operate <F1> Test Center the wafer on the stage Select (use arrow keys on the numeric pad (far right on the keyboard) space bar, page up, etc) **PROGRAM = FAC-P or FAC-N** LOT ID = HAWAIIWAFER NO. = C1 **TOX = 250 (from nanospec)** <F12> start test and wait for measurement. <Print Screen> print results <F8> exit and log off <ESC> can be used anytime, but wait for current test to be completed **Rochester Institute of Technology** Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

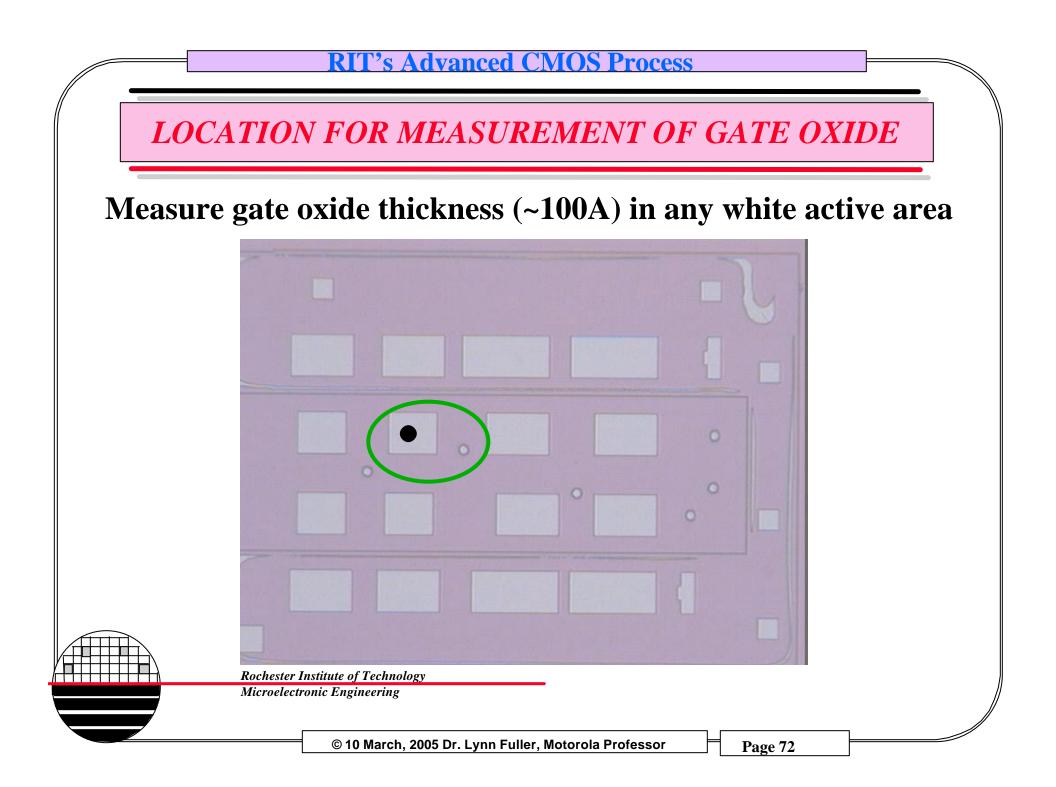

## SCA MEASUREMENT OF GATE OXIDE

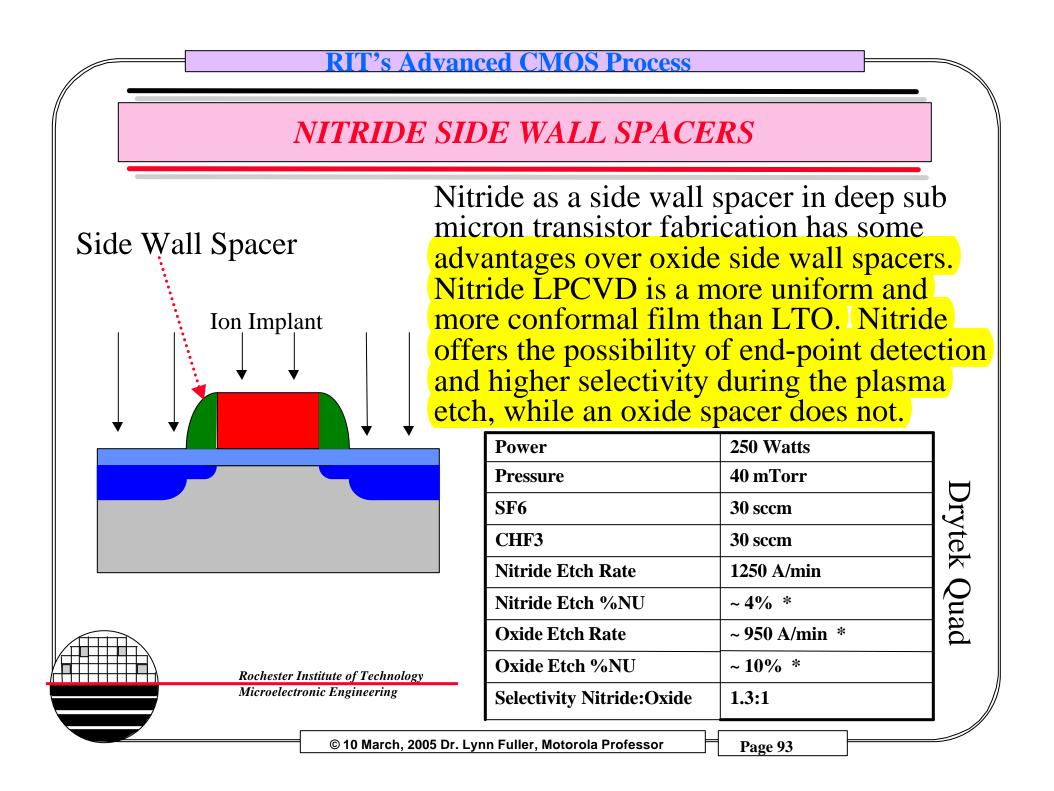

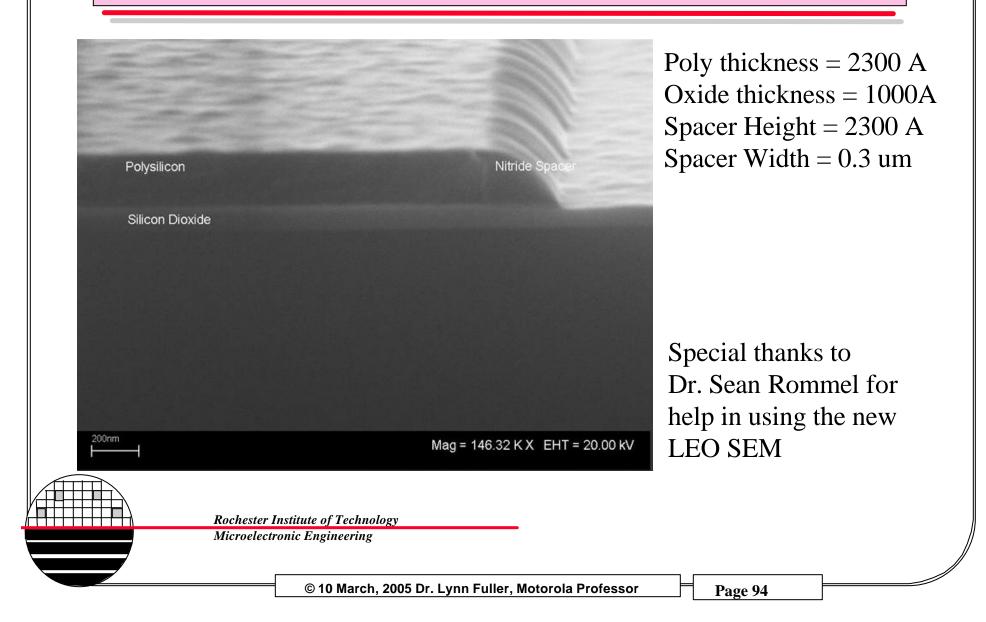

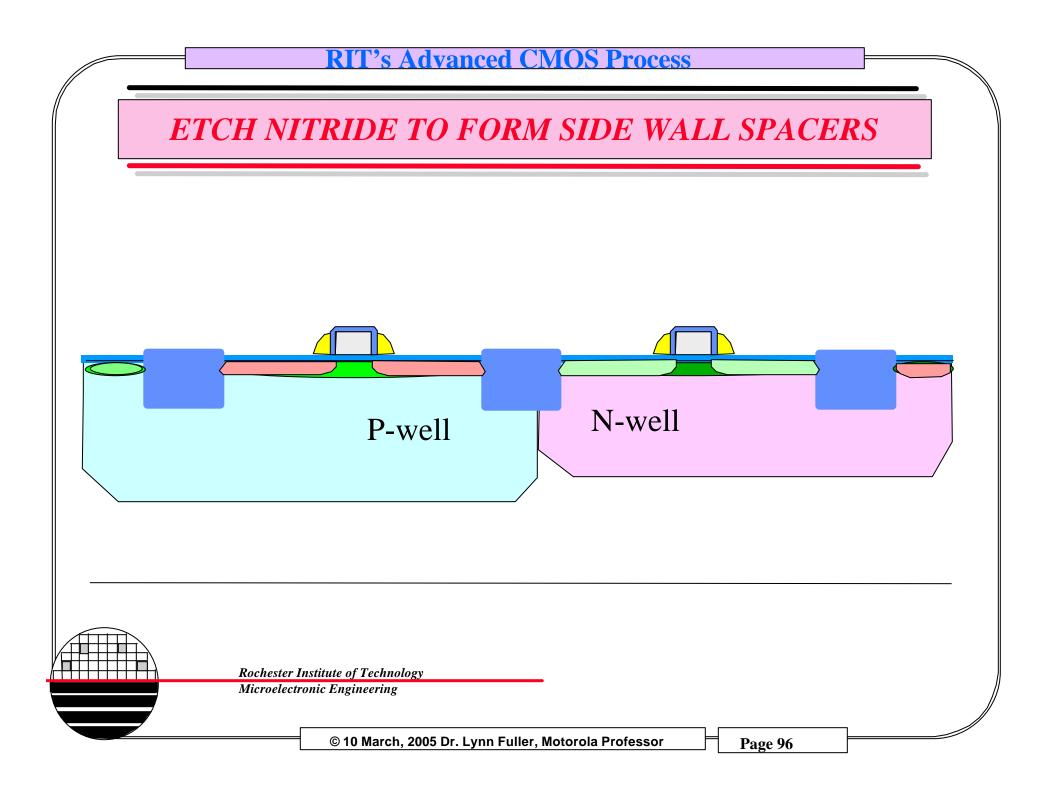

## **NITRIDE SIDE WALL SPACERS**

## SIDE WALL SPACER ETCH IN DRYTEK QUAD

Anisotropic Nitride Etch Drytek Quad Recipe FACSPCR 30 sccm SF6 30 sccm CHF3 Power = 250 watts Pressure = 40 mTorr Etch Rate = 125 nm/min

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

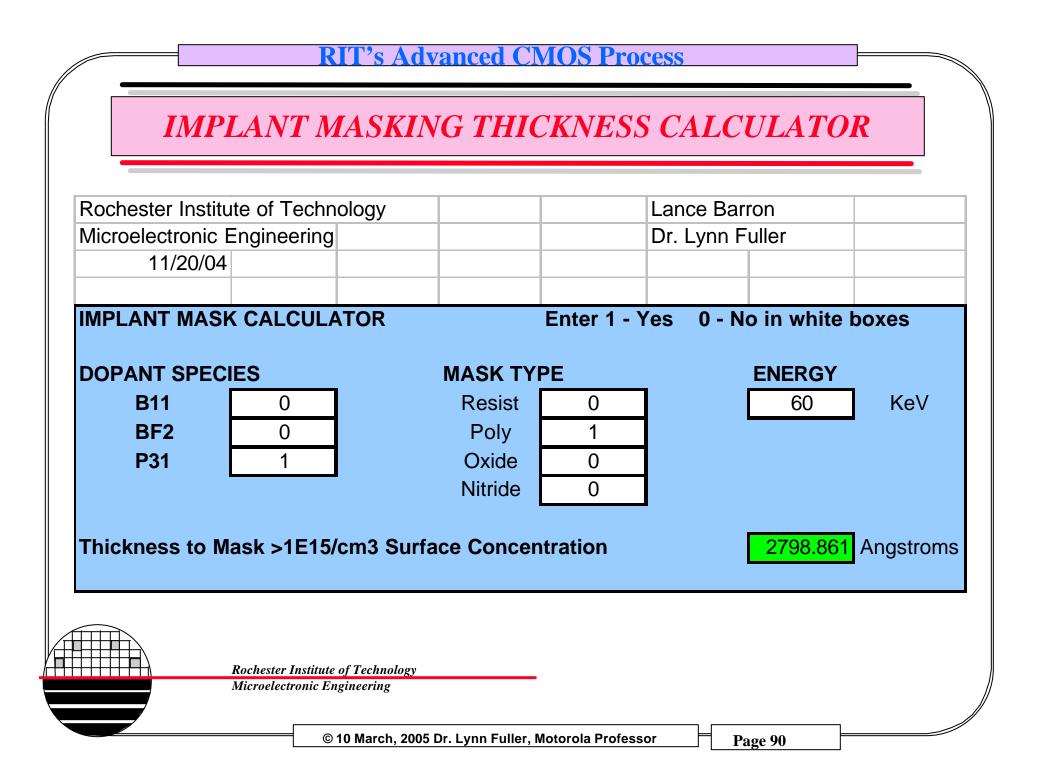

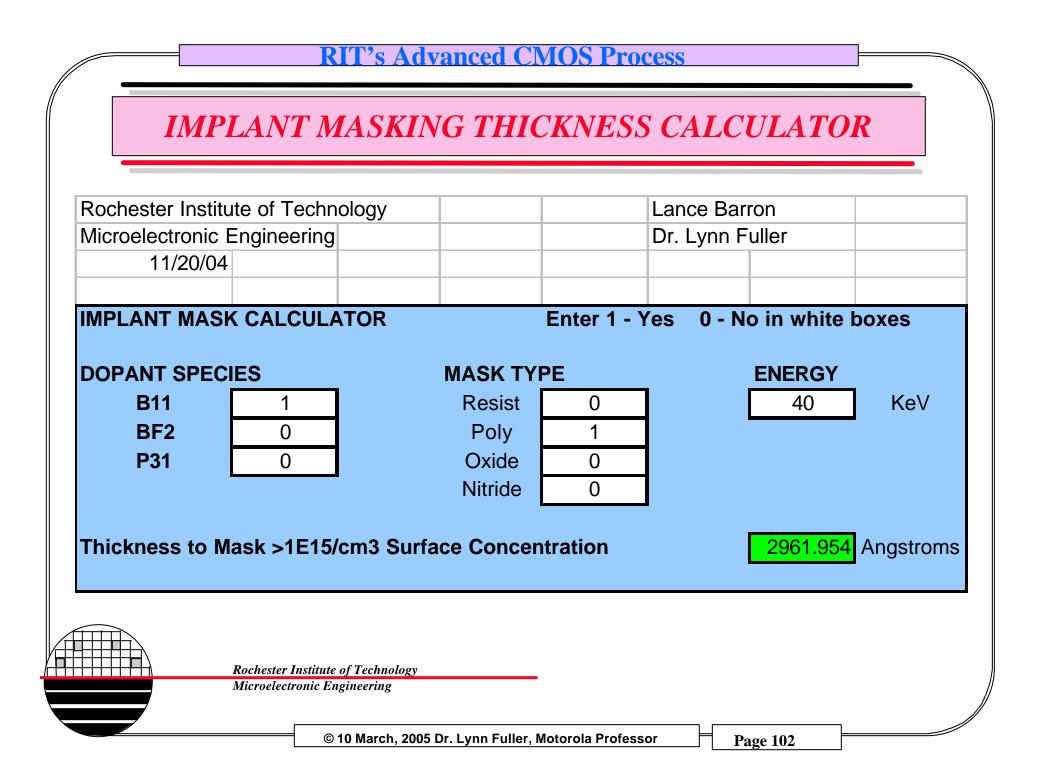

#### **RIT's Advanced CMOS Process IMPLANT MASKING THICKNESS CALCULATOR** Rochester Institute of Technology Lance Barron **Microelectronic Engineering** Dr. Lynn Fuller 11/20/04 Enter 1 - Yes 0 - No in white boxes IMPLANT MASK CALCULATOR **DOPANT SPECIES MASK TYPE ENERGY B11** Resist KeV 0 0 60 BF2 0 Poly 1 **P31** Oxide 0 Nitride 0 Thickness to Mask >1E15/cm3 Surface Concentration 2798.861 Angstroms **Rochester Institute of Technology** Microelectronic Engineering © 10 March, 2005 Dr. Lynn Fuller, Motorola Professor Page 98

# TiSi SALACIDE PROCESS

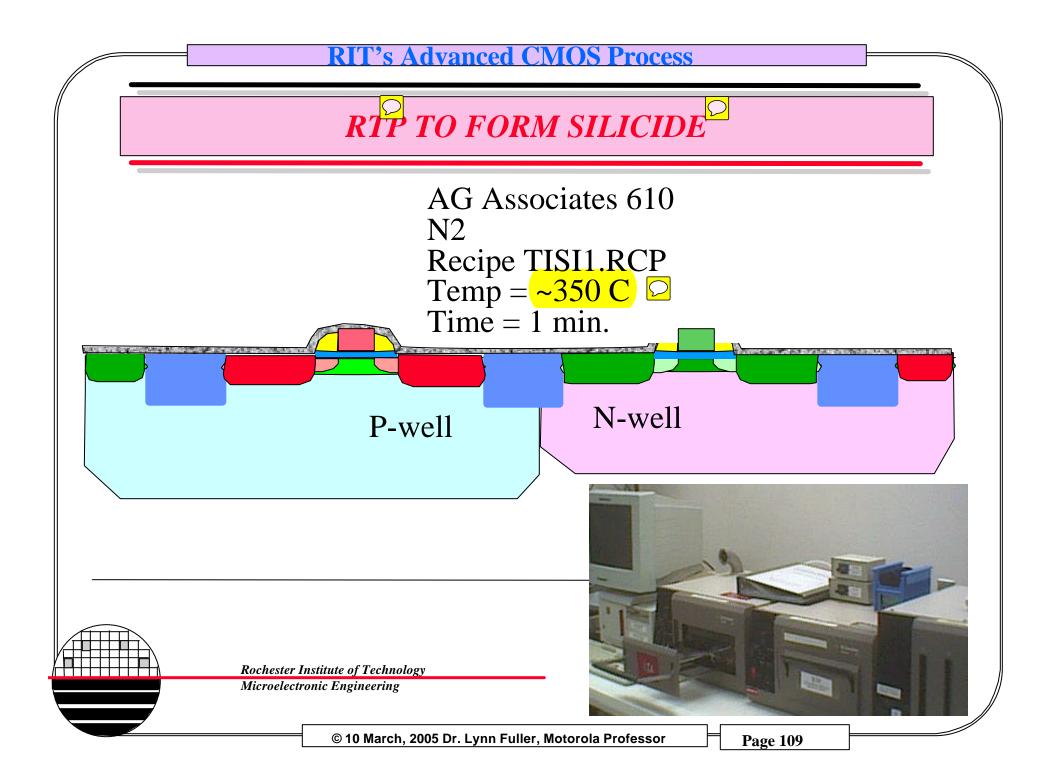

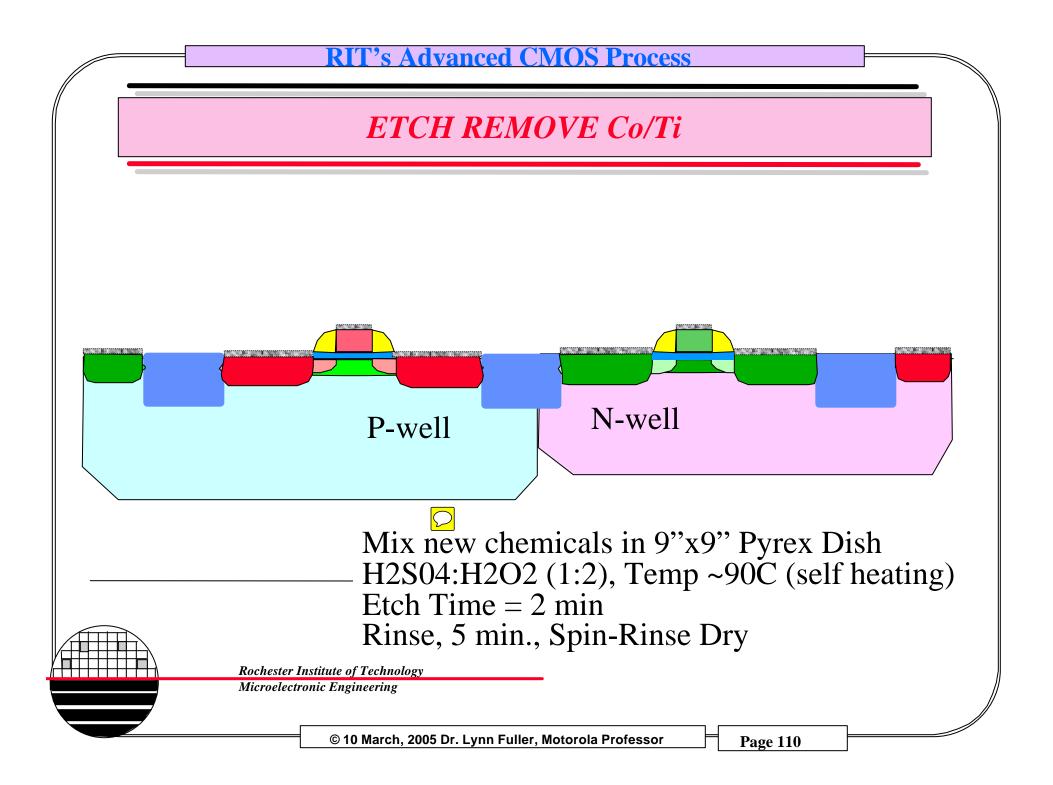

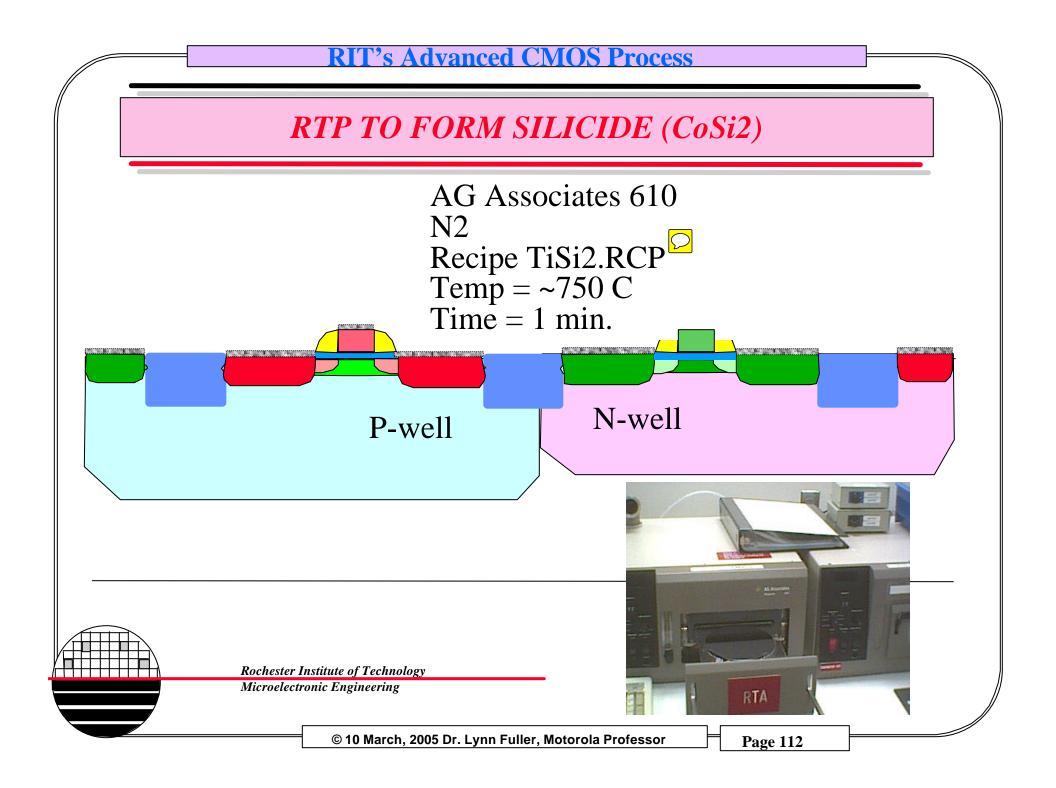

Forming a metal silicide helps reduce the resistance of the polysilicon interconnects and reduces the sheet resistance of the drain/source areas of the transistor. In deep sub-micron CMOS the nMOSFET transistor has n + poly and the pMOSFET has p + poly. O Normally the poly is doped by ion implantation at the same time the drain and sources is implanted. In this case it is essential to form a silicide to reduce the sheet resistance of the poly and to connect n+ and p+ poly where ever they meet. SALICIDE is an acronym for self-aligned silicide and can be achieved with the following process. Ti (or some other metal) is sputtered on the wafer. It is heated in vacuum or N2 atmosphere to form TiSi where ever the Ti metal is in contact with silicon but not where it is in contact with silicon dioxide. The wafer is etched in sulfuric acid and hydrogen peroxide mixture which removes the metal from the oxide regions leaving TiSi self aligned on the silicon areas. Further heat treating at a higher temperature can convert TiSi to TiSi2 which is lower sheet resistance.

## TiSi SALACIDE PROCESS

## **Sputtering of Titanium:**

4" Target, 350 watts, 5 mTorr, 10 min pre-sputter, 10 min sputter, Rate = 100Å/min

8" Target, 750 watts, 5 mTorr, 10 min pre-sputter, 10 min sputter, Rate = 176 Å/min

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

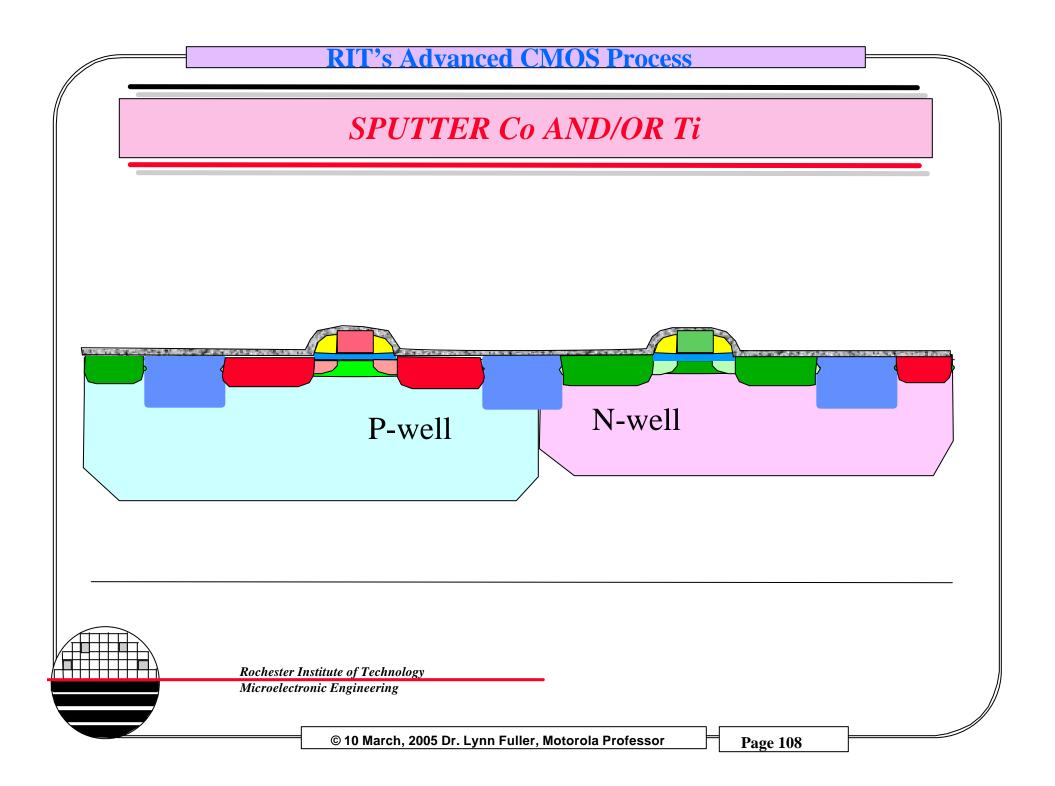

## SPUTTER OF Co AND Ti FOR CoSi2 SALACIDE

Total Thickness = 700 Å Dilute HF dip (50:1) 30 sec Spin Rinse Dry Sputter in CVC601 Heater time, 20 min., 300 C Base Pressure <5E-6 Torr Presputter Co 5 min at 250 watts Sputter Co at 5 mTorr of Ar Time = 6 min. Presputter Ti 5 min at 1000 watts Sputter Ti at 5 mTorr of Ar Time = 17 min

## CVC 601 Sputter Tool

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

## TiSi SALACIDE PROCESS

### **Etching of Ti Metal:**

Heat the Sulfuric Acid:Hydrogen Peroxide (1:2) mixture on a hotplate to 100°C (set plate temperature to 150°C)

Etch for 1 min 30 sec. This should remove the Ti that is on top of the silicon dioxide but not remove TiSi that was formed on the polysilicon and D/S regions. It also removes unreacted Ti metal over the TiSi on the poly and D/S regions.

Courtesy of SMFL

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

### **PECVD OXIDE FROM TEOS**

**TEOS Program:** (Chamber A) Step 1 Setup Time = 15 secPressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RFPower = 0 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 2 – Deposition  $\hat{\text{Dep Time}} = 55 \text{ sec } (5000 \text{ Å})$ Pressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RF Power = 205 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 3 – Clean Time = 10 secPressure = Fully Open Susceptor Temperature= 390 C Susceptor Spacing= 999 mils RF Power = 50 watts TEOS Flow = 0 sccO2 Flow = 285 scc

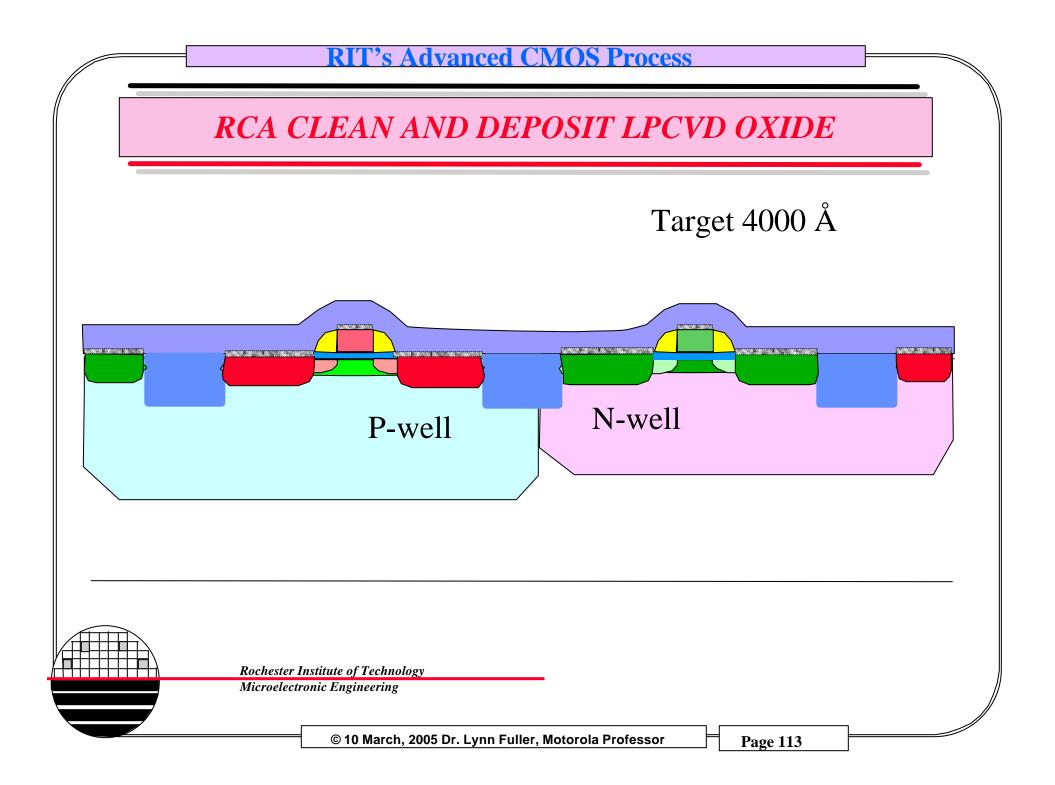

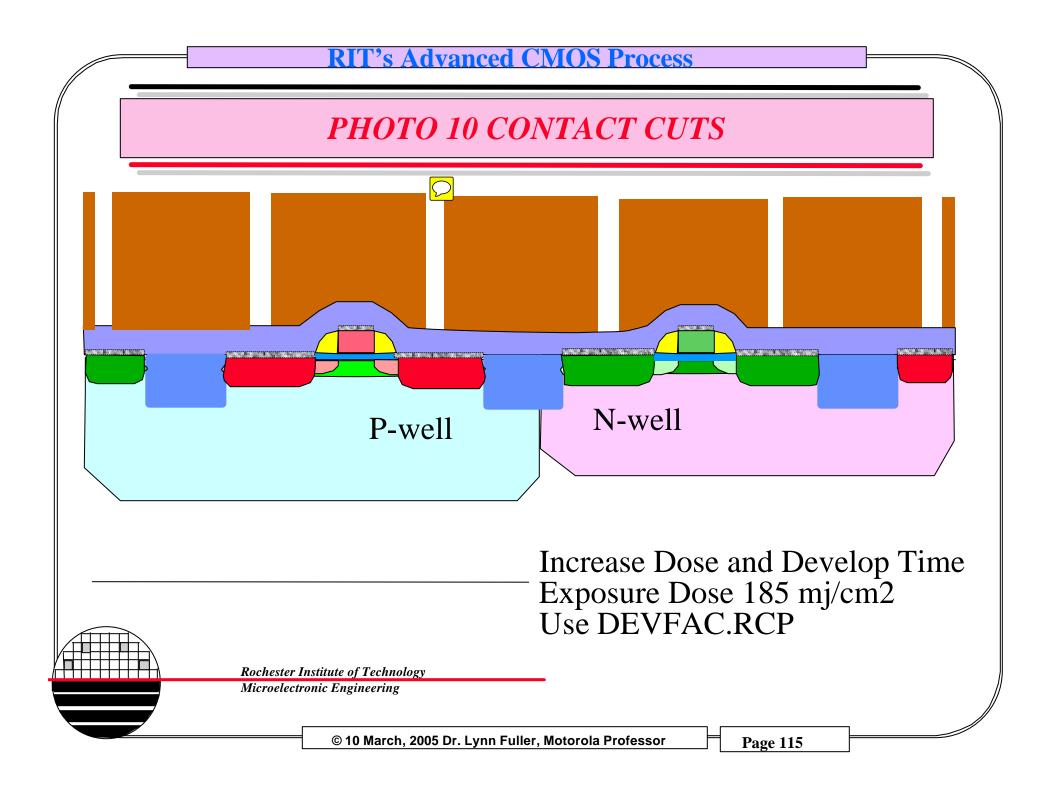

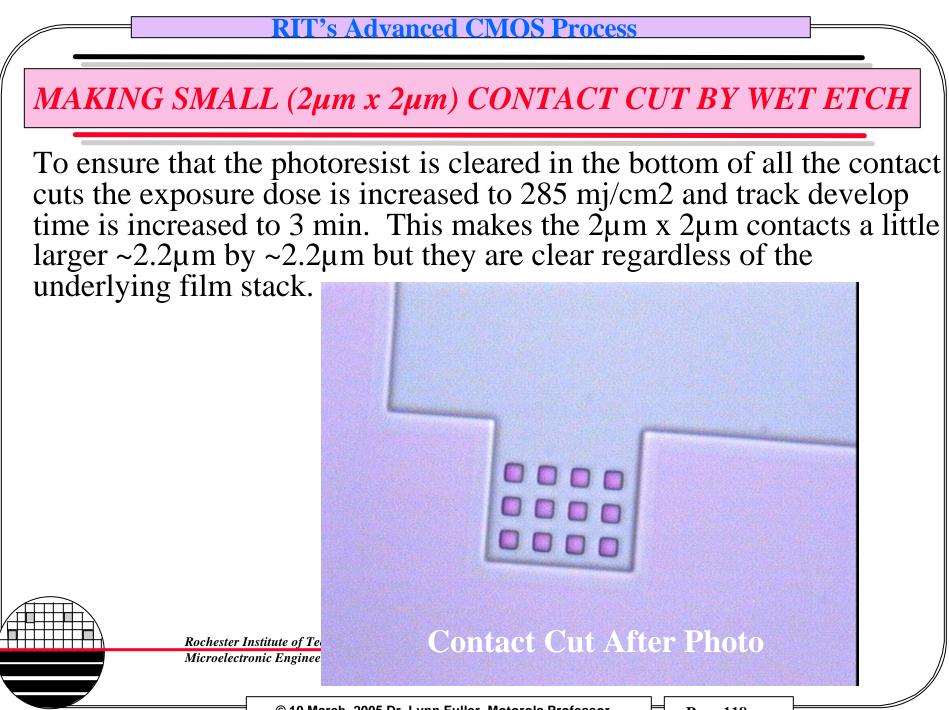

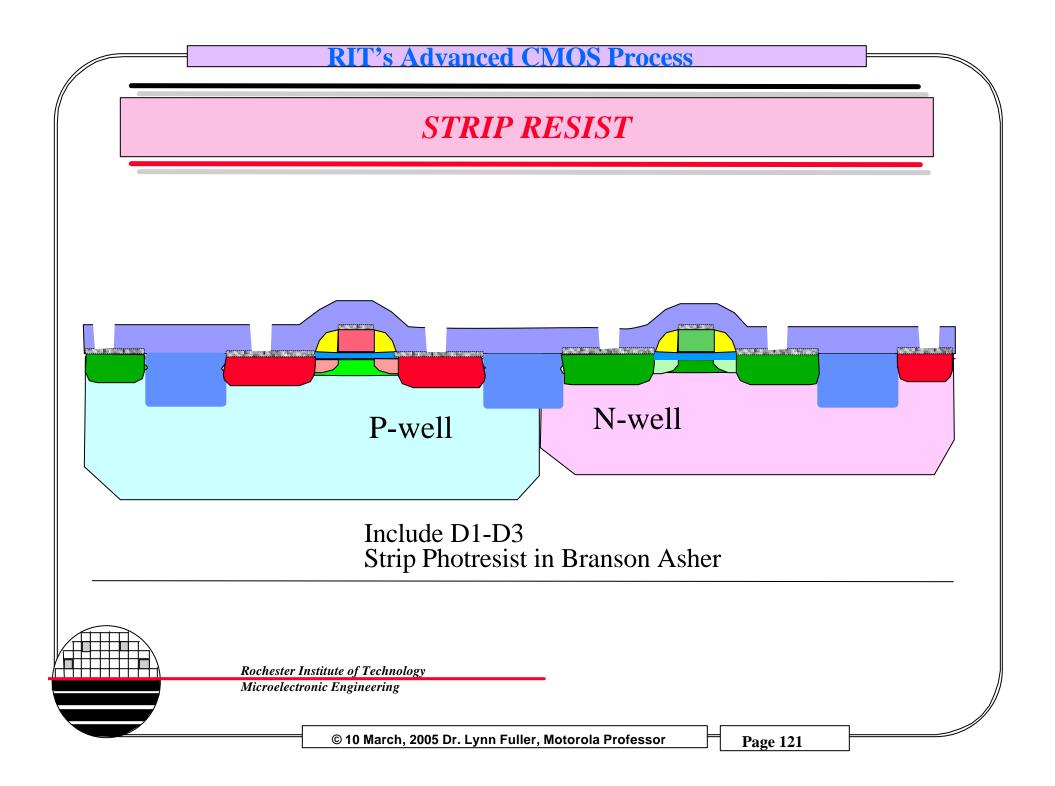

# MAKING SMALL (2µm x 2µm) CONTACT CUT BY WET ETCH

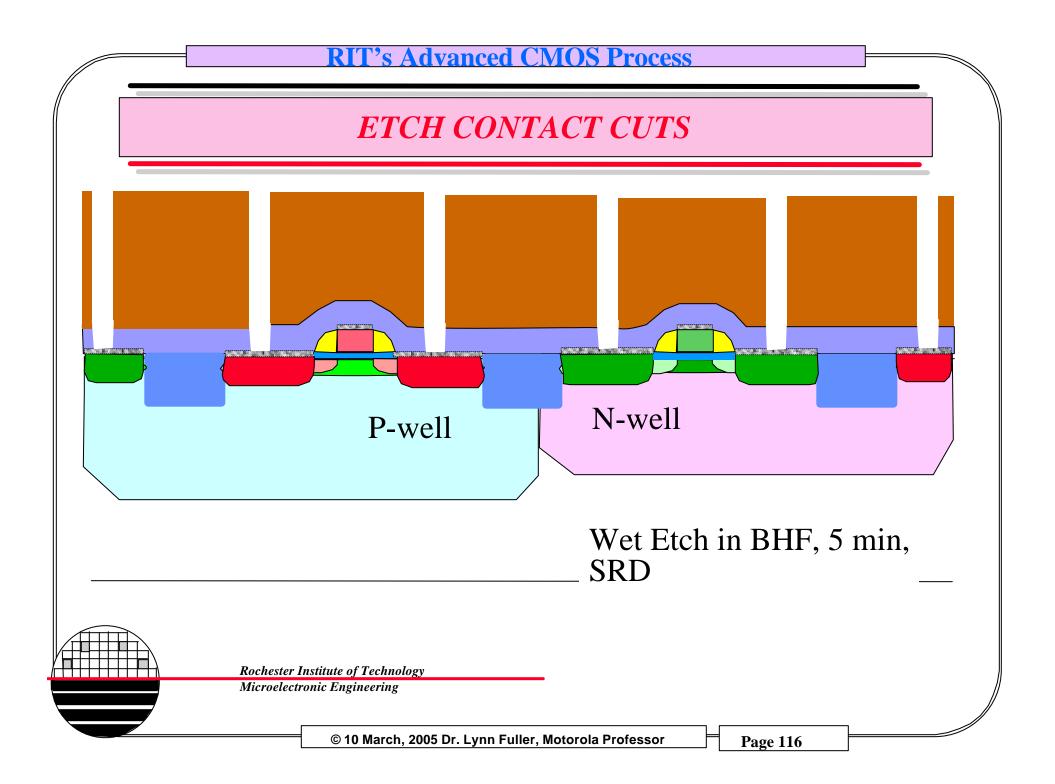

Contact Cut Lithography is difficult because of the complicated film stack. The contacts are through 4000Å TEOS oxide on thermal oxide on poly on gate oxide. The poly has a silicide layer in the Advanced CMOS process. The poly thickness might be 4000Å or 6000Å. The TEOS may be annealed. Other contacts are to drain and source through 4000Å TEOS on thermally grown oxide of ~500Å (from poly reox step) plus gate oxide. The gate oxides are 330Å, 150Å, or 100Å depending on the exact process.

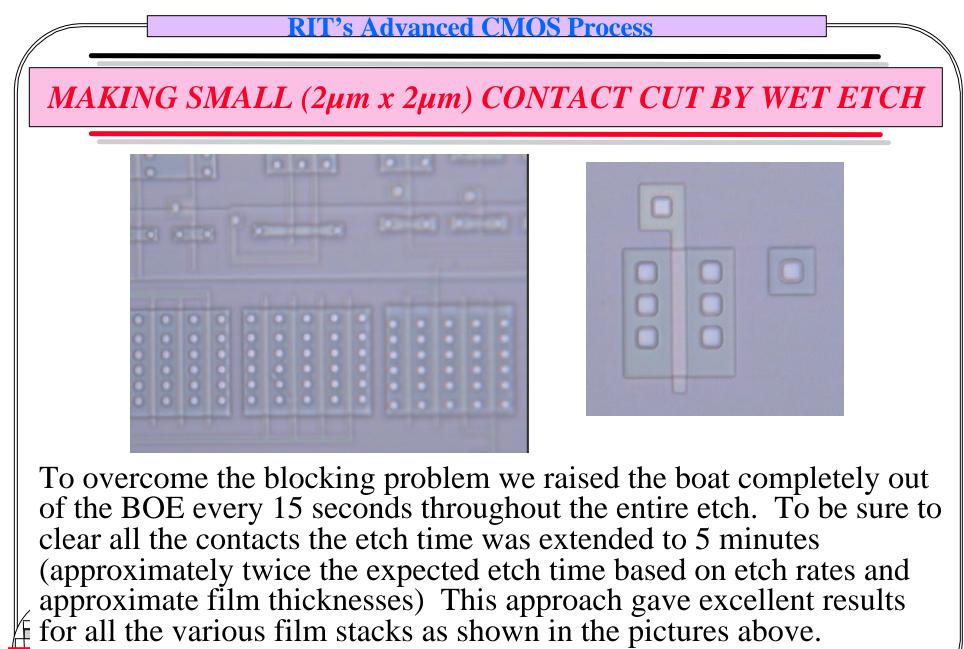

Contact cut etch is also difficult. Plasma etch is difficult because of the different oxide layers and thickness and the poor selectivity between etching oxide and the underlying poly or drain/source silicon. Wet etch has problems with blocking. That is where the BOE can not get into the small contact cut openings. Blocking depends on surface tension as measured by the wetting angle which depends on the type of photoresist used.

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

MAKING SMALL (2µm x 2µm) CONTACT CUT BY WET ETCH

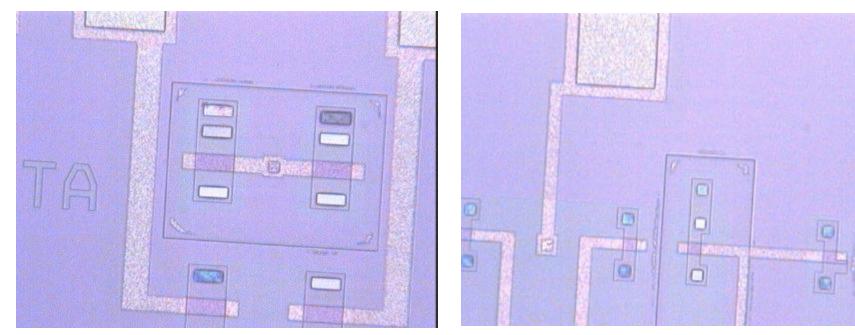

Wet etch has problems with blocking. That is where the BOE can not get into the small contact cut openings. Blocking depends on surface wetting angle. If blocking occurs some contact cuts will etch and <u>clear</u> while others will not etch as illustrated in the pictures above.

Rochester Institute of Technology Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

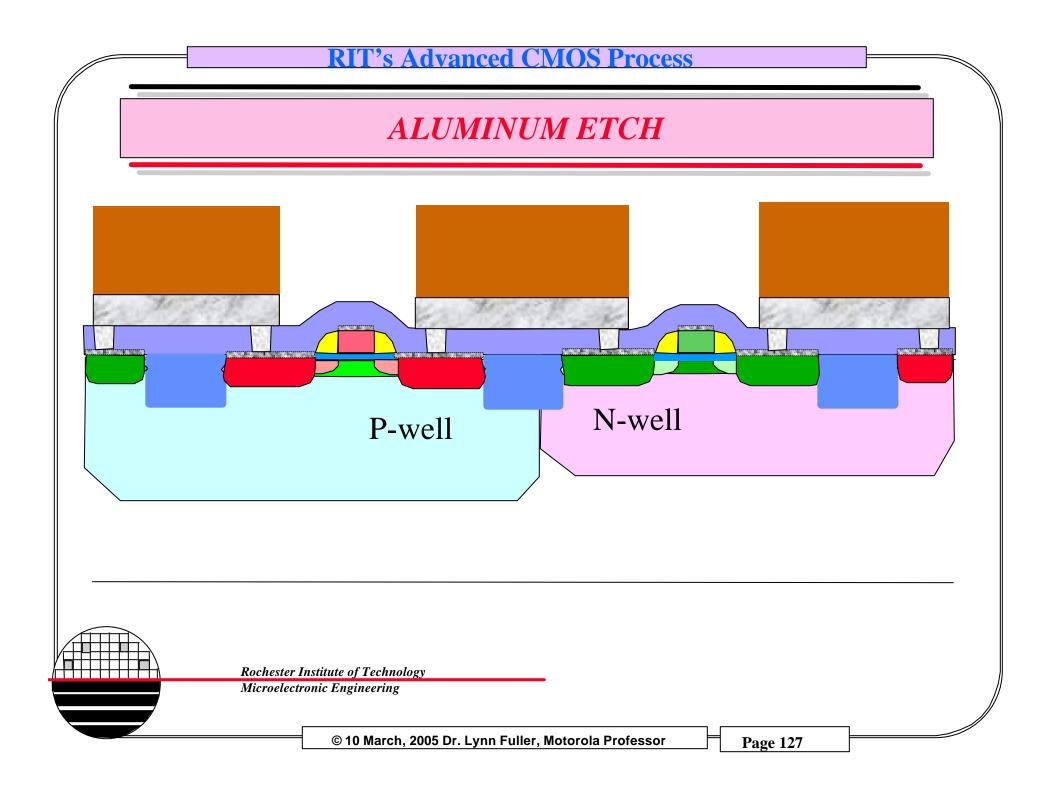

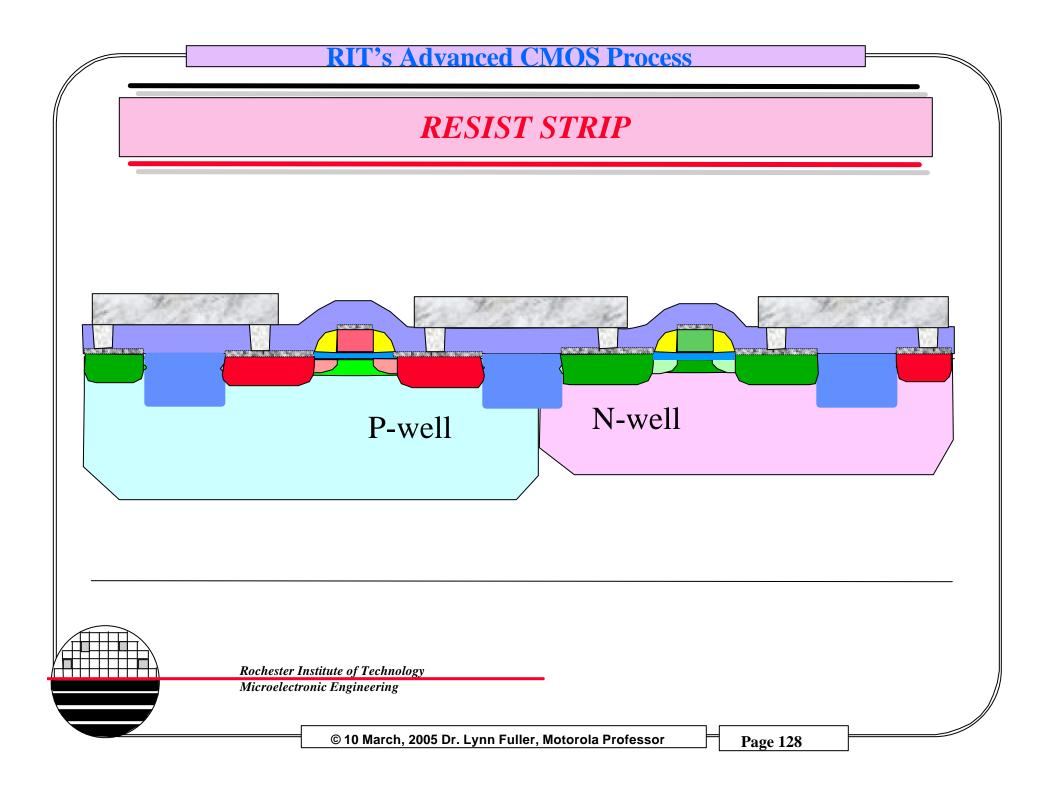

### **ALUMINUM ETCH**

### LAM 4600 Aluminum Etch Tool

| A COLUMN AND A COLUMN |       |      |          |       |      |

|------------------------------------------------------------------------------------------------------------------|-------|------|----------|-------|------|

| Step                                                                                                             | 1     | 2    | 3        | 4     | 5    |

| Pressure (mtorr)                                                                                                 | 300   | 300  | 300      | 300   | 0    |

| RF Top (W)                                                                                                       | 0     | 0    | 0        | 0     | 0    |

| RF Bottom (W)                                                                                                    | 0     | 250  | 125      | 125   | 0    |

| Gap (cm)                                                                                                         | 3     | 3    | 3        | 3     | 5.3  |

| N2                                                                                                               | 25    | 25   | 40       | 50    | 50   |

| BCI3                                                                                                             | 100   | 100  | 50       | 50    | 0    |

| CI2                                                                                                              | 10    | 10   | 60       | 45    | 0    |

| Ar                                                                                                               | 0     | 0    | 0        | 0     | 0    |

| CFORM                                                                                                            | 15    | 15   | 15       | 15    | 15   |

| Complete                                                                                                         | Stabl | Time | endpoint | Oetch | time |

| time (s)                                                                                                         | 15    | 8    | 120      | 25%   | 15   |

Rochester Institute of Technology

Microelectronic Engineering

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

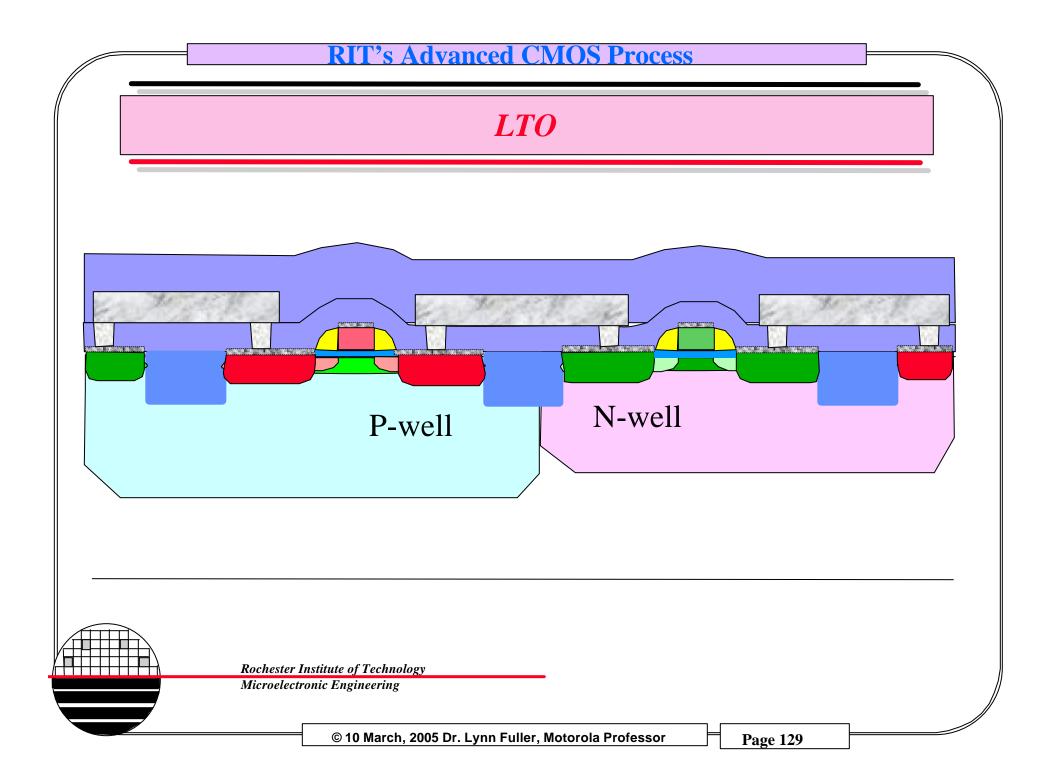

### **PECVD OXIDE FROM TEOS**

**TEOS Program:** (Chamber A) Step 1 Setup Time = 15 secPressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RFPower = 0 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 2 – Deposition  $\hat{\text{Dep Time}} = 55 \text{ sec } (5000 \text{ Å})$ Pressure = 9 TorrSusceptor Temperature= 390 C Susceptor Spacing= 220 mils RF Power = 205 watts TEOS Flow = 400 sccO2 Flow = 285 scc Step 3 – Clean Time = 10 secPressure = Fully Open Susceptor Temperature= 390 C Susceptor Spacing= 999 mils RF Power = 50 watts TEOS Flow = 0 sccO2 Flow = 285 scc

### TAKE SEM PICTURES OF RING OSCILLATOR

# MESA WIPTRACKING SYSTEM

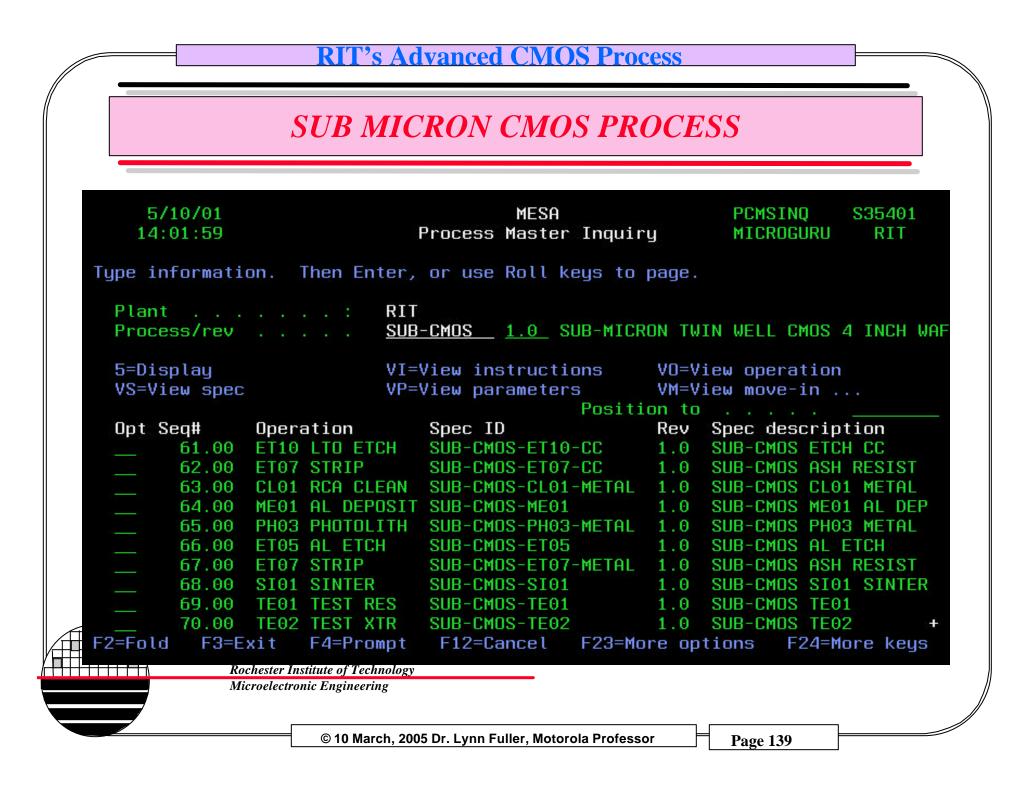

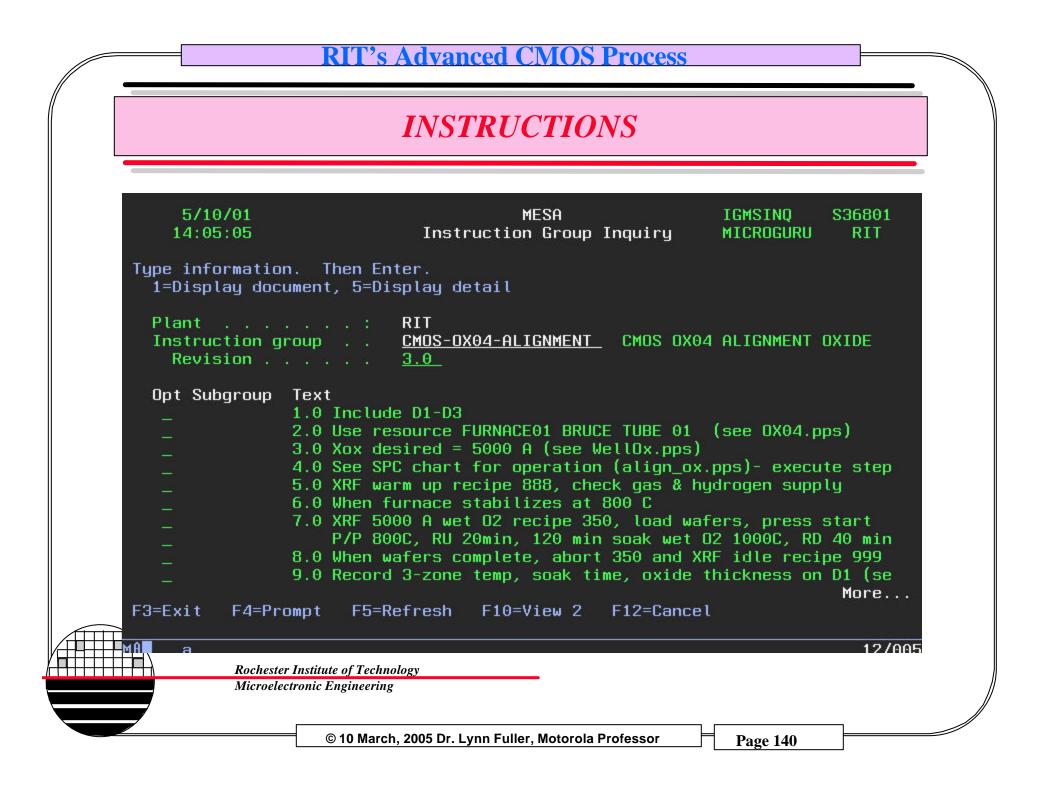

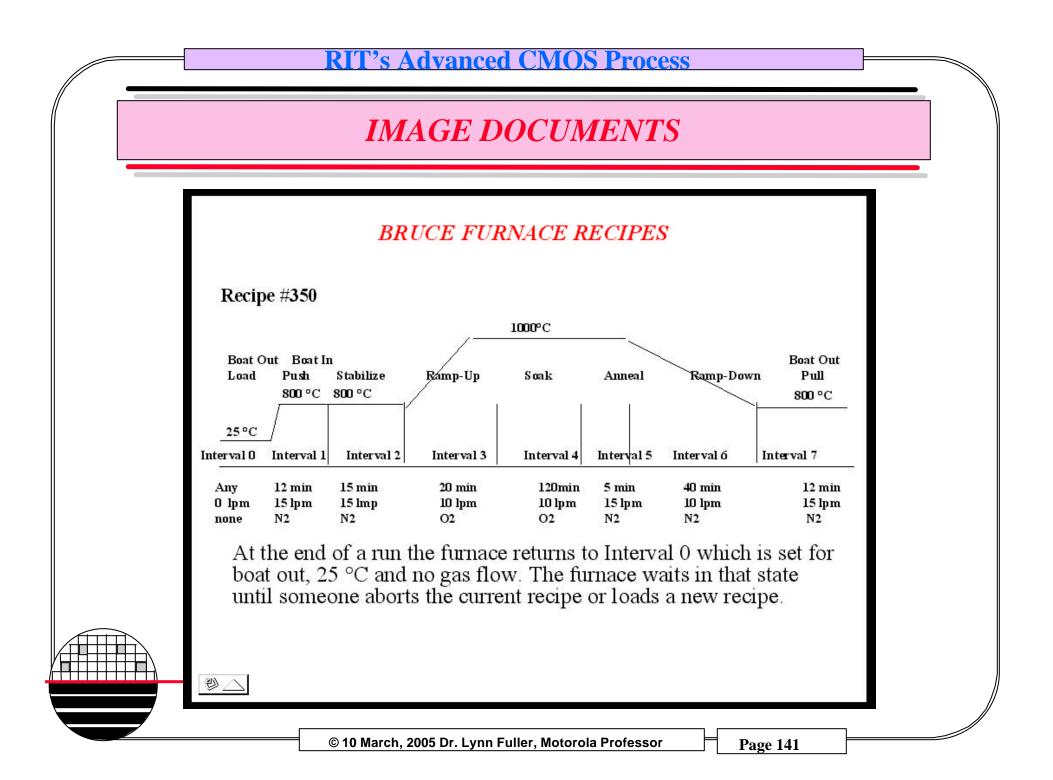

The process is long and complicated and will take many months to complete each lot. A computerized record keeping system is required to provide instructions and collect data. MESA (Manufacturing Execution System Application) from Camstar, Inc. runs on our AS/400 computer.

© 10 March, 2005 Dr. Lynn Fuller, Motorola Professor

Rochester Institute of Technology Microelectronic Engineering