- Rodolfo Azevedo

- UNICAMP

# Instruction Set Architecture

The portion of the computer that is visible to the programmer or the compiler writer.

Computer Architecture: A quantitative approach

An instruction set architecture (ISA) is an abstract model of a computer. It is also referred to as architecture or computer architecture.

Wikipedia

Contrato entre os projetistas de hardware e software.

Definição de uma linha

# Que tipo de contrato é esse?

A empresa fornece a especificação precisa e você escreve o software!

# Isto é importante?

x86 ISA

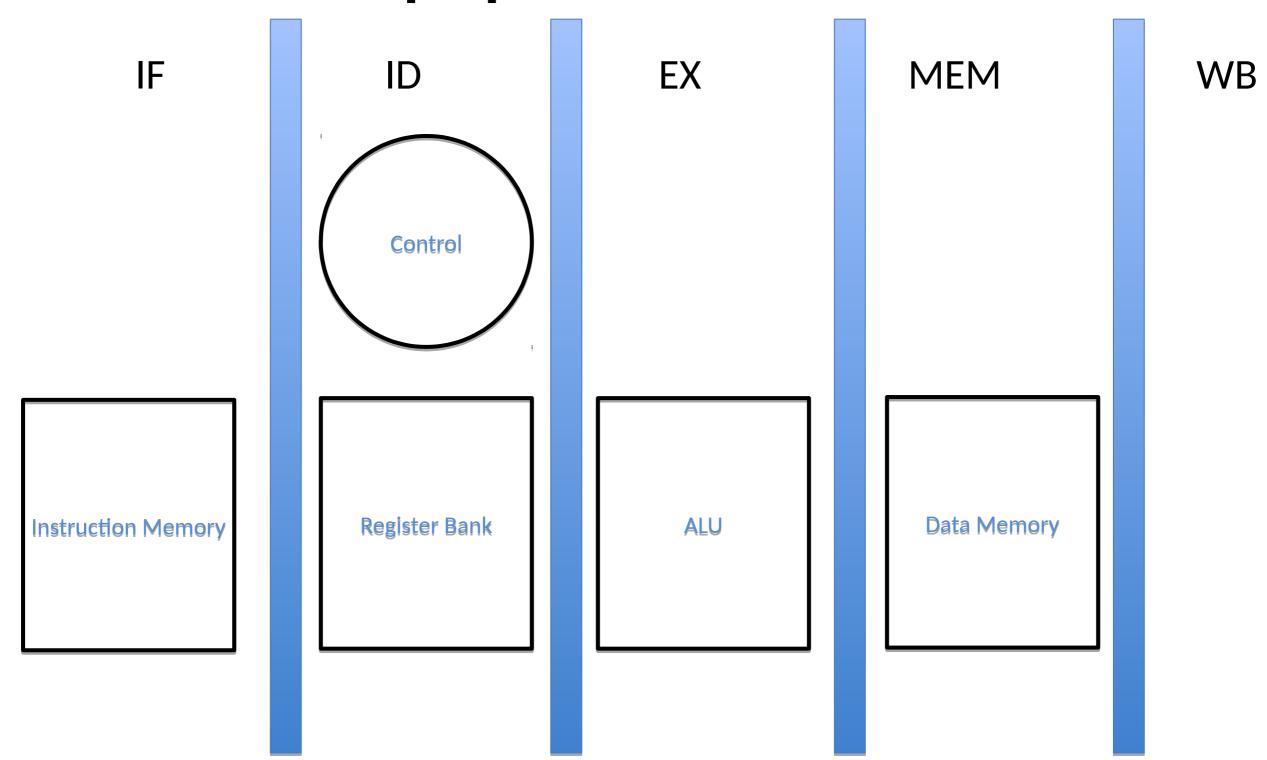

# Visão altíssimo nível de um pipeline escalar

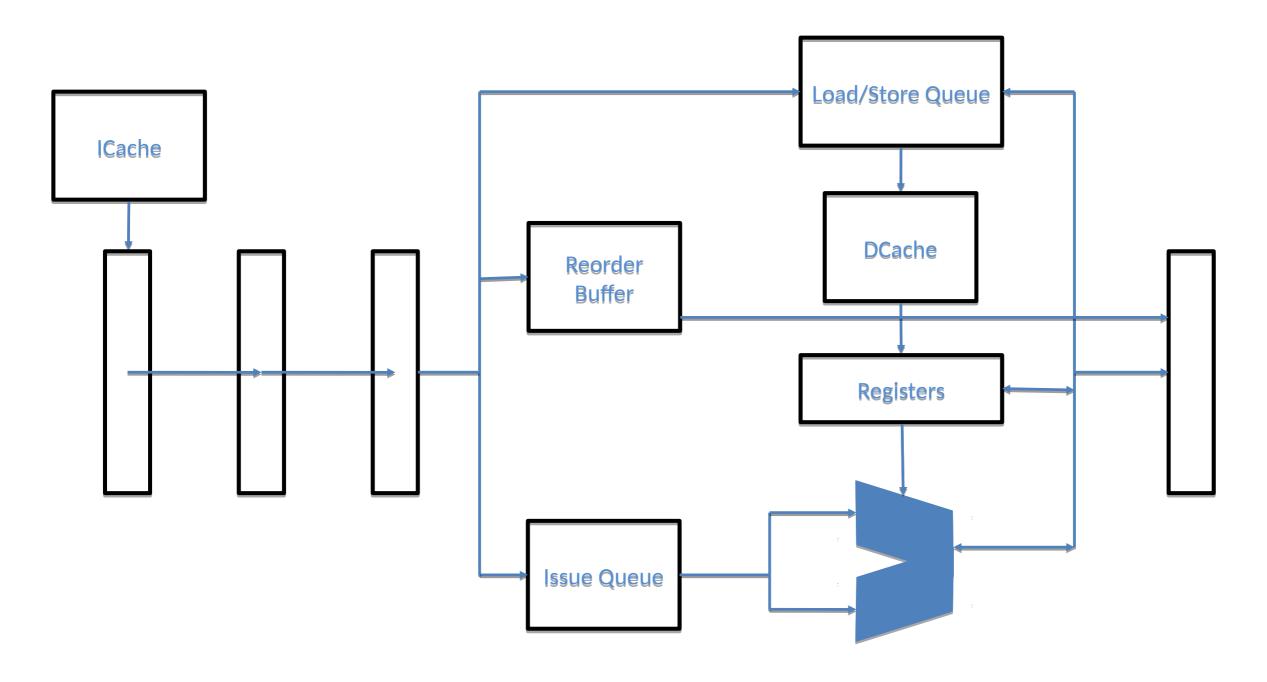

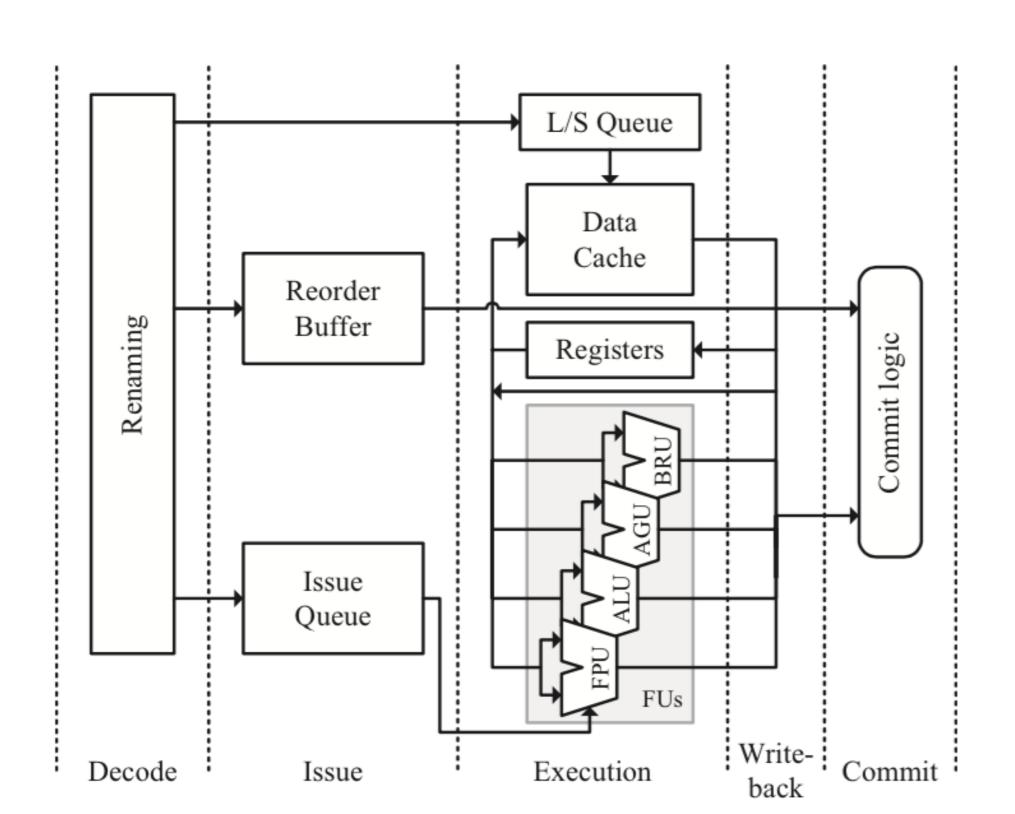

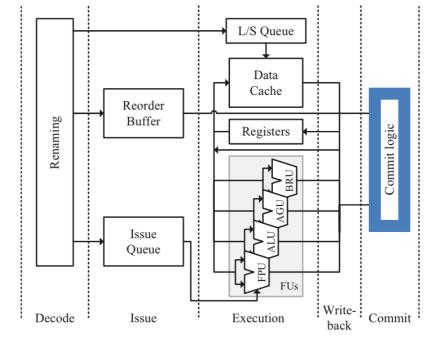

# Visão alto nível de um superescalar

Fetch Decode Rename Issue Execution Write-back Commit

# Temporização

# Contador de tempo do processador

- rdtsc: lê o time stamp clock

- Pode ser reordenada no código

- rdtsp: lê o time stamp clock e processor id

- Garante que todas as instruções que iniciaram antes terminarão antes

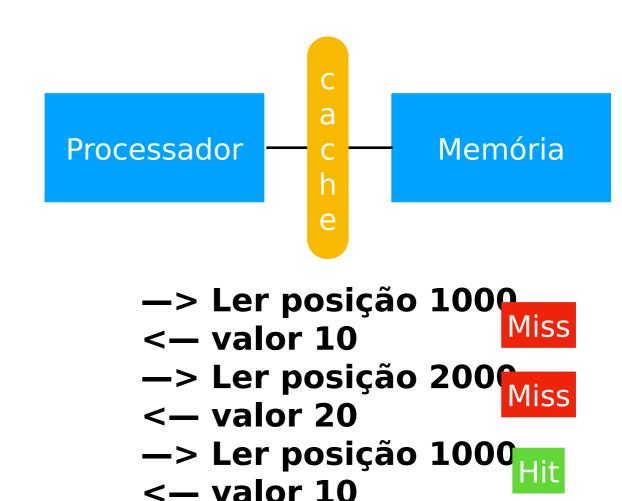

#### Caches

#### Caches

- DRAM são lentas

- A hierarquia de caches guarda cópia dos dados recentemente utilizados acelerando acessos posteriores

- Acesso transparente ao usuário

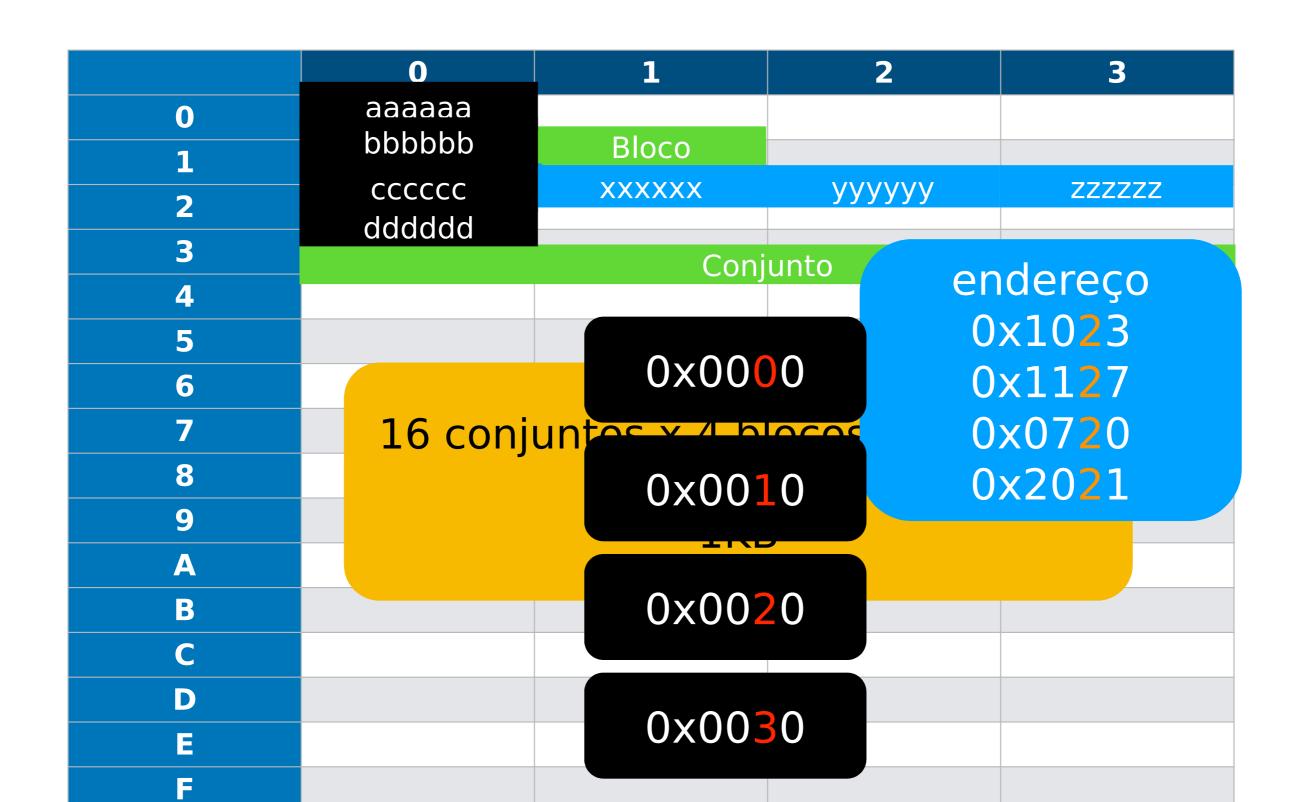

#### Por dentro da cache

## Exemplo

- 7 voluntários

- 4 células da cache

- 1 controlador

- 1 cronômetro

- 1 memória

- Lembrete sobre o endereço da cache: 0x00N0

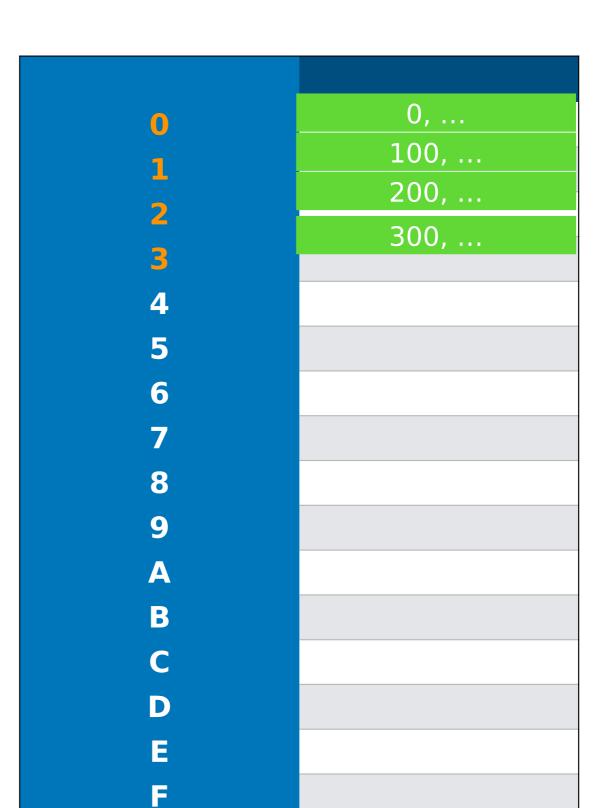

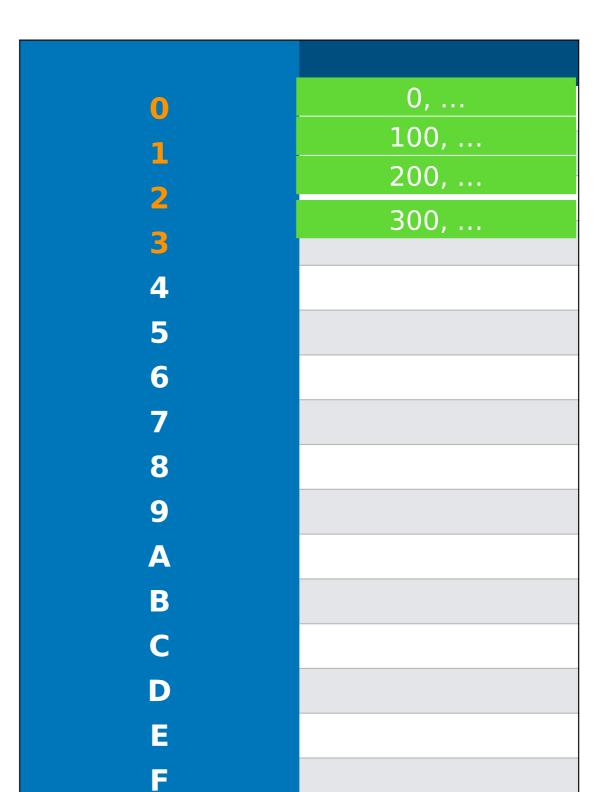

#### Treinamento

- 0x1000

- 0x0000

- 0x0010

- 0x0020

- 0x0030

- 0x0000

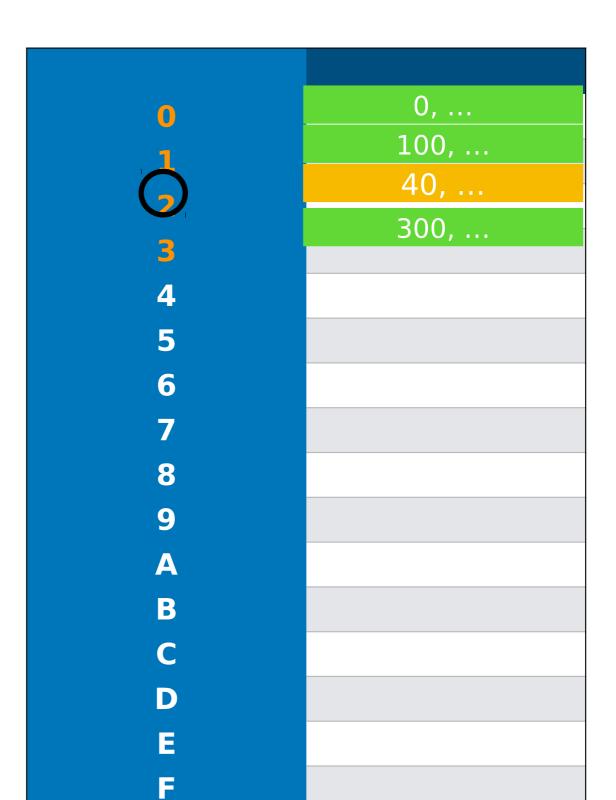

#### Uma leitura nova

• ??????

# Vamos descobrir algo sobre a leitura

- 0x0000

- 0x0010

- 0x0020

- 0x0030

# Conclusões

Pode-se converter dados em endereços e testar várias posições de memória

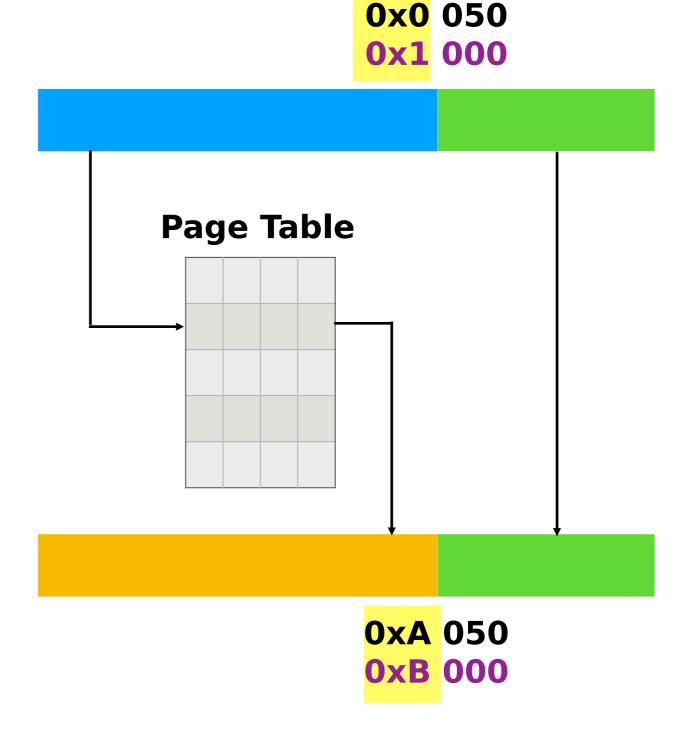

## Memória Virtual

#### Memória Virtual

- Converte endereços virtuais em físicos (reais)

- Implementa mecanismos de proteção de memória

- Page Table

- Hierárquica

- Bits de proteção

- TLB

- Acesso rápido aos dados da Page Table

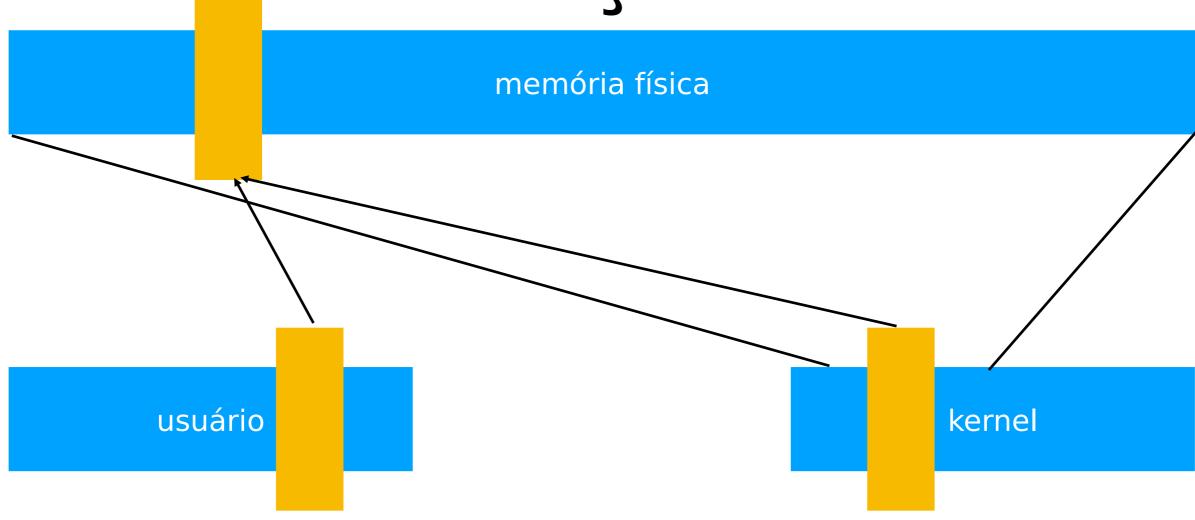

## Espaço de Endereçamento

inux e MacOS: todo o espaço de endereçamento é mapeado no kernel Vindows trabalha com pools de memória

# Exemplo bem simples

- Endereços começados com 0: usuário

- Endereços começados com outros dígitos: supervisor

- Voluntário?

- 0x0000

- 0x1000

- 0x2000

#### KASLR

- Kernel Address Space Layout Randomization

- Endereços onde o kernel é carregado são aleatorizados toda vez que o sistema inicia

- Melhora a segurança contra ataques, mas ainda é possível descobrir onde o kernel está carregado

- Utiliza blocos de 8GB para carga

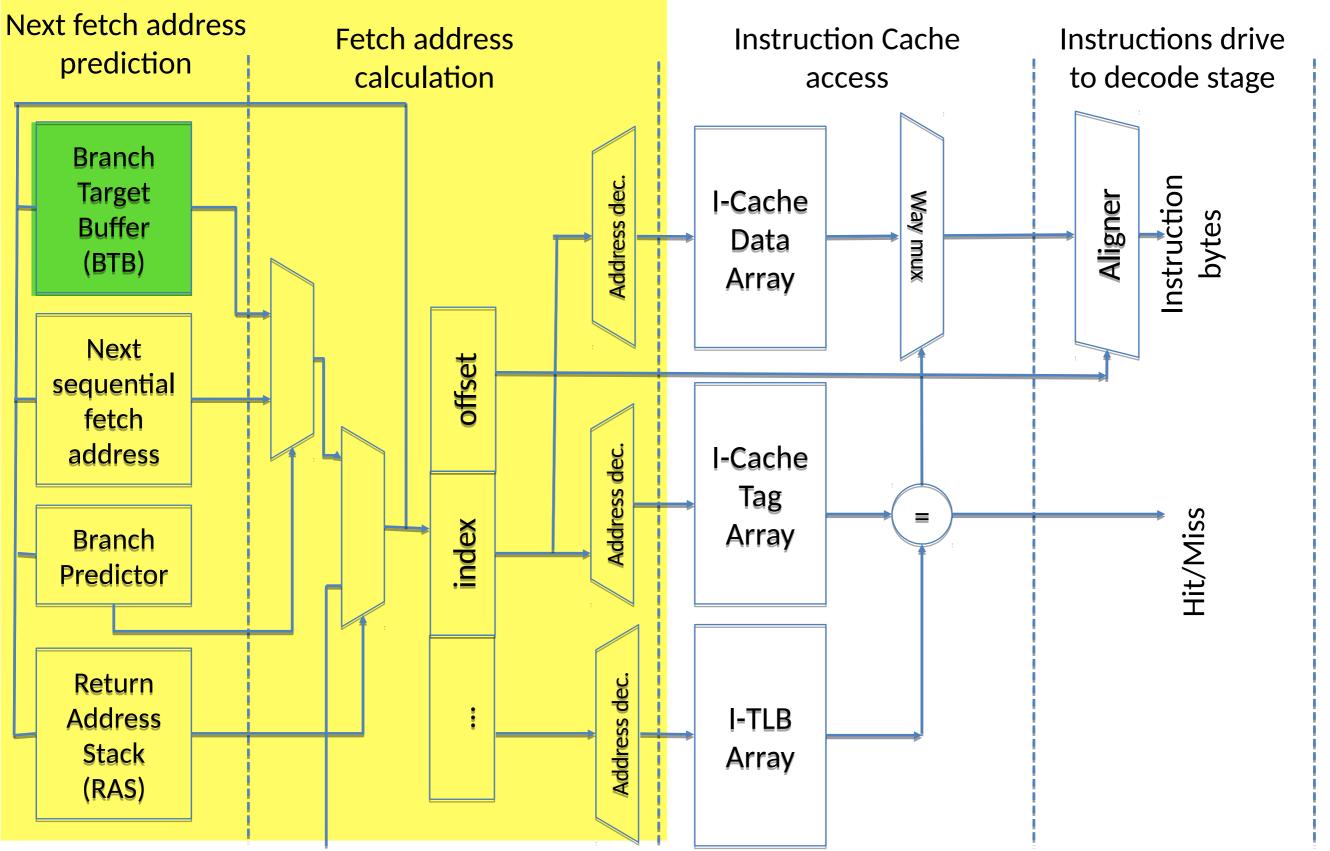

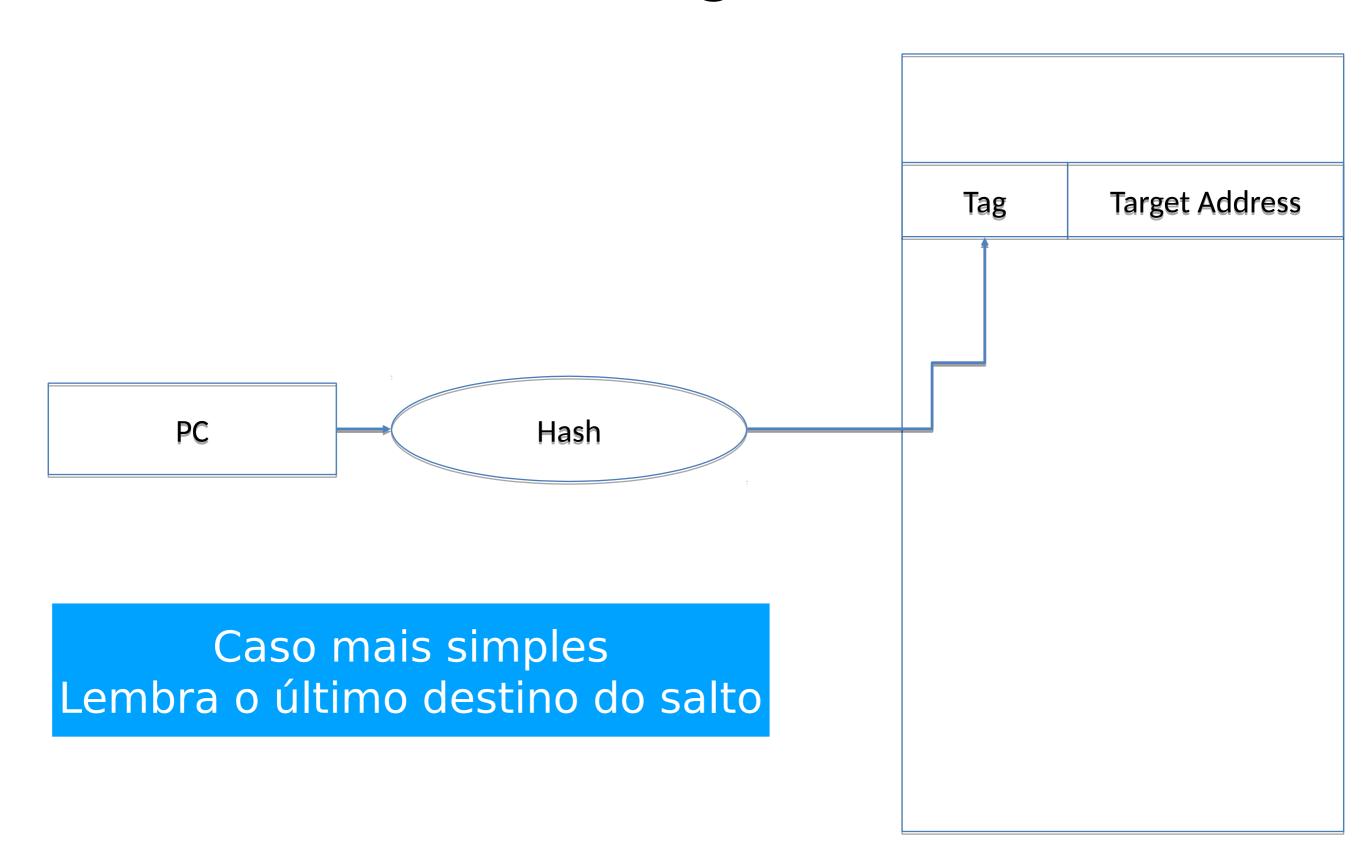

#### Branch Prediction

Fetch Pipeline

#### Branch Target Buffer

# Execução fora de ordem

# Execução

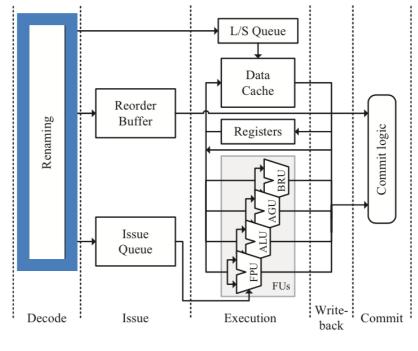

## Renaming

- Utiliza mais registradores internos que a quantidade disponível na ISA

- Remove dependências de nome

Data dependence Read after write Name dependence Write after write

Name dependence Write after read

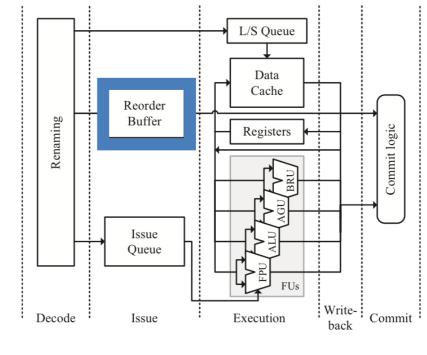

#### Reorder buffer

- Guarda as instruções na ordem de execução do código

- Guarda bits extras sobre o estado da execução das instruções

- Exception bit

- A instrução será efetivada no estágio de commit

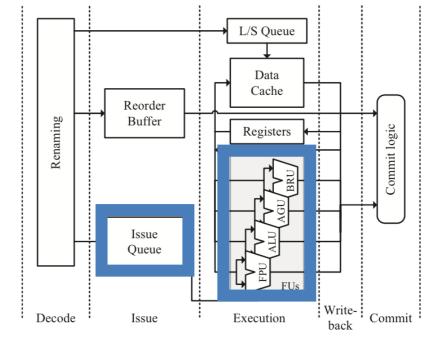

#### Issue Queue

- Envia instruções para as unidades funcionais

- As instruções podem ser executadas fora de ordem

- Desde que não haja dependência não resolvida ainda

#### Commit

- Efetiva as instruções em ordem

- Gera as exceções

# Será que funciona?

#### Atores

- Voluntários da cache

- Estágio de fetch

- 2 para execute

- 1 para gerenciamento de memória virtual

- 1 para commit

# Instruções em papel

## O que houve

- Memória Virtual

- Marca com \* quando não há permissão para executar

- Commit

- Para a execução quando recebe uma instrução com \*

- Cache

- Comportamento conhecido

#### Meltdown

- Instrução 1

- Leia posição de memória 0x2020

- Instrução 2

- Pegue o resultado da instrução anterior e acesse a memória

# Código

```

retry:

```

mov al, byte [rcx]

Leitura não permitida

shl rax, 0xc

prepara o endereço

jz retry

mov rbx, word [rbx + rax]

acessa a memória

## Requisitos extras

- Acesso a endereço inválido gera exceção

- Programas de usuário podem capturar esta exceção e não fazer nada

- Pode-se usar instruções de memória transacional para evitar as exceções. As transações serão abortadas

- Pode ser executado por Javascript, no seu browser, apontando para uma página maliciosa

## Spectre

```

if (x < array1_size) Falso mas previsto como

verdadeiro

y = array2[array1[x] * 256];</pre>

```

#### Comentários

- Totalmente no nível de usuário

- Processadores multithread compartilham estruturas de branch prediction

- É possível ler dados do seu browser via Javascript

- Poluir o branch predictor não é tão simples mas é possível

# Diferenças

Architecture

Intel, Apple

Intel, Apple, ARM, AMD

Entry

Must have code execution on the system Must have code execution on the system

Method

Intel Privilege Escalation + Speculative Execution Branch prediction + Speculative Execution

Impact

Read kernel memory from user space

Read contents of memory from other users' running programs

Action

Software patching

Software patching (more nuanced)

https://danielmiessler.com/blog/simple-explanation-difference-meltdown-

#### Patches

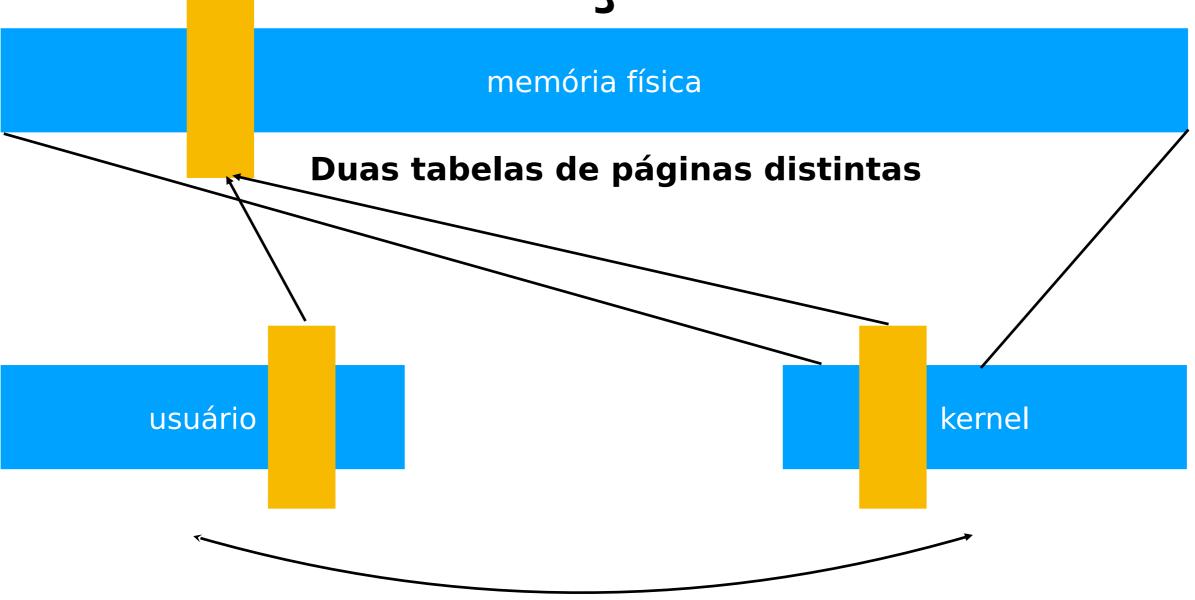

- Meltdown: Separar o espaço de endereçamento do kernel das aplicações

- KAISER Patch

- Mais TLB flushes durante a execução de programas

- Spectre: With microcode updates, Intel has enabled three new features in its processors to control how branch prediction is handled.

- IBRS ("indirect branch restricted speculation") protects the kernel from branch prediction entries created by user mode applications;

- STIBP ("single thread indirect branch predictors") prevents one hyperthread on a core from using branch prediction entries created by the other thread on the core;

- IBPB ("indirect branch prediction barrier") provides a way to reset the branch predictor and clear its state.

## Espaço de Endereçamento

**Limpar TLB**

# Meltdown in action memory dump

# Meltdown in action password

#### Conclusões

- Nova era de timing attacks em grande escala

- Repensar a especificação da arquitetura (ISA)

- Incluir alguns requisitos de temporização?

- Especulação?

- Maior separação dos estados internos dos processos

#### Referências

- http://meltdownattack.com

- Meltdown: <u>https://meltdownattack.com/meltdown.pdf</u>

- Spectre: <a href="https://spectreattack.com/spectre.pdf">https://spectreattack.com/spectre.pdf</a>

- Exemplos no github: <u>https://github.com/IAIK/meltdown</u>

- On the Meltdown and Spectre Design Flaws. Mark Hill.

- http://research.cs.wisc.edu/multifacet/papers/hill\_mark\_wisconsin\_meltdown\_spectre.pdf

- Rodolfo Azevedo

- UNICAMP