# SEL-415 Introdução à Organização dos Computadores

Decodificadores

Aula 2

Prof. Dr. Marcelo Andrade da Costa Vieira Profa. Luiza Maria Romeiro Codá Profa. Maria Stela Veludo de Paiva

## INTRODUÇÃO (Resumo):

#### Estudo ou análise de um Computador:

ORGANIZAÇÃO: (implementação) : relacionada aos componentes físicos

Exs: tecnologia utilizada na memória, freqüência do relógio, sinais de controle.

ARQUITETURA: características de interesse do programador

Exs: Conjunto de instruções, tamanho da palavra, modo de endereçamento das instruções

## INTRODUÇÃO(cont):

HARDWARE: parte física do computador → conjunto de componentes eletrônicos que constituem um computador

Exs: circuito integrado, monitor, teclado, mouse.

O hardware sózinho não faz nada ⇒ é inerte.

É necessário uma instrução ou comando para realizar uma certa tarefa.

SOFTWARE: parte lógica do computador → conjunto de instruções de diferentes formas e dados processados pelos circuitos eletrônicos do hardware.

Ex: programa do computador.

## INTRODUÇÃO (cont):

Resumindo: o computador é constituído de diversos componentes (hardware), capaz de realizar uma série de tarefas, de acordo com a seqüência de ordens dadas aos componentes, sendo essas ordens( ou instruções) em conjunto denominadas programa (software)..

Como o Computador representa os dados a serem processados e as instruções?

são representados por valores numéricos(dígitos) os quais são convertidos em valores de tensão ⇒ por isso o nome computador digital

Qual o sistema de numeração utilizado pelos Computadores?

sistema decimal é inconveniente para processamento computacional ⇒utilizase o sistema binário (0 e 1) (menor consumo de energia) Portanto, Hardware básico utiliza chaves, relés, válvulas, transistores que funcionam abertos ou fechados.

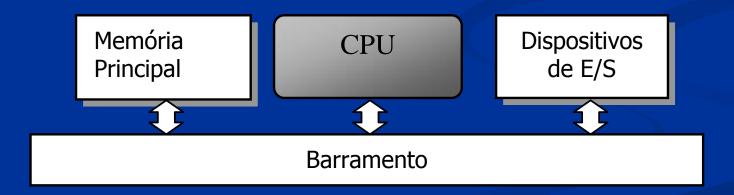

#### MODELO DE VON NEUMANN

A arquitetura básica de um computador consiste de 4 partes principais:

- CPU (ULA + Controle + Registradores)

- Memória principal

- dispositivo de conexão (barramento de dados)

- dispositivo de entrada/saída.

# Os Princípiois de Von Neumann (Revisão aula 1)

#### O Conceito Von Neumann:

- computador visto como uma Máquina de programa armazenado

- seqüencialmente executado

- CPU comunica-se com apenas um dispositivo de cada vez

## Implementação do Modelo de Von Neumann

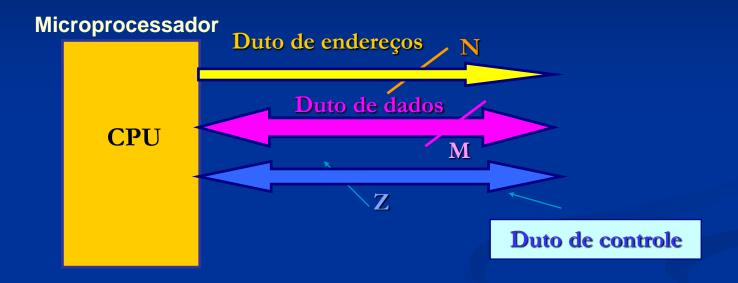

- ✓ Apenas 1 duto (barramento) faz a comunicação entre CPU e memórias ou dispositivos de I/O

- Esse duto consiste em :

- um conjunto de linhas de endereços (geradas pela CPU) um conjunto Linhas de dados (enviadas ou recebidas pela CPU) um conjunto de linhas de controle (geralmente gerados pela CPU)

- A CPU (ou microprocessador) deve selecionar apenas 1 dispositivo (memórias ou I/O) de cada vez para se comunicar

Portanto, necessário que o circuito de hardware implementado para o Sistema microprocessado possibilite que a CPU selecione apenas 1 dispositivo por vez.

Para tal utiliza-se DECODIFICADORES

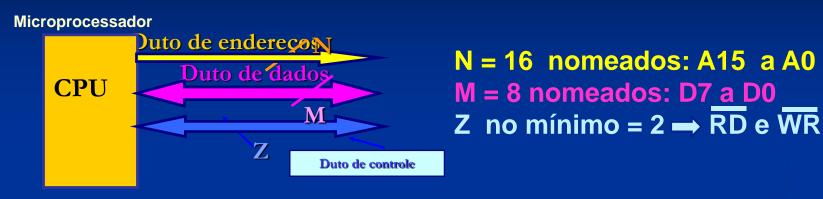

### Representação da CPU e barrramentos

Onde N, M e Z são o número de linhas d e endereços, dados e sinais de controle que podem variar de acordo com a escolha do microprocessador

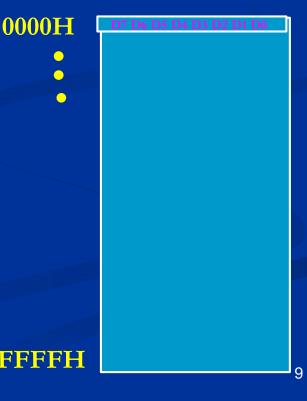

### Microprocessador (CPU) de 64K x 8

N = 16 nomeados: A15 a A0

M = 8 nomeados: D7 a D0

Z no mínimo = 2 → RD e WR

Um microprocessador de 16 linhas de endereços (A15 a A0) consegue gerar 2 <sup>16</sup> endereços diferentes = 65536 endereços Que pode ser representado por 64K (onde K = 1024)

Cada endereço endereça o conjunto de 8 bits de dados (D7 a D0)

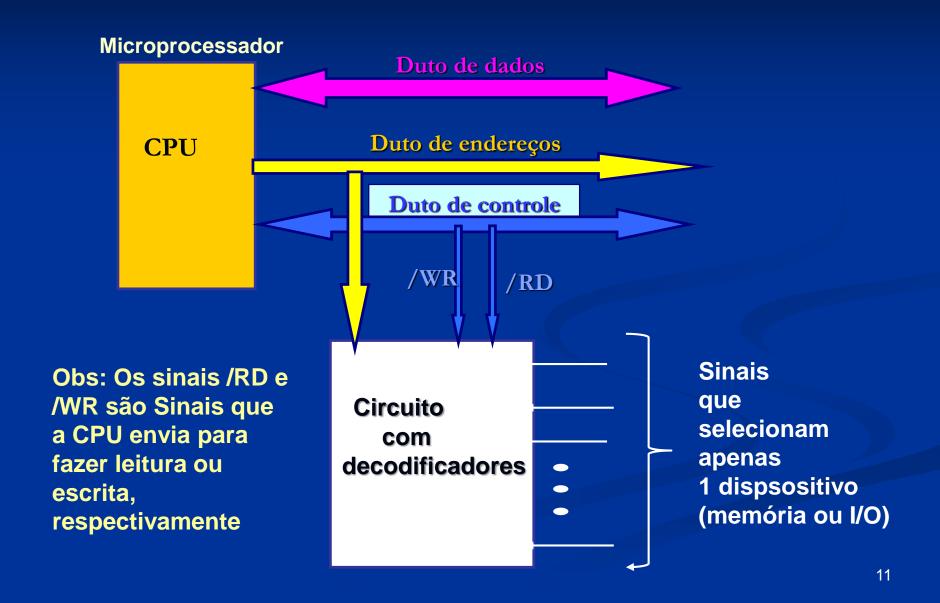

# Comunicação doMicroprocessador (CPU) de 64K x 8 com os dispositivos

O microprocessador envia um número de endereço na linha de endereços (A15 a A0) para selecionar o dispositivo com o qual irá se comunicar (enviando ou recebendo dados)

O microprocessador para enviar dados para memórias ou dispositivos entrada ESCRITA

coloca o sinal de controle WR ='0'

O microprocessador para receber dados de memórias ou dispositivos saída LEITURA

coloca o sinal de controle RD ='0'

### Implementação do Modelo de Von Neumann

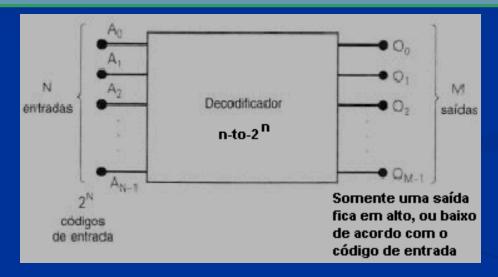

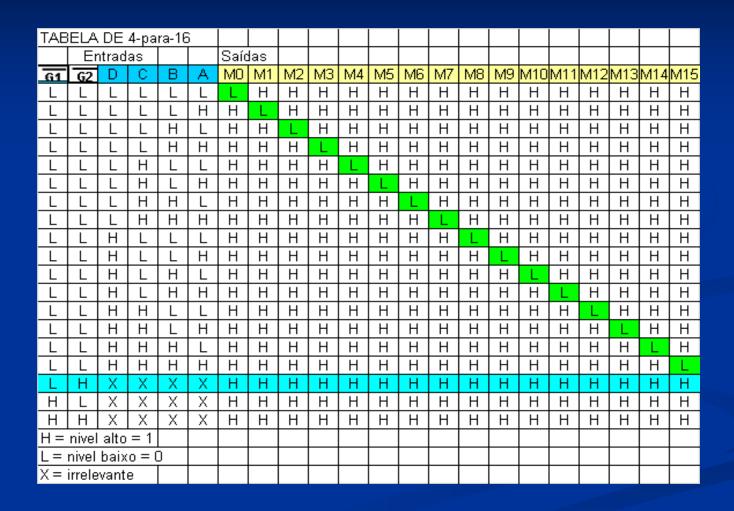

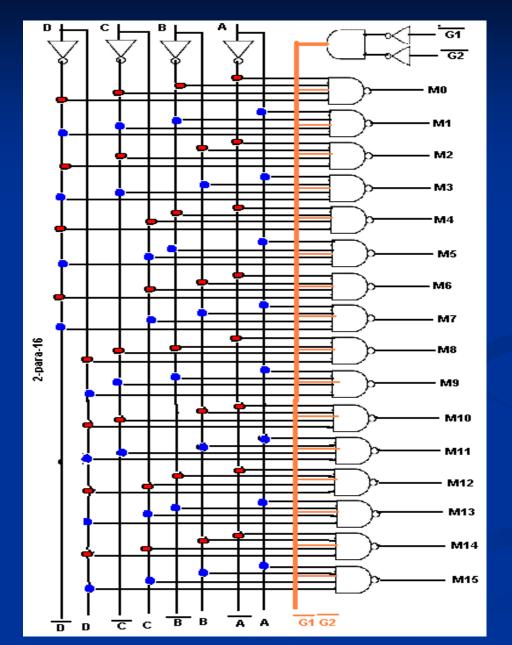

#### **DECODIFICADORES** (Revisão)

#### Decodificador N X M:

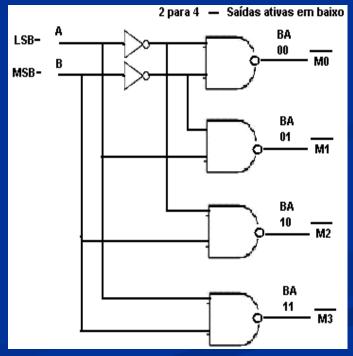

converte um código binário de **N** bits que lhe é apresentado como entrada, em **M** linhas de saída, sendo que cada linha de saída será ativada por uma, e somente uma, das possíveis combinações dos bits de entrada. ( $M = 2^N$ )

Existem decodificadores que quando a saída está ativa o valor dela é "1" e outros que apresentam a saída ativa em "0". Nos circuitos de seleção de projetos de microcomputadores utiliza-se decodificadores com saídas ativas em "0" porque nas memórias e grande parte das interfaces, o sinal de seleção é ativo em "0".

#### **DECODIFICADORES**

- Cada saída é ativada por um único código binário aplicado nas entradas;

- o índice da saída indica o valor do código binário que ativa essa saída.

| TABELA 2-para-4 |   |        |    |    |    |

|-----------------|---|--------|----|----|----|

| Entradas        |   | Saídas |    |    |    |

| В               | Α | Q0     | Q1 | Q2 | Q3 |

| 0               | 0 | 0      | 1  | 1  | 1  |

| 0               | 1 | 1      | 0  | 1  | 1  |

| 1               | 0 | 1      | 1  | 0  | 1  |

| 1               | 1 | 1      | 1  | 1  | 0  |

Decodificador 2 para 4

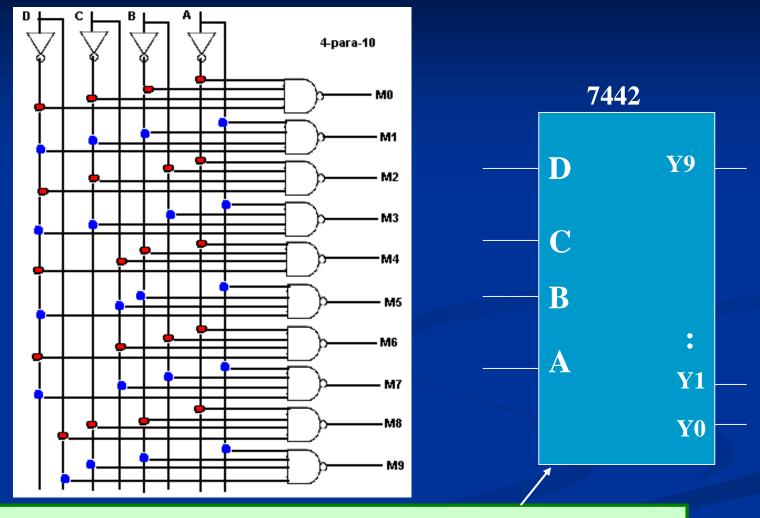

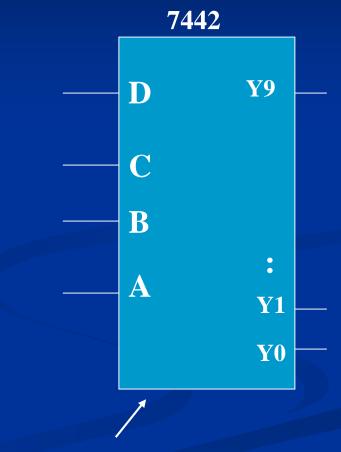

# 7442 : DECODIFICADOR 4 para 10 com saidas ativas em nível baixo

#### Tabela para o 7442

| TABELA    | 4-para | a-10 |   |   |        |    |    |    |    |    |    |    |    |    |

|-----------|--------|------|---|---|--------|----|----|----|----|----|----|----|----|----|

|           | Entrad | las  |   |   | Saídas |    |    |    |    |    |    |    |    |    |

| Num       | О      | 0    | В | Α | M0     | M1 | M2 | M3 | M4 | M5 | M6 | M7 | M8 | M9 |

| 0         | L      | L    | L | L | L      | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 1         | L      | L    | L | Н | Н      | L  | Н  | Η  | I  | Н  | I  | Н  | Η  | Н  |

| 2         | L      | L    | Н | L | Н      | Н  | L  | Н  | Н  | Н  | Н  | Н  | Н  | Н  |

| 3         | L      | L    | Н | Н | Н      | Н  | Н  | L  | Н  | Н  | Н  | Н  | Н  | Н  |

| 4         | L      | Н    | L | L | Н      | Н  | Н  | Н  | L  | Н  | Н  | Н  | Н  | Н  |

| 5         | L      | Н    | L | Н | Н      | Н  | Н  | Н  | Н  | L  | Н  | Н  | Н  | Н  |

| 6         | L      | Н    | Н | L | Н      | Н  | Н  | Η  | Н  | Н  | L  | Н  | Н  | Н  |

| 7         | П      | I    | Ι | Н | H      | Ι  | I  | Ι  | I  | Ι  | I  | L  | Ι  | Н  |

| 8         | I      | L    | Ш | L | H      | Ι  | I  | Ι  | I  | Ι  | I  | Η  | L  | Н  |

| 9         | I      | L    | Ш | Н | H      | Ι  | I  | Ι  | I  | Ι  | I  | Ι  | Ι  | L  |

| 1         | Ι      | L    | Ι | L | Н      | Ι  | Ι  | Ι  | Ι  | Ι  | Ι  | Ι  | Ι  | Η  |

| N         | I      | L    | Ι | Н | Н      | Ι  | Ι  | Ι  | I  | Ι  | Ι  | Ι  | Ι  | Н  |

| V         | I      | H    | П | L | H      | I  | I  | Ι  | I  | Η  | I  | Η  | I  | Н  |

| Α         | I      | H    | П | Н | H      | I  | I  | Ι  | I  | Ι  | I  | Η  | I  | Н  |

| L         | Η      | Н    | Н | L | Н      | Η  | Η  | Ι  | Н  | Н  | Ι  | Н  | Η  | Н  |

| l.        | Η      | Н    | Н | Н | Н      | Η  | Ι  | Ι  | Н  | Н  | Ι  | Η  | Η  | Н  |

| H = nive  | alto = | 1    |   |   |        |    |    |    |    |    |    |    |    |    |

| L = nivel | baixo  | = 0  |   |   |        |    |    |    |    |    |    |    |    |    |

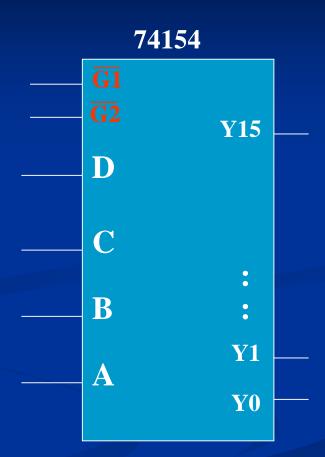

Obs: A entrada D do decodificador representa o bit mais significativo.

Entradas: **D C B A** (**D** é o bit + significativo)

Saídas: Y0 a Y9 (dez saídas) (ou M0 a M9)

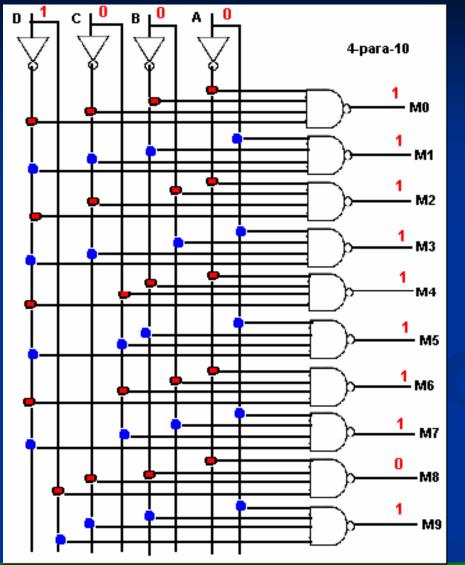

Entradas: D='1' C='0' B='0' A='0' (D é o bit + significativo)  $\rightarrow$  Entrada = (1000)b=8

Saídas: Y0 a Y9 ( dez saídas) (ou M0 a M9)  $\longrightarrow$  Y8 (M8)='0' é selecionada as demais são ='1'

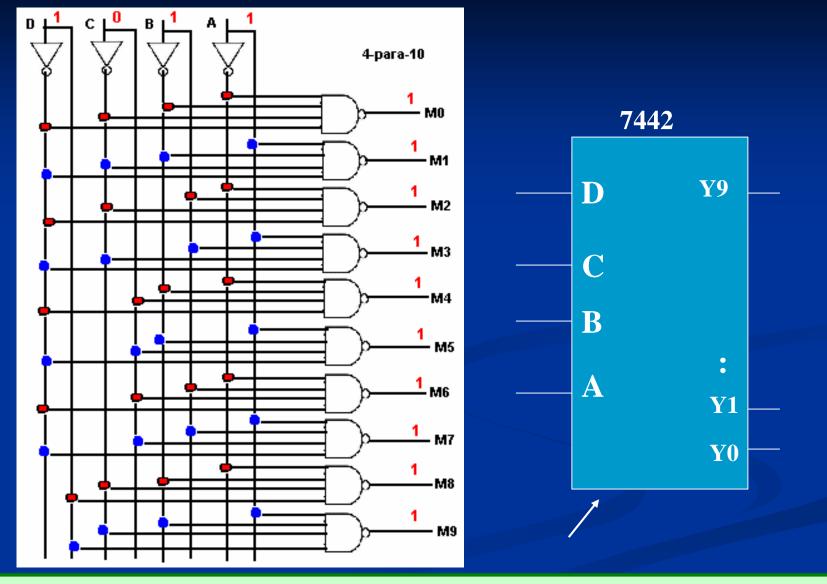

Entradas:  $\mathbf{D} \times \mathbf{C} \times \mathbf{B} = (1011)\mathbf{b} = 11$  em decimal

Saídas: Y0 a Y9 (dez saídas) (ou M0 a M9) nenhuma saída é selecionada, todas serão = 1'

G1 e G2: entradas para habilitar ou desabilitar o chip

D é o bit + significativo das entradas D C B A

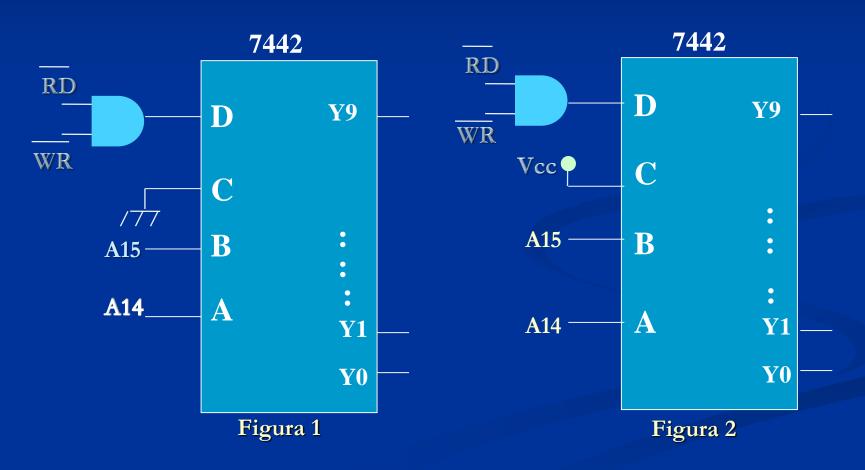

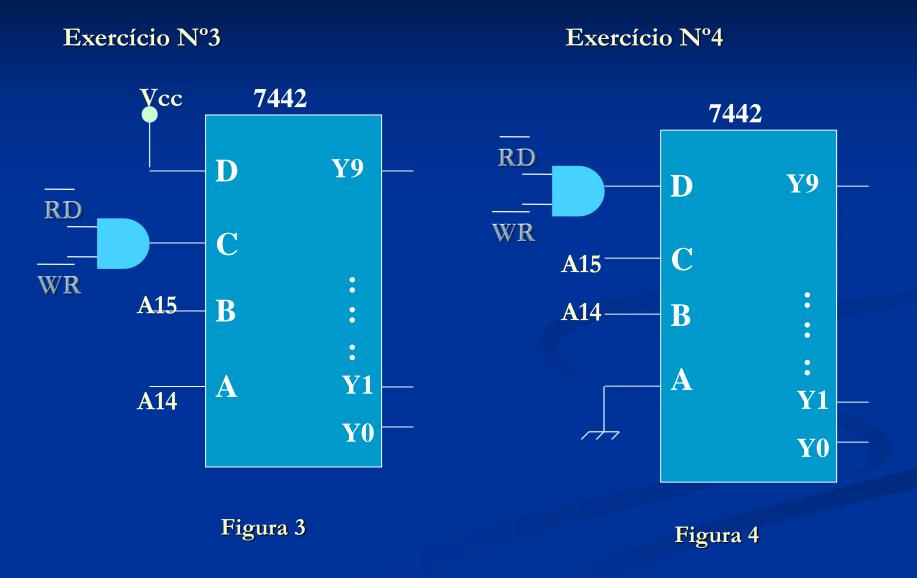

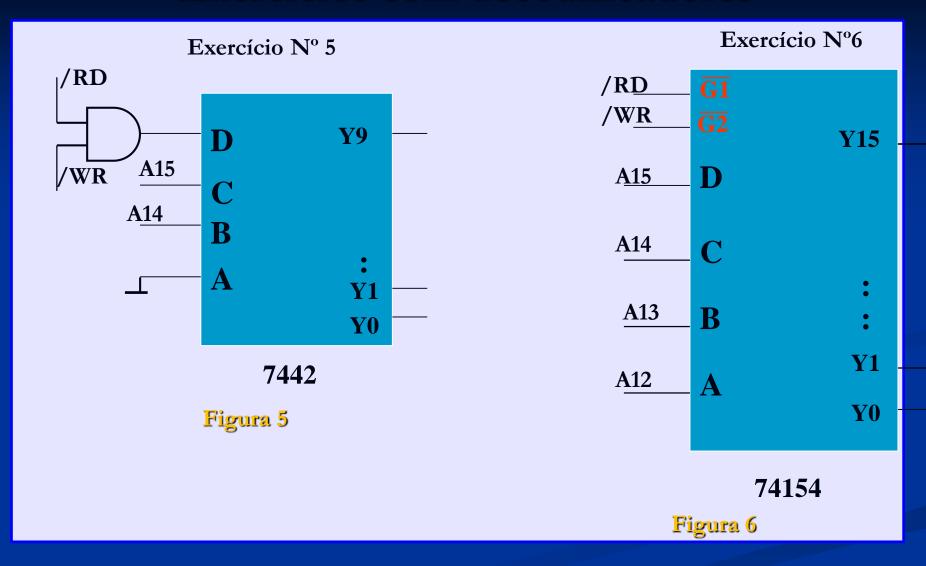

#### EXERCÍCIOS COM DECODIFICADORES:

Quais são saídas do 7442 podem ser usadas como sinal de seleção /CS, sabendo-se que as linhas de endereço devem estar sincronizadas com os sinais /WR e /RD?

# Associando faixas de endereço às saídas do decodificador

#### Para o decodificador do Exercício Nº1(Figura1):

| Valor dos | bits de seleção (A15 e A14)  A15A0,                                                                       |

|-----------|-----------------------------------------------------------------------------------------------------------|

| Saída Y0  | endereço inicial: 0000H — <b>00</b> 00 0000 0000 0000 endereço final: 3FFFH — <b>00</b> 11 1111 1111      |

| Saída Y1  | endereço inicial: 4000H <b>01</b> 00 0000 0000 0000 endereço final: 7FFFH: <b>01</b> 11 1111 1111 1111    |

| Saída Y2  | endereço inicial: 8000H → <b>10</b> 00 0000 0000 0000 endereço final: BFFFH → <b>10</b> 11 1111 1111 1111 |

| Saída Y3  | endereço inicial: C000H → <b>11</b> 00 0000 0000 0000 endereço final: DFFFH → <b>11</b> 11 1111 1111      |

#### **EXERCÍCIOS COM DECODIFICADORES:**

#### Exercícios com decodificadores

#### **EXERCÍCIOS COM DECODIFICADORES:**

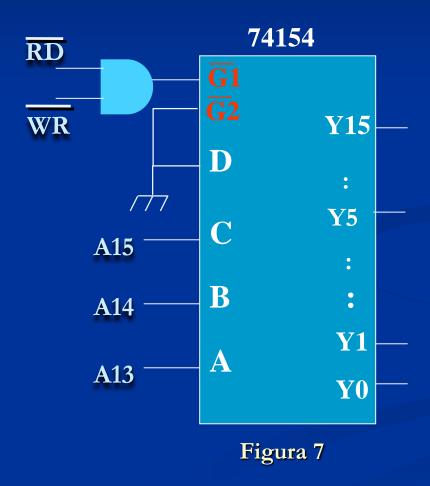

Exercício Nº7: a. Qual o valor de A15, A14 e A13 para a saída Y5 b. Qual a saída do decodificador que contém o endereço DFFFH

#### Exercícios com decodificadores

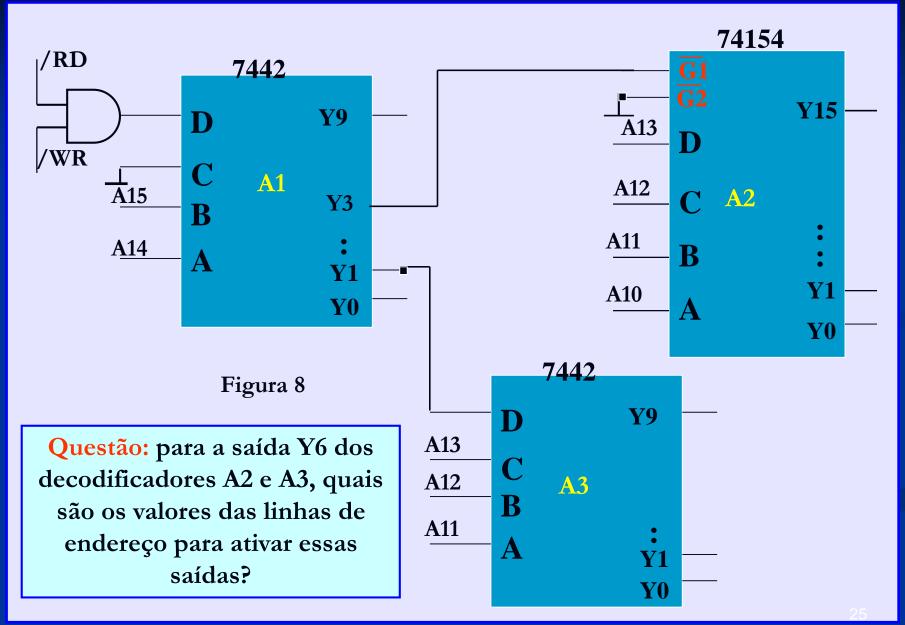

#### Exercício Nº8

# Associando faixas de endereço às saídas do decodificador

Decodificador A2 está na faixa de endereço da saída Y3 (C000 – FFFFH) e o A3 na faixa de endereço da saída Y1

#### Exemplo para 4 saídas do decodificador A2 da Figura 8:

| Valor dos | bits de seleção (A15 e A14)                       | A15A0,                                |  |  |  |

|-----------|---------------------------------------------------|---------------------------------------|--|--|--|

| Saída Y0  | endereço inicial: C000H — endereço final: C3FFH — | · · · · · · · · · · · · · · · · · · · |  |  |  |

| Saída Y1  | endereço inicial: C400H<br>endereço final: C7FFH: |                                       |  |  |  |

| Saída Y2  | endereço inicial: C800H — endereço final: CBFFH — |                                       |  |  |  |

| Saída Y3  | endereço inicial: CC00H — endereço final: CFFFH — | · · · · · · · · · · · · · · · · · · · |  |  |  |

#### EXERCÍCIOS PROPOSTOS (continuação):

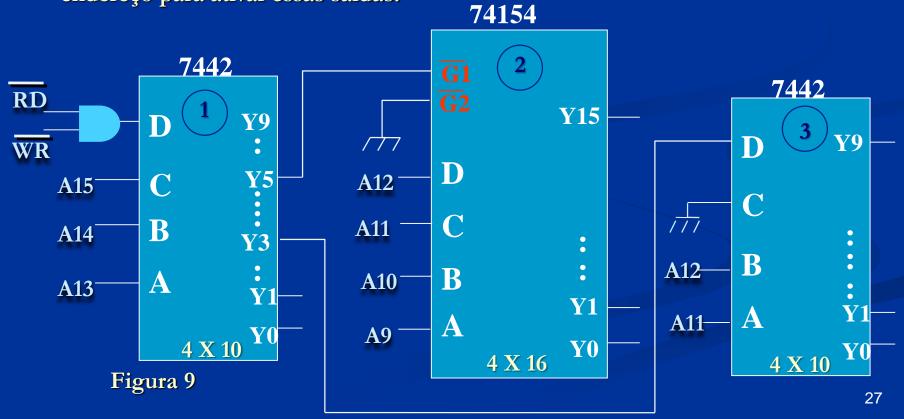

Exercício Nº9:

- •Qual é o decodificador mestre?

- •Quais os valores de A15, A14 e A13 que selecionam o decodificador 2?

- •Qual a faixa de endereço que é selecionada pelo decodificador 2?

- •Quais saídas do decodificador 3 que podem ser selecionadas quando a saída Y3 do decodificador 1 está ativa?

- •Qual a faixa de endereços que o decodificador 3 seleciona?

- •Para a saída Y6 dos decodificadores 2 e 3, quais são os valores das linhas de endereço para ativar essas saídas?

#### EXERCÍCIOS PROPOSTOS (continuação):

Resposta Exercício Nº9:

•Qual é o decodificador mestre:

Resp: é o decodificador 1

•Quais os valores de A15, A14 e A13 que selecionam o decodificador 2?

Resp: são os valores 101, respectivamente para ativa a saída Y5 do decodificador 1 que está ligada ao decodificador 2

•Qual a faixa de endereço que é selecionada pelo decodificador 2?

Resp: É a faixa da saída Y5 do decodificador 1 que é:

A000h a BFFFh

•Quais saídas do decodificador 3 que podem ser selecionadas quando a saída Y3 do decodificador 1 está ativa?

Resp: Nesse circuito de lógica de seleção apenas podem ser ligados dispositivos nas saídas Y0, Y1, Y2 e Y3 do decodificador 3, pois só essas saídas podem estar ativas quando Y3 do decodificador 1 estiver ativo(Y3=0), estando este ligado à entrada D do decodificador 3 e a entrada C do decodificador 3 também aterrada, só ativam as saídas de Y0 a Y3 do decodificador 3

•Qual a faixa de endereços que o decodificador 3 seleciona?

Resp: O decodificador 3 seleciona a faixa que é ativada pela saída y3 do decodificador 1, ou seja, 6000h a 7FFFh

•Para a saída Y6 dos decodificadores 2 e 3, quais são os valores das linhas de endereço para ativar essas saídas?

Resp: Y6 do decodificador 2 está ativo na faixa de endereços de AC00h a ADFFh e Y6 do decodificador 3 nunca estará ativo por nenhum endereço enviado pelo microprocessador

# **FIM**