## Departamento de Engenharia Elétrica e de Computação SEL 0415 - INTROD. À ORGANIZAÇÃO DE COMPUTADORES

## 8a. LISTA DE EXERCÍCIOS

## Lógica de Seleção

**1.** Faça o projeto da lógica de seleção para dividir o espaço de endereço do microprocessador em blocos de **4Kbytes**, especificando endereço inicial e final de cada bloco. Divida o bloco que inicia no endereço 4000H, em blocos de 1Kbytes e o bloco que inicia no endereço A000H em blocos de 512 bytes.

Usando **lógica de seleção absoluta**, ligue uma memória de 2kbytes, a partir do endereço 1000H, outra a partir do endereço 4000H e outra a partir do endereço A000H, determinando o endereço final de cada memória.

Repita o mesmo para **lógica de seleção** <u>não</u> <u>absoluta</u>, determinando os endereços fantasmas. Justifique quando a lógica de seleção absoluta não se aplicar.

- 2. Repita o exercício 2 para blocos de 2Kbytes.

- **3.** Faça o projeto da lógica de seleção para dividir o espaço de endereço do microprocessador em blocos de **1Kbytes**, especificando endereço inicial e final de cada bloco.

Divida o bloco que inicia no endereço 4000H, em blocos de 512 bytes e o bloco que inicia no endereço A000H em blocos de 256 bytes.

Usando **lógica de seleção absoluta**, ligue uma memória de 2kbytes, a partir do endereço 1000H, outra a partir do endereço 4000H e outra a partir do endereço A000H. determinando o endereço final de cada memória.

Repita o mesmo para **lógica de seleção** <u>não</u> absoluta, determinando os endereços fantasmas. Justifique quando a lógica de seleção absoluta não se aplicar.

**4-** Usando a técnica de *decodificação absoluta*, implemente um circuito lógico para seleção das seguintes memórias na sequência dada:

a. sistema de memórias (na sequência dada):

EPROM: 4 de 2Kx8 (end. Inicial: 0000H)

1 de 8Kx 8

RAM: 1 de 4Kx8 (end. Inicial: 5000H)

1 de 2Kx8 1 de 1Kx8

b. circuitos adicionais que podem ser usados no projeto:

74LS373, decodificadores 74LS154 e 7442, e portas lógicas.

**5-** Faça o projeto do item 4 para o mesmo sistema de memórias, utilizando a técnica de seleção *não absoluta*.

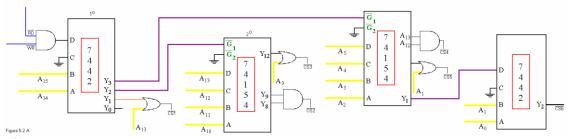

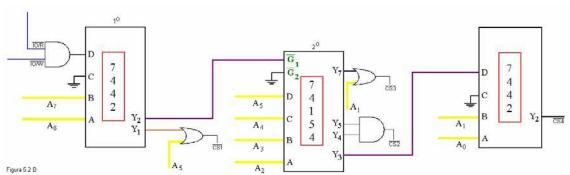

6. Para os circuitos de seleção dados nas figuras 6.1 e 6.2

## **6.1** determine:

- a) A faixa de endereço associada a cada decodificador.

- **b)** Determine qual organização de memória que pode ser conectada diretamente nas saídas de cada decodificador.

- **c)** A faixa de endereço das saídas CSi especificadas (inclusive endereços fantasma onde houver).

Figura 6.1

Figura 6.2

**6.2** Quanto ao tamanho do espaço de endereçamento selecionado pelo decodificador em relação ao tamanho da memória, o que ocorre no circuito da Figura 6.1, no 2<sub>0</sub> decodificador, quando uma memória de 2K x 8 na é ligada na saída Y3. Em seguida, faça o mesmo tipo de análise para memória de 512 x 8.