Departamento de Engenharia Elétrica e de Computação EESC-USP

## SEL-415 Introdução à Organização de Computadores

Princípio de Operação de memórias Expansão de Memórias Lógica de Seleção Aula 5

Profa. Luiza Maria Romeiro Codá

# Memórias Semicondutoras PRINCÍPIOS DE OPERAÇÃO DAS MEMÓRIAS

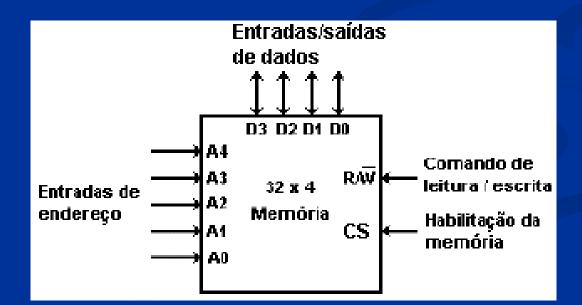

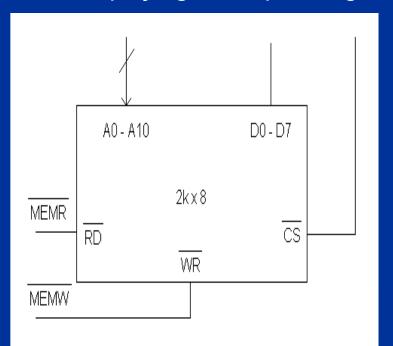

- Selecionar o endereço a ser acessado (leitura ou escrita);

- Se a operação for escrita, fornecer os dados de entrada;

- Se a operação for leitura, os dados estarão disponíveis na saída;

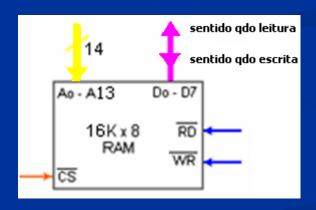

- Habilitar a memória (CS) para que as portas de I/O sejam liberadas para a operação desejada;

- Selecionar o tipo de operação: leitura ou escrita (R/W);

### Sinais nos pinos de controle

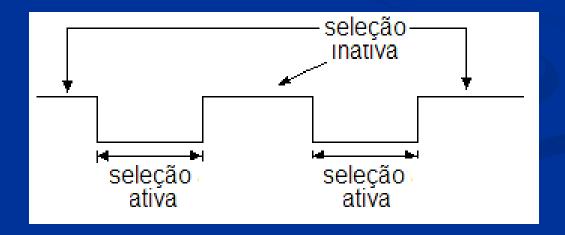

#### Sinal de Habilitação:

$\frac{\text{ME} - Memory Enable}{\text{E} - Enable}$   $\frac{\text{CS} - Chip Select}{\text{CS}}$

É um sinal de seleção, ativo em "0"  $\rightarrow$  seleciona o dispositivo. Se colocado em nível "1"  $\rightarrow$  desabilita o dispositvo , geralmente colocando em estado de alta-impedância (tristate).

### Sinais nos pinos de controle

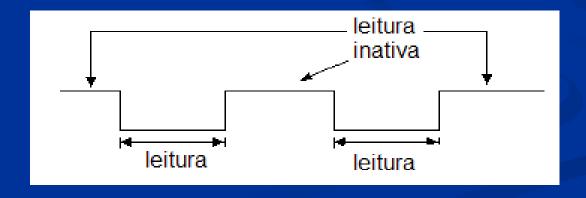

Sinal de Leitura:

$\overline{RD}$  – Read

É um sinal de leitura, ativo em nível lógico "0" → Coloca o dado armazenado na memória, na posição definida no duto de endereços, no duto de dados.

### Sinais nos pinos de controle

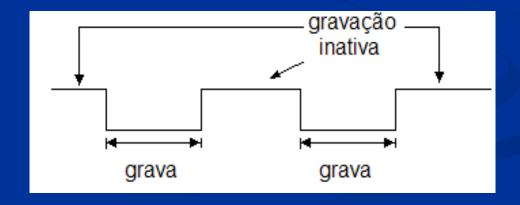

Sinal de Escrita:

$\overline{W}$  – Write

É um sinal de escrita (gravação), ativo em nível lógico "0" → Armazena o dado presente no duto de dados na posição de memória definida no duto de endereços.

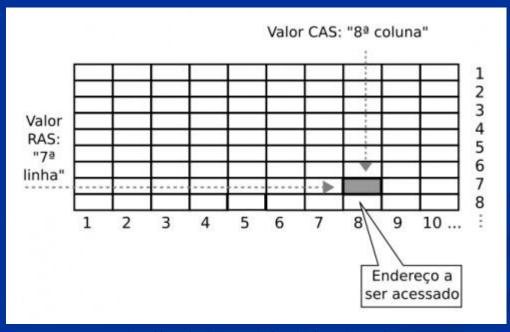

#### Acesso à Memória

- as células de memória são organizadas em uma espécie de matriz, ou seja, são orientadas em um esquema que lembra linhas(*wordline*) e colunas(*bitline*).

- controlador de memória: acessa a memória gerando primeiro o valor **RAS** (Row Address Strobe) (nºda linha de qual o endereço faz parte), e depois do valor **CAS** (Column Address Strobe) da coluna.

http://www.hardware.com.br/tutoriais/memoria-ram,

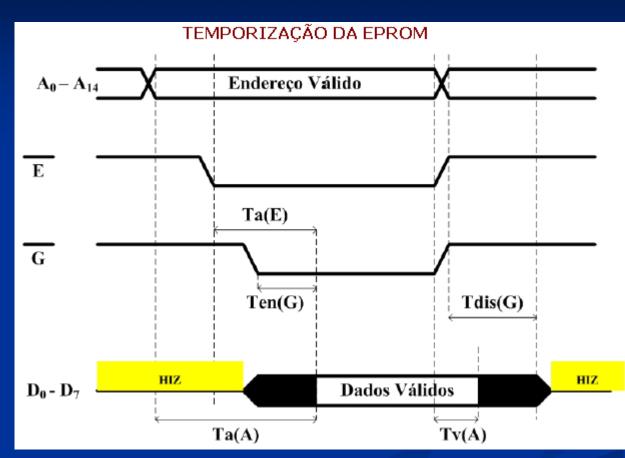

### Tempos de Chaveamento das Memórias Semicondutoras

Ta(A): Tempo de acesso após endereço válido.

Ta(E): Tempo de acesso após habilitação do chip.

Ten(G): Tempo de acesso após habilitação da saída (tristate).

Tv(A): Tempo em que os dados estão válidos após a mudança de endereço, de E ou de G.

Tdis(G): Tempo para desabilitar a saída após a mudança de endereço.

#### Ciclo de Leitura

Obs: Existe um atraso de propagação entre a aplicação das entradas (endereços e controle e seleção) de uma ROM e a aparição das saídas de dados durante a operação de leitura.

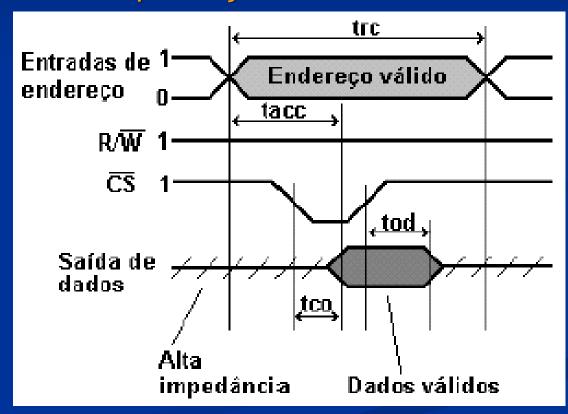

### TEMPOS DE CHAVEAMENTO DAS MEMÓRIAS SEMICONDUTORAS (Cont.)

trc = intervalo de duração do ciclo de leitura;

tacc = tempo de acesso à RAM;

tco = tempo que a saída da RAM leva para sair de alta impedância e ter um dado válido;

tod = tempo decorrido entre a desabilitação da RAM e o instante que as saídas da RAM vão para alta impedância.

#### Temporização memória RAM

Ciclo de Leitura

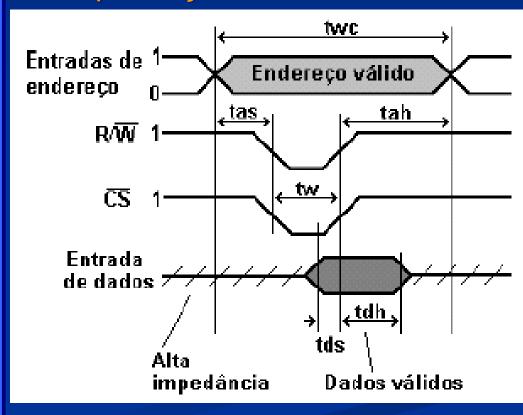

### TEMPOS DE CHAVEAMENTO DAS MEMÓRIAS SEMICONDUTORAS (cont.)

- tas = tempo para estabilização do duto de endereços, antes de habilitar a RAM;

- tah = intervalo necessário para que o duto de endereços permaneça estável;

- tw = tempo de escrita, onde /CS e R/W ficam em "0";

- tds = tempo em que os dados devem ser mantidos na entrada, antes da desabilitação de CS e W / R;

- tdh = tempo em que os dados devem ser mantidos na entrada depois da desabilitação de CS e R /W.

#### Temporização memória RAM

Ciclo de Escrita (ou Gravação)

### Expansão de Memórias Semicondutoras

### Expansão de Memórias

- a) Aumentar o número de bits da palavra:

- \* Exemplo:

- + Organização desejada: **2K x 8** (EPROM ou RAM)

- + Memória disponível: 2K x 4

- b) Aumentar o número de palavras (endereços):

- \* Exemplo:

- + Organização desejada: 4K x 8 (EPROM ou RAM)

- + Memória disponível: 2K x 8

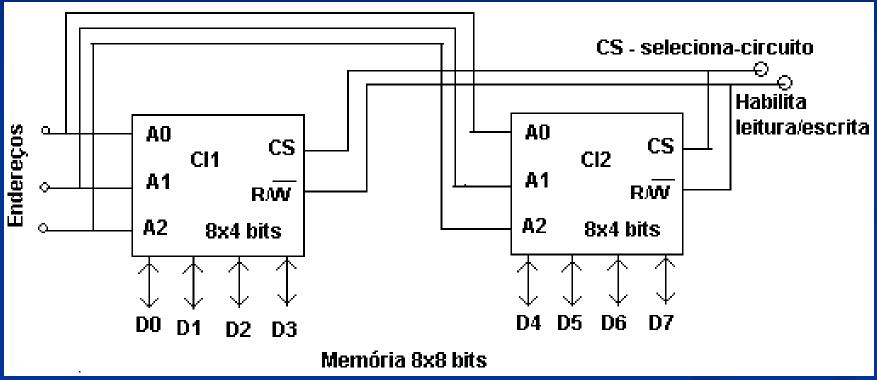

#### Aumentar o Tamanho (nº de bits) da Palavra

Dois CI's com 3 linhas de endereços → 2³ = 8 endereços. Cada endereço aponta para uma palavras de 4 bits (8x4), ligados de modo a formar uma memória de 8 palavras de 8 bits (8 x8)

- O duto de endereços e os pinos de controle dos CIs são interligados;

- O duto de dados fica dividido entre os Cls, de forma que cada Cl contribui com uma parcela do dado

- 4 MSB no Cl2 pino D7

- 4 LSB no Cl1 pino D0

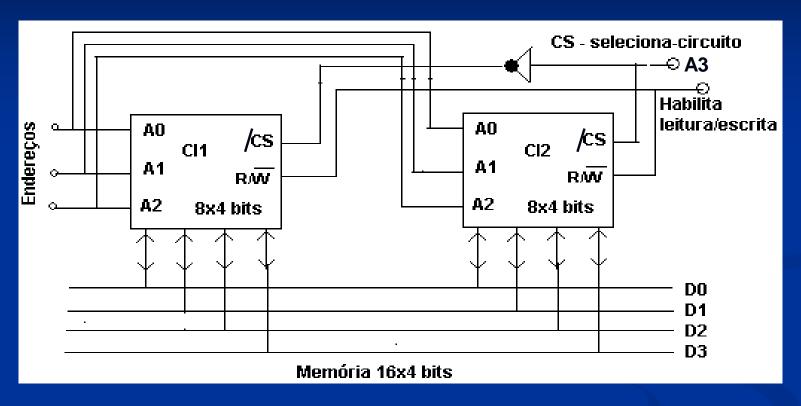

#### Aumentar o Nº de Palavras (células)

Dois Cl's com 8 palavras de 4 bits cada (8x4), ligados de modo a formar uma memória de 16 palavras(células) de 4 bits (16x4)

- O duto de dados, endereços e o pino de R/W dos CIs são interligados;

- O pino de controle (/CS) dos CIs **não** recebem o mesmo sinal; a seleção de CI1 e CI2 é feita através da linha de endereço A3, como segue:

- Pino de endereço A3 = 1 Seleciona o CI1 (8 end. mais signif.)

- Pino de endereço A3 = 0 Seleciona o CI2 (8 end. menos signif.)

#### Aumentar o Nº de Palavras

- O duto de dados, endereços e o pino de R/W dos CIs são interligados;

- O pino de controle (/CS) dos CIs não recebem o mesmo sinal; ;a seleção de CI1 e CI2 é feita através da linha de endereço A3, como segue:

- Pino de endereço A3 = 1 Seleciona o CI1 (8 end. mais signif.)

- Pino de endereço A3 = 0 Seleciona o CI2 (8 end. menos signif.)

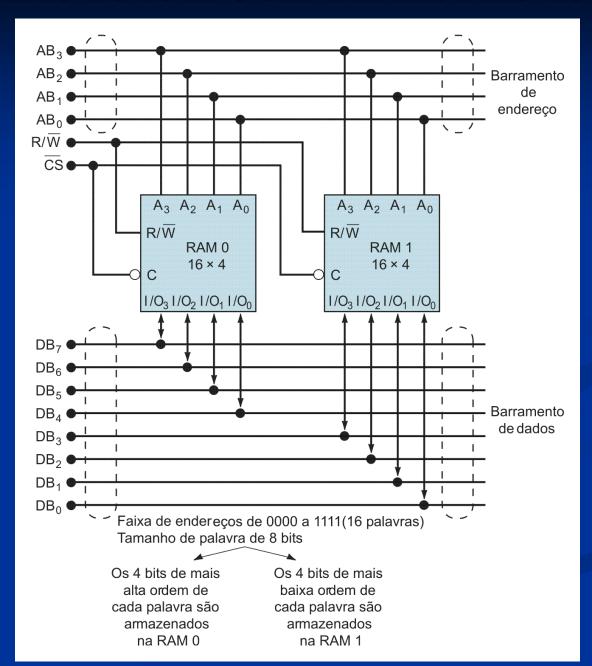

#### Duas RAMs de 16 X 4 em um módulo de 16 X 8

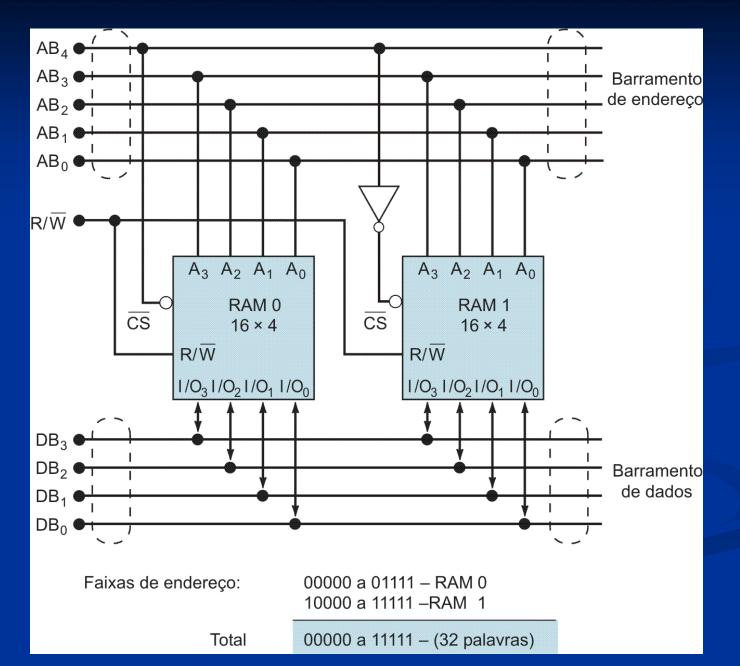

#### Duas RAMs de 16 X 4 em um módulo de 32 X 4

Tabela 2.1 Grandezas Usadas para Abreviar Valores em Computação

| Nome da unidade | Valor em potência de 2 | Valor em unidades                 |

|-----------------|------------------------|-----------------------------------|

| 1K (1 quilo)    | 210                    | 1024                              |

| 1M (1 mega)     | $1024K = 2^{20}$       | 1.048.576                         |

| 1G (1 giga)     | $1024M = 2^{30}$       | 1.073.741.824                     |

| 1T (1 tera)     | $2^{40}$               | 1.099.511.627.776                 |

| 1P (1 peta)     | 2 <sup>50</sup>        | 1.125.899.906.843.624             |

| 1Ex (1 exa)     | $2^{60}$               | 1.152.921.504.607.870.976         |

| 1Z (1 zeta)     | 270                    | 1.180.591.620.718.458.879.424     |

| 1Y (1 yotta)    | $2^{80}$               | 1.208.925.819.615.701.892.530.176 |

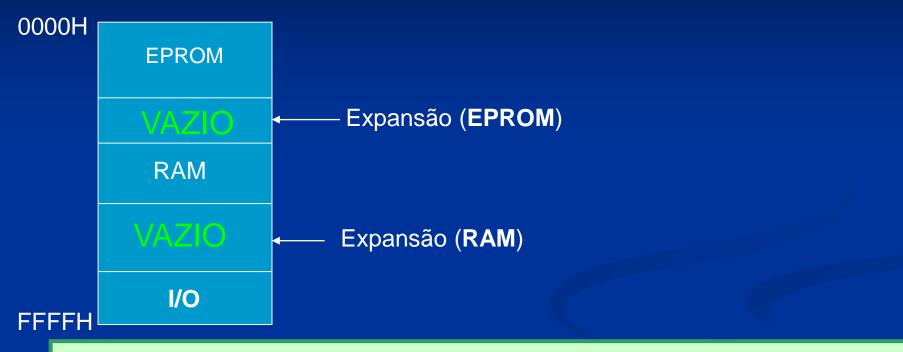

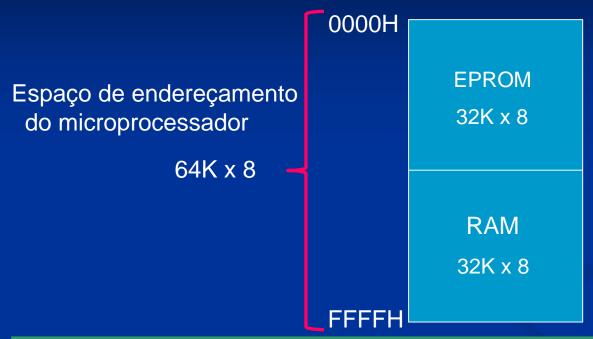

# Lógica de Seleção de Memória

Mapeamento

#### 1. Seleção de memórias e dispositivos de I/O

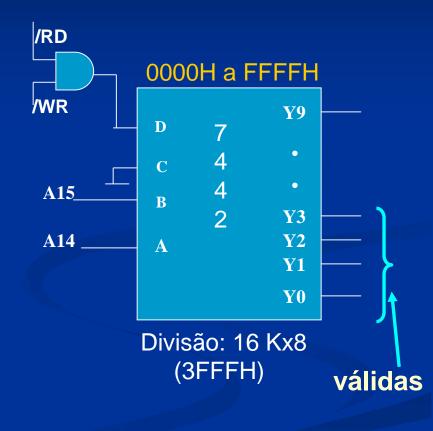

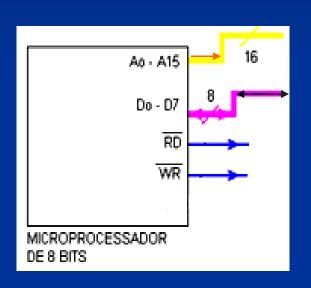

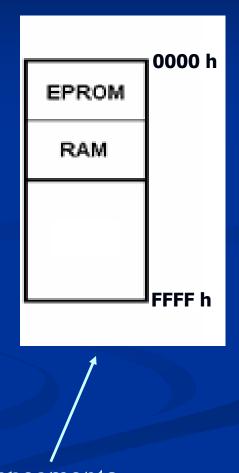

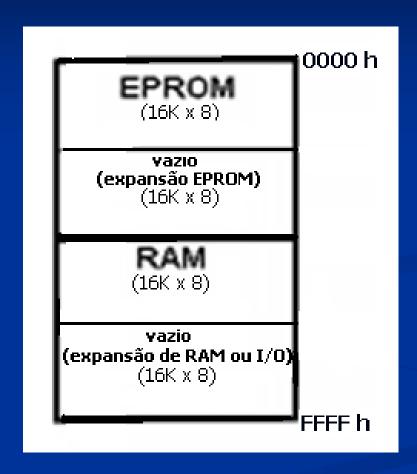

- Um microprocessador que tem duto de endereços de 16 bits e duto de dados de 8 bits, consegue endereçar 2 16 = 65536 (ou 64K) bytes

- As 64K posições que o microprocessador consegue endereçar podem ser representadas graficamente por um retângulo dividido em 64K posições, que é denominado **espaço de endereços do microprocessador**

Dentro do **espaço de endereços** de 64K bytes que o microprocessador consegue endereçar, são mapeadas as memórias e os dispositivos de I/O

A "Lógica de Seleção", construída pelo projetista, define as faixas de endereços do µP que irão selecionar cada uma das memórias e dispositivos

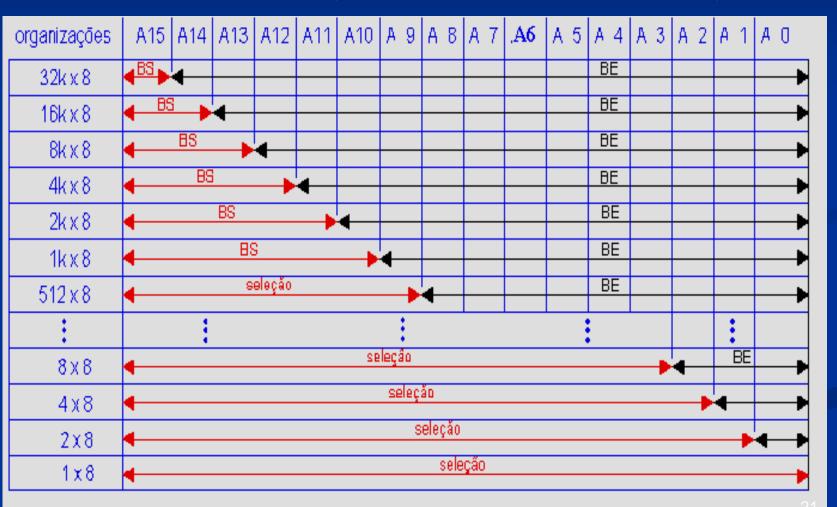

O endereço de **16 bits**, gerado pelo **uP** pode ser visto como sendo constituído por <u>duas partes</u> (tabela 1) :

**BE:** Bits de endereçamento do chip

BS: Bits de seleção

Tabela 1 – Sinais de seleção BS para diferentes organizações

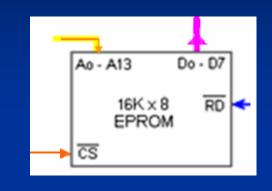

O endereço de **16 bits**, gerado pelo **uP para endereçar** cada memória de 32Kx8, pode ser visto como sendo constituído por <u>duas partes</u> (tabela 1)

**BE:** Bits de endereçamento dos chips de memória de 16Kx8 de A<sub>14</sub> a A<sub>0</sub>

BS: Bit de seleção dos chips de memória de 32Kx8 é A<sub>15</sub>

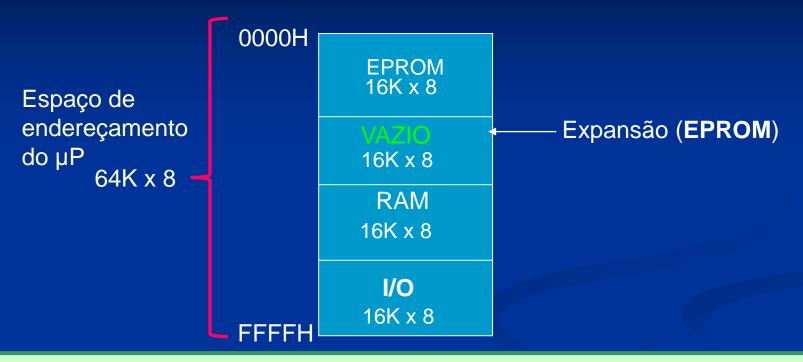

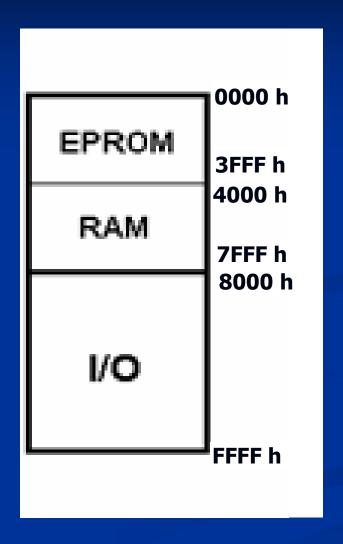

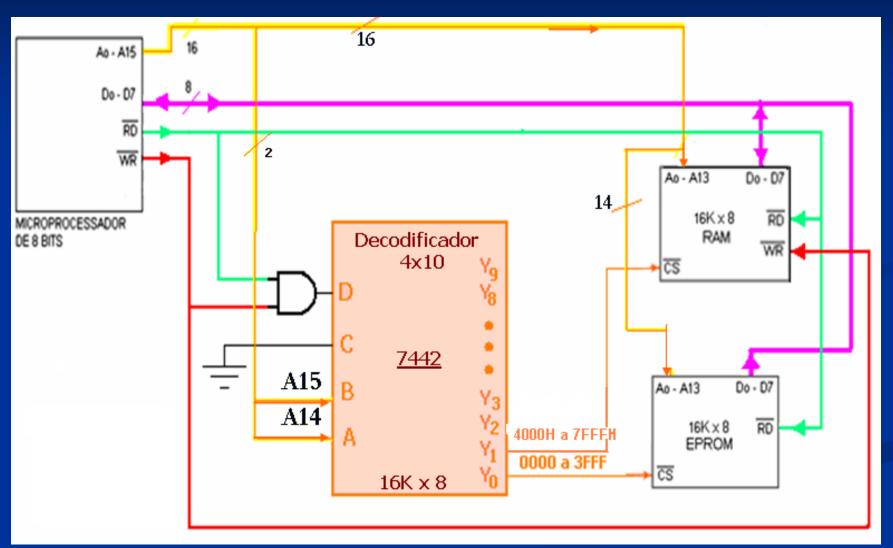

O endereço de **16 bits**, gerado pelo **µP para endereçar** cada memória de e dispositivos de I/O de 16Kx8, pode ser visto como sendo constituído por <u>duas partes</u> (tabela 1) :

**BE:** Bits de endereçamento dos chip de memória e dispositivos de I/O de 16Kx8 de  $A_{13}$  a  $A_0$

**BS:** Bits de seleção chip de memória e dispositivos de I/O de 16Kx8 são A<sub>15</sub> e A<sub>14</sub>

2. Número de posições de memória (em hexadecimal) para cada organização.

Fazendo-se os bits de seleção (BS) iguais a zero, e bits de endereçamento (BE), iguais a "1", na tabela 1, é possível determinar o (número de posições – 1) ocupadas por cada organização:

32k x 8: 7FFFH 2k x 8: 07FFH 8 x 8: 0007H

16k x 8: 3FFFH 1k x 8: 03FFH 4 x 8: 0003H

8k x 8 : 1FFFH 512 x 8 : 01FFH 2 x 8 : 0001H

$4k \times 8 : 0FFFH : 1 \times 8 : 0000H$

Esse valor é somado ao endereço inicial, no espaço de endereçamento, para se obter o endereço final da memória

|                       |                                | Linhas de Endereço do<br>Microprocessador |                     |                     |

|-----------------------|--------------------------------|-------------------------------------------|---------------------|---------------------|

| Blocos de<br>Memórias | nº de<br>Linhas de<br>Endereço | Seleção da<br>Memória                     | bits de<br>Endereço | Tamanho<br>do Bloco |

| 32K X8                | 15                             | A15                                       | A0 até<br>A14       | 7FFFH               |

| 16K X8                | 14                             | A14 até<br>A15                            | A0 até<br>A13       | 3FFFH               |

| 8K X8                 | 13                             | A13 até<br>A15                            | A0 até<br>A12       | 1FFFH               |

| 4K X8                 | 12                             | A12 até<br>A15                            | A0 até<br>A11       | OFFFH               |

| 2K X8                 | 11                             | A11 até<br>A15                            | A0 até<br>A10       | 07FFH               |

| 1K X8                 | 10                             | A10 até<br>A15                            | A0 até A9           | 03FFH               |

Relação entre

os blocos de

memórias e as

linhas de

endereço

de um

microprocessador

de 16 linhas (bits)

de endereço

| Blocos de<br>Memória | n.o de linhas<br>de endereço | Bits de<br>seleção | Bits de<br>endereço | Tamanho<br>do bloco |

|----------------------|------------------------------|--------------------|---------------------|---------------------|

| .512 X8              | 9                            | A9 até<br>A15      | A0 até A8           | 01FFH               |

| .256 X8              | 8                            | A8 até<br>A15      | A0 até A7           | 00FFH               |

| 128 x 8              | 7                            | A7. até<br>A15     | A0 até<br>A6        | 007FH               |

| 64 x8                | 6                            | A6 até<br>A15      | A0 até A5           | 003FH               |

| 32 x8                | 5                            | A5 até A15         | A0 até A4           | 001FH               |

| 16 ×8                | 4                            | A4 até A15         | A0 até A3           | 000FH               |

| 8 x 8                | 3                            | A3. até<br>A15     | A0 até<br>A2        | 0007H               |

| 4 x 8                | 2                            | A 2 até<br>A15     | A0 até A1           | 0003H               |

| .2 x8                | 1                            | A1 até A15         | A0                  | 0001H               |

| 1 ×8                 | 0                            | A0 até A15         | nenhum              | 0000H               |

Relação entre

os blocos de

memórias e as

linhas de

endereço

de um

microprocessador

de 16 linhas (bits)

de endereço

Exemplo: considerando endereço inicial = 8000H

|       | end. Inicial | end. Final |

|-------|--------------|------------|

| 32Kx8 | 8000H        | FFFFH      |

| 8KX8  | 8000H        | 9FFFH      |

| 1KX8  | 8000H        | 83FFH      |

|       |              |            |

| 8X8   | 8000H        | 8007H      |

| 4X8   | 8000H        | 8003H      |

| 2X8   | 8000H        | 8001H      |

| 1X8   | 8000H        | 8000H      |

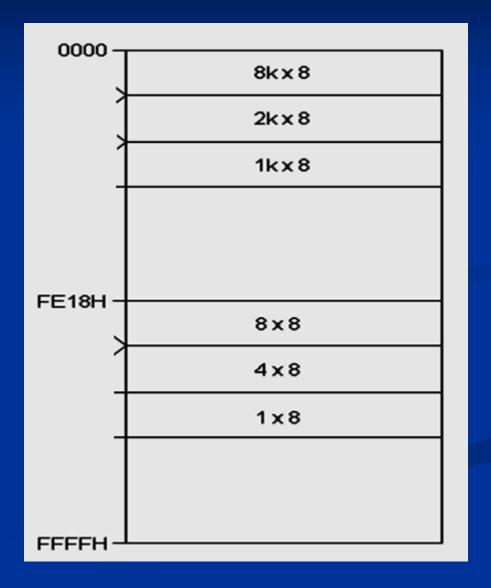

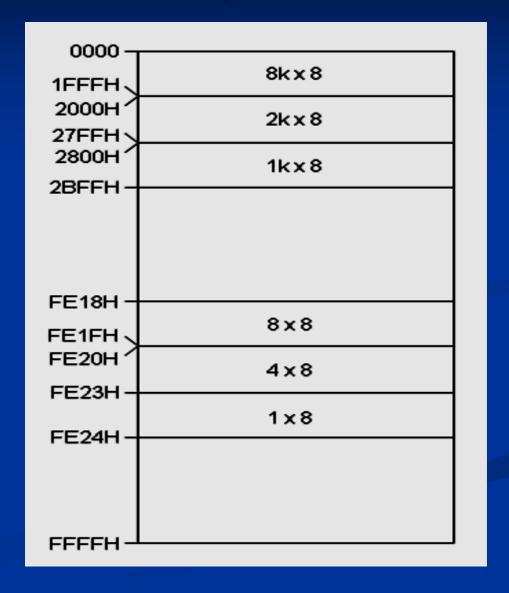

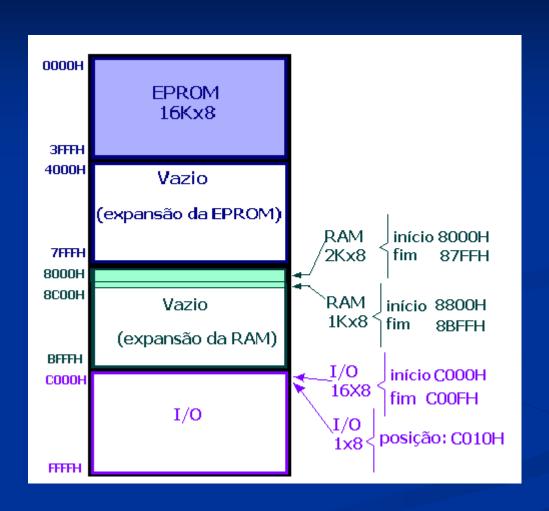

Exercício: Encontrar o endereço inicial e final, para as organizações de memória e de I/O mapeadas na Figura ao lado

Resposta: Endereço inicial e final para as organizações de memória e de I/O

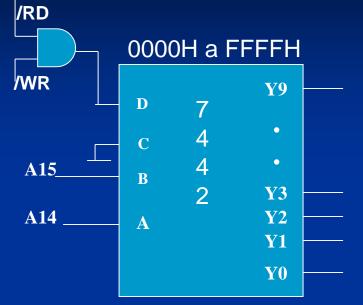

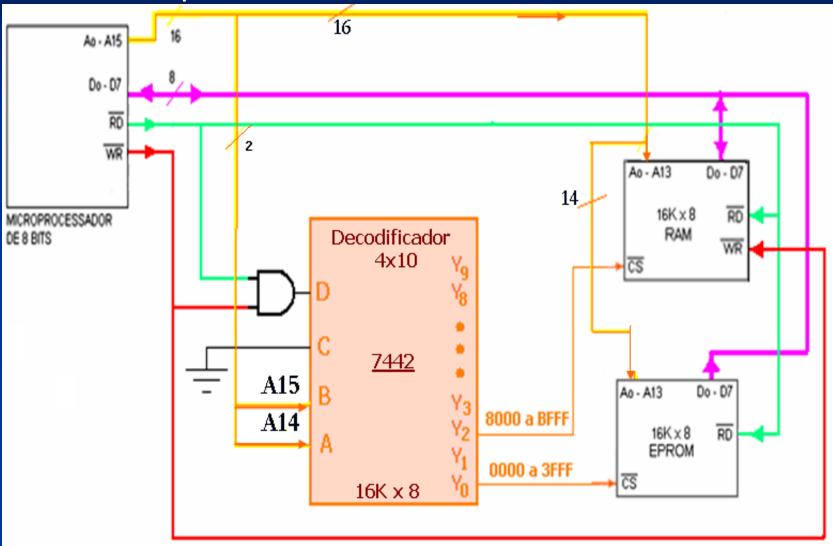

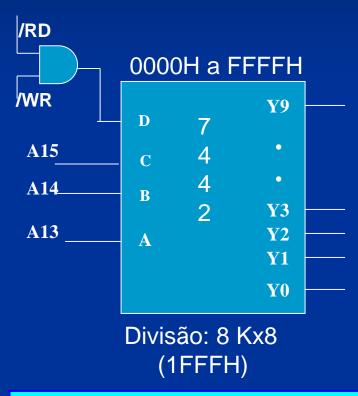

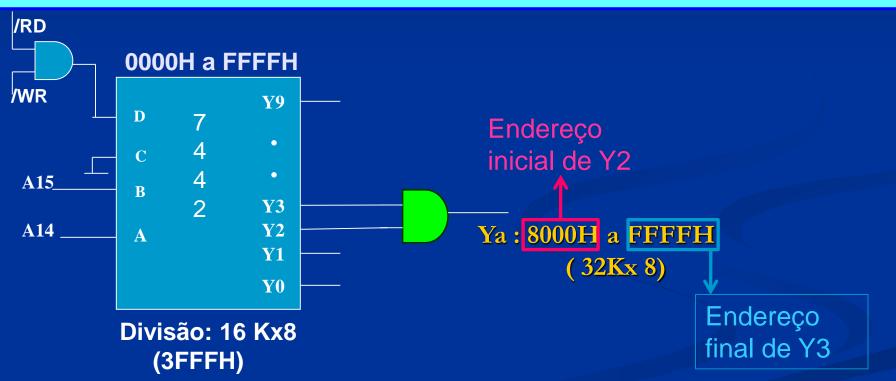

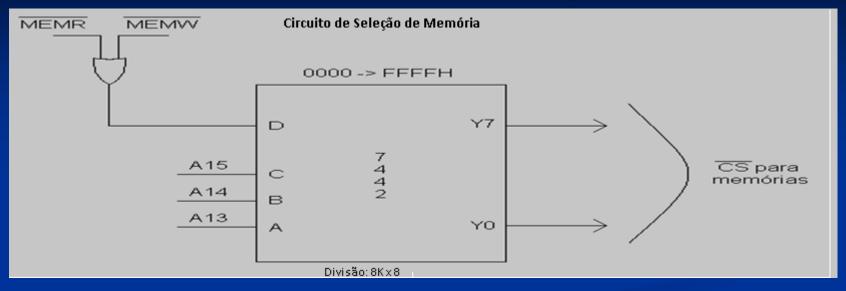

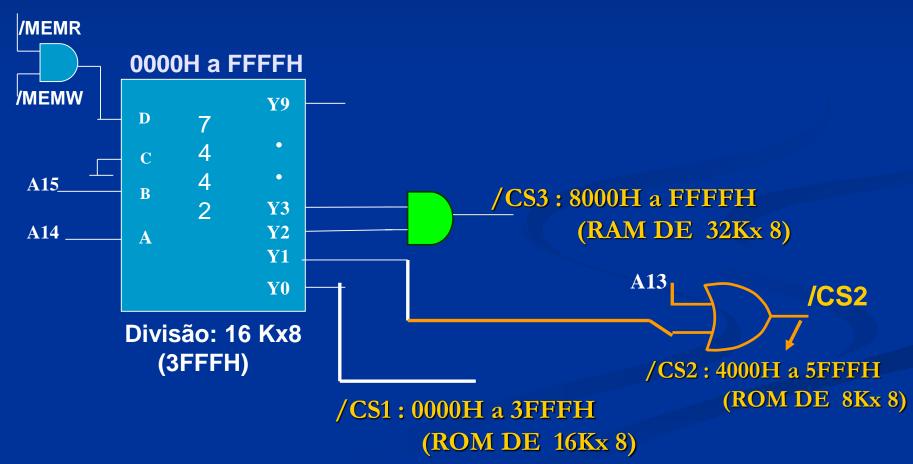

A lógica de seleção implementada com circuitos decodificadores garante a seleção de **uma única memória ou interface**, que se comunicará com o microprocessador.

- Cada decodificador fica "dentro" de um espaço de endereço, e divide esse espaço em blocos menores.

- O tamanho da divisão depende de qual é o **bit de seleção** menos significativo conectado na entrada do decodificador ( ver tabela 1) .

#### **Exemplo:**

(3FFFH)

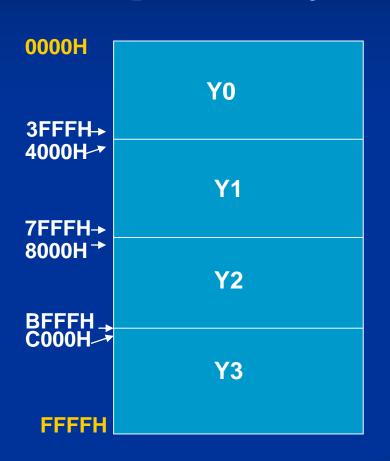

- Espaço de endereço: **0000 a FFFFH** (o decodificador não é selecionado por nenhum outro decodificador )

- <u>tamanho da divisão</u>: **16 Kx8**, pois o bit menos significativo é o **A14**

- pode-se **conectar direto** nesse decodificador organizações que tem linhas de endereço de A0 A13

Quais saídas do decodificador que podem ser ativadas ? Qual a faixa de endereço associada a cada saida?

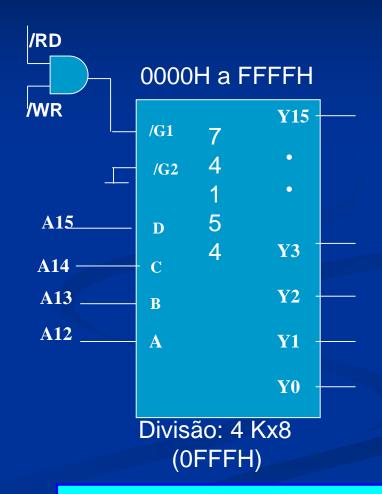

- Espaço de endereço: **0000 a FFFFH** (o decodificador não é selecionado por nenhum outro decodificador )

- <u>tamanho da divisão</u>: **16 Kx8**, pois o bit menos significativo é o **A14**

- pode-se **conectar direto** nesse decodificador organizações que tem linhas de endereço de A0 A13

Divisão: 16 Kx8 (3FFFH)

| Saídas válidas para serem usadas como /CS: | faixa de endereço |

|--------------------------------------------|-------------------|

| <b>Y0</b> : (A15, A14) = (0,0)             |                   |

| <b>Y1</b> : (A15, A14) = (0,1)             | 4000H até 7FFFH   |

| <b>Y2</b> : (A15, A14) = (1,0)             |                   |

| <b>Y3</b> : (A15, A14) = (1,1)             |                   |

Cada saída **válida** do decodificador, que pode ser usada como saída de seleção (/**CS**), tem a ela associada uma **faixa de endereço**, determinada pelos bits de endereço (seleção) conectados nas entradas deste decodificador.

Há duas maneiras de se determinar a faixa de endereço da saída:

- a. Soma do bloco divisor ao endereço inicial de cada saída válida do decodificador

- b. determina-se o endereço inicial e final associado à saída do decodificador como segue:

- endereço inicial: valor dos bits de seleção conectados no decodificador, que ativa a saída. Os demais bits em "0".

- **endereço final:** valor dos bits de seleção conectados no decodificador, que ativa a saída. Os demais bits em "1"

#### Utilizando o mesmo exemplo do decodificador anterior:

**a** . Soma do bloco divisor ao endereço inicial de cada saída **tamanho do bloco divisor** = **3FFFH** (16 K x 8)

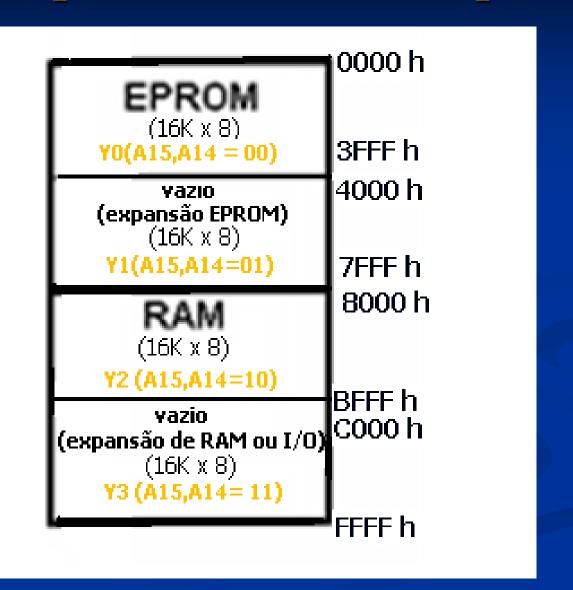

Y0 = 0000 a 3FFFH Y1 = 4000H a 7FFFH

Y2 = 8000H a BFFFH Y3 = C000H a FFFFH

| <b>b.</b> Valor dos bits de seleção (A15 e A14) |                                                   | A15A0 |

|-------------------------------------------------|---------------------------------------------------|-------|

| Saída Y0                                        | endereço inicial: 0000H — endereço final: 3FFFH — |       |

| Saída Y1                                        | endereço inicial: 4000H — endereço final: 7FFFH:  |       |

| Saída Y2                                        | endereço inicial: 8000H — endereço final: BFFFH — |       |

| Saída Y3                                        | endereço inicial: C000H — endereço final: DFFFH   |       |

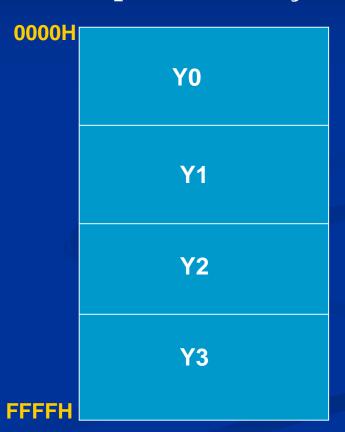

Dado o mapa de endereço ao lado:

a. como seria a ligação do decodificador(7442) para obter a divisão do espaço de endereços de 64Kbytes em 4 espaços iguais?

b. Qual o tamanho de cada bloco em hexadecimal?

c. Qual o endereço inicial e final em (hexadecimal) de cada bloco?

#### Mapa de endereços

#### Mapa de endereços

### Como ligar o µP às Memórias?

| Ló     | gica | a de | e Se | eleç | ão | do į | μP | _ ] | Lin | has | de | Er | ıde | reç | os |            | M    | lemór       | ia   |

|--------|------|------|------|------|----|------|----|-----|-----|-----|----|----|-----|-----|----|------------|------|-------------|------|

| Tipo   |      |      |      |      |    |      |    |     |     |     |    |    |     |     |    | Início (H) |      | Fim (H)     |      |

| ROM    | 0    | 0    | 0    | 0    | 0  | 0    | 0  | 0   | 0   | 0   | 0  | 0  | 0   | 0   | 0  | 0          | 0000 | 16k         |      |

| KOM    | 0    | 0    | 1    | 1    | 1  | 1    | 1  | 1   | 1   | 1   | 1  | 1  | 1   | 1   | 1  | 1          |      | TOK         | 3FFF |

| RAM    |      |      |      |      |    |      |    |     |     |     |    |    |     |     |    |            | 4000 | 16k         |      |

| IXAIVI |      |      |      |      |    |      |    |     |     |     |    |    |     |     |    |            |      | TOK         | 7FFF |

| I/0    |      |      |      |      |    |      |    |     |     |     |    |    |     |     |    |            | 8000 | 32k         |      |

| 1/0    |      |      |      |      |    |      |    |     |     |     |    |    |     |     |    |            |      | <i>32</i> K | FFFF |

| Lóạ    | gica | a de | e Se | leç | ão          | do į | μP        | _ ]       | Lin       | has       | de        | Er        | ıde        | reç       | os        |           | M          | lemór       | ia      |

|--------|------|------|------|-----|-------------|------|-----------|-----------|-----------|-----------|-----------|-----------|------------|-----------|-----------|-----------|------------|-------------|---------|

| Tipo   | A15  | A14  | A13  | A12 | <b>A</b> 11 | A10  | <b>A9</b> | <b>A8</b> | <b>A7</b> | <b>A6</b> | <b>A5</b> | <b>A4</b> | <b>A</b> 3 | <b>A2</b> | <b>A1</b> | <b>A0</b> | Início (H) |             | Fim (H) |

| ROM    | 0    | 0    | 0    | 0   | 0           | 0    | 0         | 0         | 0         | 0         | 0         | 0         | 0          | 0         | 0         | 0         | 0000       | 16k         |         |

| KOM    | 0    | 0    | 1    | 1   | 1           | 1    | 1         | 1         | 1         | 1         | 1         | 1         | 1          | 1         | 1         | 1         |            | TOK         | 3FFF    |

| RAM    | 0    | 1    | 0    | 0   | 0           | 0    | 0         | 0         | 0         | 0         | 0         | 0         | 0          | 0         | 0         | 0         | 4000       | 16k         |         |

| IXAIVI | 0    | 1    | 1    | 1   | 1           | 1    | 1         | 1         | 1         | 1         | 1         | 1         | 1          | 1         | 1         | 1         |            | TOK         | 7FFF    |

| I/0    | 1    | 0    | 0    | 0   | 0           | 0    | 0         | 0         | 0         | 0         | 0         | 0         | 0          | 0         | 0         | 0         | 8000       | 32k         |         |

| 1/0    | 1    | 1    | 1    | 1   | 1           | 1    | 1         | 1         | 1         | 1         | 1         | 1         | 1          | 1         | 1         | 1         |            | <i>32</i> K | FFFF    |

### Mapeamento

### Como ligar o µP às Memórias

### Mapeamento

| Ló                 | gic    | a d  | e S | ele | ção  | do   | μP | _  | Lir | ıha | s d | e Ei | nde | reç | os  |    | М          | ia   |         |

|--------------------|--------|------|-----|-----|------|------|----|----|-----|-----|-----|------|-----|-----|-----|----|------------|------|---------|

| Tipo               | A 15 . | A 14 | A13 | A12 | A 11 | A 10 | A9 | A8 | A7  | A6  | A5  | A4   | A3  | A2  | A 1 | AO | Início (H) |      | Fim (H) |

| DOM.               | 0      | 0    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0   | 0    | 0   | 0   | 0   | 0  | 0000       | 16k  |         |

| ROM                | 0      | 0    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1   | 1    | 1   | 1   | 1   | 1  |            | 102  | 3FFF    |

| vazio<br>expansão  |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    | 4000       | 16k  |         |

| expansão<br>de ROM |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    |            | 1010 | 7FFF    |

| RAM                |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    | 8000       | 16k  |         |

| TOAN               |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    |            | 1010 | BFFF    |

| vazio<br>expansão  |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    | C000       | 16k  |         |

| de RAM<br>ou I/O   |        |      |     |     |      |      |    |    |     |     |     |      |     |     |     |    |            | 1010 | FFFF    |

| Ló                 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |      |     |     |      |      |    |    |    |    |    |    |    |    |     | Memória |            |      |         |

|--------------------|---------------------------------------|------|-----|-----|------|------|----|----|----|----|----|----|----|----|-----|---------|------------|------|---------|

| Tipo               | A 15 .                                | A 14 | A13 | A12 | A 11 | A 10 | A9 | A8 | A7 | A6 | A5 | A4 | A3 | A2 | A 1 | AO      | Início (H) |      | Fim (H) |

|                    | _                                     | _    |     |     |      |      |    |    | ۰  | ۰  |    |    |    |    | ۰   |         | 0000       |      |         |

| ROM                | Ü                                     | 0    | 0   | 0   | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0       | 0000       | 16k  |         |

| 10101              | 0                                     | 0    | 1   | 1   | 1    | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1       |            |      | 3FFF    |

| vazio<br>expansão  | 0                                     | 1    | 0   | 0   | 0    | 0    | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0   | 0       | 4000       | 16k  |         |

| expansão<br>de ROM | 0                                     | 1    | 1   | 1   | 1    | 1    | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1  | 1   | 1       |            | TOK  | 7FFF    |

| RAM                |                                       |      |     |     |      |      |    |    |    |    |    |    |    |    |     |         | 8000       | 16k  |         |

| ICALVI             |                                       |      |     |     |      |      |    |    |    |    |    |    |    |    |     |         |            | IVIC | BFFF    |

| vazio<br>expansão  |                                       |      |     |     |      |      |    |    |    |    |    |    |    |    |     |         | C000       | 16k  |         |

| de RAM<br>ou I/O   |                                       |      |     |     |      |      |    |    |    |    |    |    |    |    |     |         |            | IOR  | FFFF    |

| Ló                 | gic                                   | a d  | e S | ele | ção  | do   | μP | _  | Lin | ıha | s do | e E: | nde | reç | os |      | М          | [emór | ia      |

|--------------------|---------------------------------------|------|-----|-----|------|------|----|----|-----|-----|------|------|-----|-----|----|------|------------|-------|---------|

| Tipo               | A 15 .                                | A 14 | A13 | A12 | A 11 | A 10 | A9 | A8 | A7  | A6  | A5   | A4   | A3  | A2  | A1 | A0   | Início (H) |       | Fim (H) |

|                    | Λ                                     | 0    | _   | ^   | Λ    | Λ    | Λ  | 0  |     | ^   | ^    | 0    | 0   | Λ   | Λ  | 0    | 0000       |       |         |

| ROM                | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |      |     |     |      |      |    |    |     |     |      |      |     |     |    | 0000 | 16k        |       |         |

|                    | 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1         |      |     |     |      |      |    |    |     |     |      |      |     |     |    |      |            | 3FFF  |         |

| vazio<br>exnansão  | 0                                     | 1    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0   | 0   | 0  | 0    | 4000       | 16k   |         |

| expansão<br>de ROM | 0                                     | 1    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1   | 1   | 1  | 1    |            | TOK   | 7FFF    |

| RAM                | 1                                     | 0    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0   | 0   | 0  | 0    | 8000       | 16k   |         |

| 105101             | 1                                     | 0    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1   | 1   | 1  | 1    |            | 1010  | BFFF    |

| vazio<br>expansão  |                                       |      |     |     |      |      |    |    |     |     |      |      |     |     |    |      | C000       | 16k   |         |

| de RAM<br>ou I/O   |                                       |      |     |     |      |      |    |    |     |     |      |      |     |     |    |      |            | TOIC  | FFFF    |

| Ló                               | gic    | a d  | e S | ele | ção  | do   | μP | _  | Lin | ıha | s do | e Ei | n de | reç | os |    | М          | [emór | ia      |

|----------------------------------|--------|------|-----|-----|------|------|----|----|-----|-----|------|------|------|-----|----|----|------------|-------|---------|

| Tipo                             | A 15 . | A 14 | A13 | A12 | A 11 | A 10 | A9 | A8 | A7  | A6  | A5   | A4   | A3   | A2  | A1 | AO | Início (H) |       | Fim (H) |

|                                  |        |      |     |     |      |      |    |    |     |     |      |      |      |     |    |    |            |       |         |

| ROM                              | 0      | 0    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0    | 0   | 0  | 0  | 0000       | 16k   |         |

| KOM                              | 0      | 0    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1    | 1   | 1  | 1  |            | TOIC  | 3FFF    |

| vazio<br>expansão                | 0      | 1    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0    | 0   | 0  | 0  | 4000       | 16k   |         |

| vazio<br>expansão<br>de ROM      | 0      | 1    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1    | 1   | 1  | 1  |            | IOK   | 7FFF    |

| RAM                              | 1      | 0    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0    | 0   | 0  | 0  | 8000       | 16k   |         |

| ICALVI                           | 1      | 0    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1    | 1   | 1  | 1  |            | IOR   | BFFF    |

| vazio<br>expansão                | 1      | 1    | 0   | 0   | 0    | 0    | 0  | 0  | 0   | 0   | 0    | 0    | 0    | 0   | 0  | 0  | C000       | 16k   |         |

| expansão   _<br>de RAM<br>ou I/O | 1      | 1    | 1   | 1   | 1    | 1    | 1  | 1  | 1   | 1   | 1    | 1    | 1    | 1   | 1  | 1  |            | TOR   | FFFF    |

### Como ligar o µP às Memórias?

### Mapeamento 2º exemplo

### Como ligar o µP às Memórias? Exemplo 3

### Mapeamento do Exemplo2

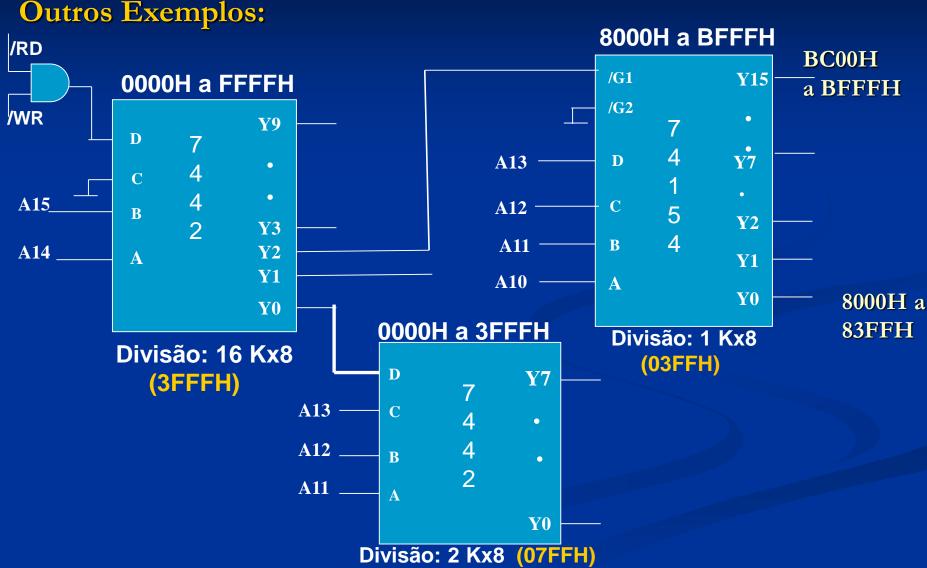

#### **Outros Exemplos:**

Saídas válida como /CS: Y0 a Y7

Saídas válida como /CS: Y0 a Y15

#### **Outros Exemplos:**

Exercício: 1. determinar a faixa de endereço associada a cada saída válida

2. Substituir o decodificador 74154 pelo 7442 e efetuar as ligações necessárias para selecionar a mesma faixa de endereço.

Exercício: 1. determinar a faixa de endereço associada a cada saída válida.

Pode-se escolher qualquer endereço inicial?

Resp: Não!!! há endereços que simplificam a lógica de seleção.

- Se a memória está "alinhada" com o endereço inicial, os bits de seleção tem o mesmo valor para qualquer posição da memória, o que simplifica a lógica de seleção

- a memória está alinhada com o endereço inicial se os **bits de endereçamento do bloco de memória** tem valor **zero** para o endereço inicial.

#### **Exemplo:**

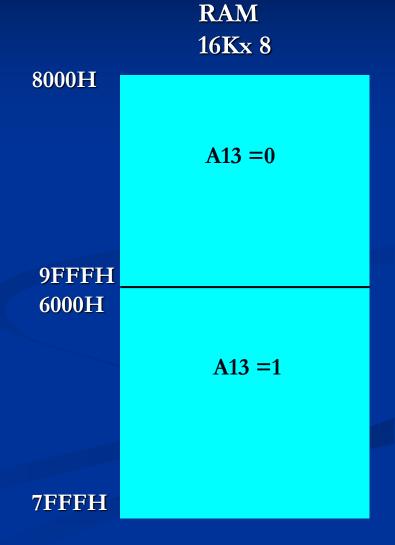

a) Memória não alinhada - RAM de 16Kx8

A13

END. INICIAL: 0 1 10 0000 0000 0000END. FINAL:

0000 H

3FFF H

4000 H

5FFF H

9FFFH

6000H

**EPROM** 16Kx 8

EPROM 8Kx 8

RAM 16Kx 8

\* A13 que é bit de endereçamento da memória, tem valor 1, para o end. inicial.

- Os bits de seleção para endereço inicial e final\_NÃO são os mesmos

- A lógica de seleção deve ser feita com divisão de 8Kx8 (ou menor), pois para esse bloco os bits de Endereço se mantém em 0.

6000 H: 0 1 10 0000 0000 0000

**END. FINAL:**

**9FFFH:** 1 0 01 1111 1111 1111

Obs: O chip da memória é acessado da metade até o fim (qdo A13=0) e depois do início até a metade(qdo A13=1)

#### B) Memória alinhada - RAM de 16Kx8

Pode ser criado um "buraco" (vazio) para o alinhamento

A13

END. INICIAL: 1000 0000 0000 0000 END. FINAL: 1011 1111 1111

- 0s bit de endereçamento da memória, A0 até A13, tem valor "0".

- ❖ Os bits de seleção, para endereço inicial e final, são os mesmos

- ❖ O lógica de seleção deve ser feita com divisão de 16Kx8, o mesmo tamanho da memória.

- No mapeamento das memórias, é interessante que as memórias do tipo EPROM sejam mapeadas <u>em sequência</u>, para se ter continuidade do programa armazenado.

- Memórias do tipo RAM também são mapeadas em sequência para se ter continuidade na área de dados.

- Para evitar a ocorrência de memória não alinhada, além da escolha do endereço inicial adequado, as memórias devem ser mapeadas de forma que as de maior organização ocupem os blocos iniciais no mapa de endereços

Pode-se combinar linhas de seleção através da lógica AND, para selecionar organizações de memória MAIORES do que a faixa de endereço das saídas de seleção

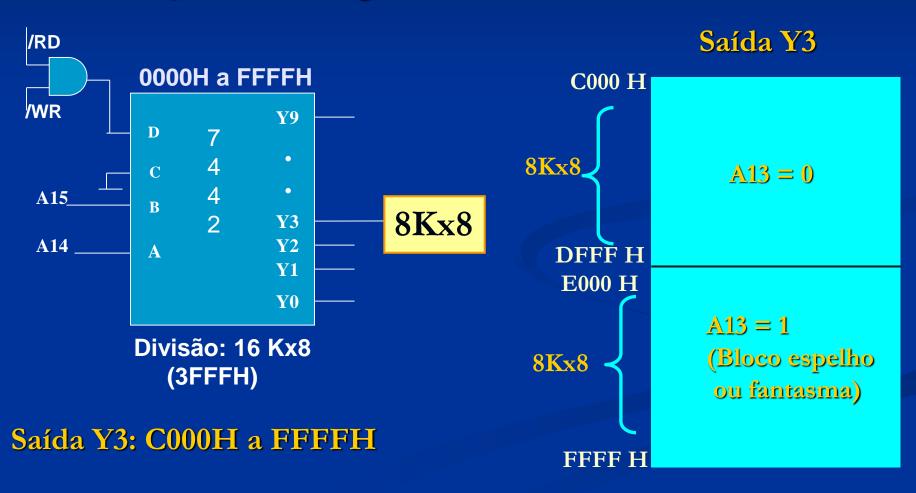

O que ocorre se uma memória com <u>organização menor</u> que a da saída de seleção, for interligada na saída Y3?

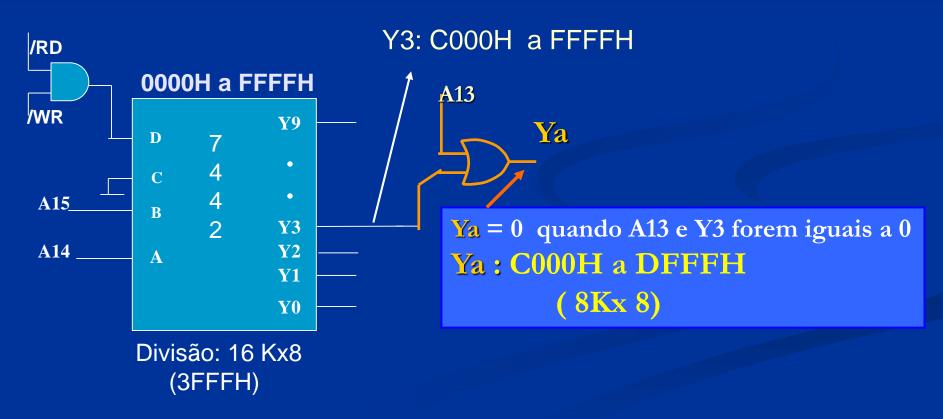

A13 é bit de seleção da memória de 8Kx8, mas NÃO está presente no decodificador, portanto é irrelevante, podendo valer 1 ou 0.

- ❖Os dois blocos de 8K podem ser usados para selecionar a memória de 8Kx8 : C000H a DFFFH e E000H a FFFFH.

- ❖Os dois blocos acessam as mesmas posições físicas das memórias, p. ex., C000H e E000H acessam a mesma posição da memória.

Pode-se combinar linhas de seleção através da lógica OR, combinada com linhas de endereço adequadas, para selecionar organizações de memória MENORES do que a faixa de endereço das saídas de seleção.

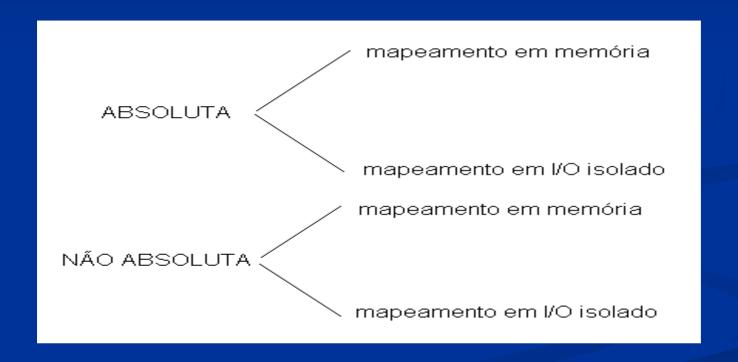

#### 3. Tipos de Lógica de Seleção

#### 3. Tipos de Lógica de Seleção

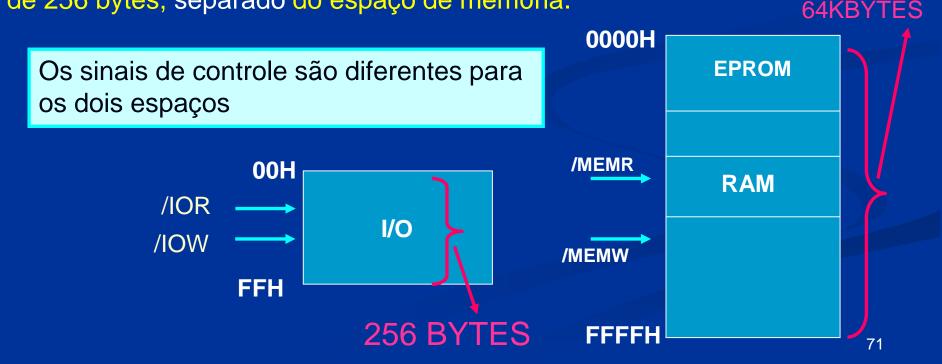

**Mapeamento em Memória:** no espaço de 64K bytes são mapeadas as memórias e os dispositivos de I/O

> os sinais de controle de leitura e gravação são <u>os mesmos</u> para memórias e para I/O

Mapeamento em I/O isolado: os dispositivos de I/O são mapeados num espaço de I/O separado do espaço de memória.

- ➤os sinais de controle de leitura e gravação são <u>diferentes</u> para os dois espaços

#### 3.1 Lógica de Seleção Absoluta

- São usados todos os bits de seleção do CHIP

- É selecionado um espaço que tem exatamente as dimensões do chip. Exemplo: para memória de 1k x 8 é selecionado um bloco de 1k x 8.

- Se a memória está "alinhada" com o endereço inicial, os bits de seleção tem o mesmo valor para qualquer posição da memória, o que simplifica a lógica de seleção

- a memória está alinhada com o endereço inicial se os bits de endereçamento do chip tem valor zero para o endereço inicial.

#### 3.1 Lógica de Seleção Absoluta

Vantagem: não há possibilidade de conflito de espaços de endereço.

**Desvantagem:** o hardware é mais complexo que o da lógica não absoluta, principalmente para interfaces que ocupam poucas posições de memória

#### 3.1.a Exemplos de lógica de seleção absoluta, Mapeamento em Memória

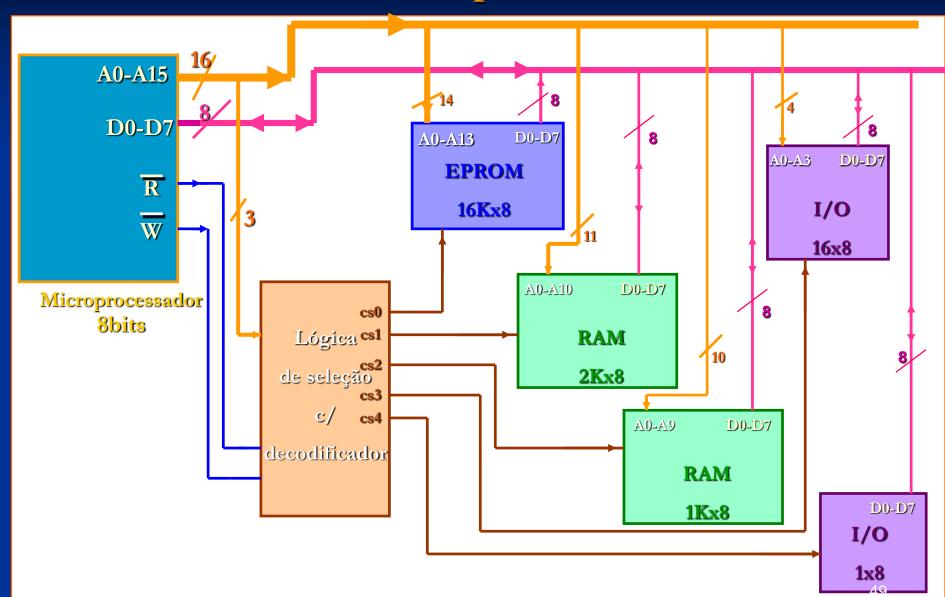

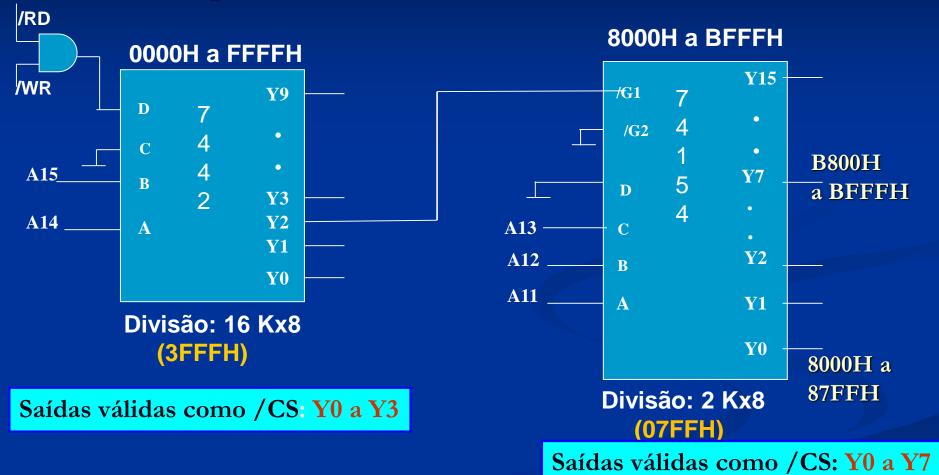

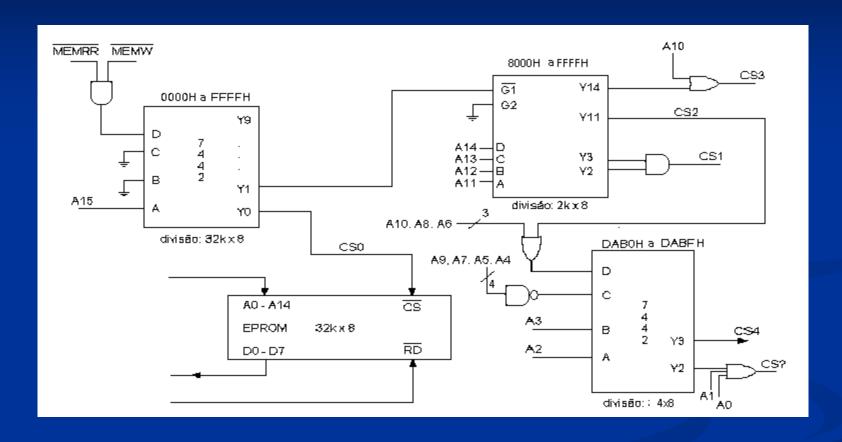

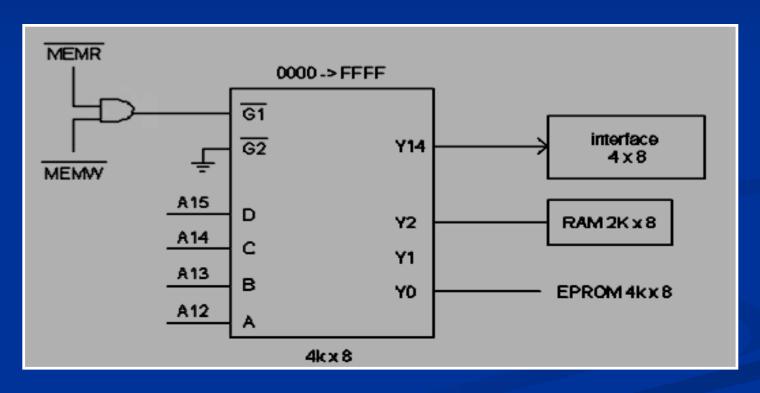

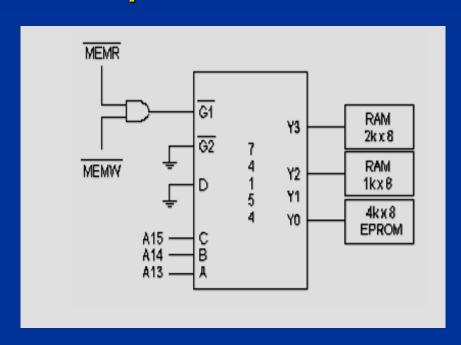

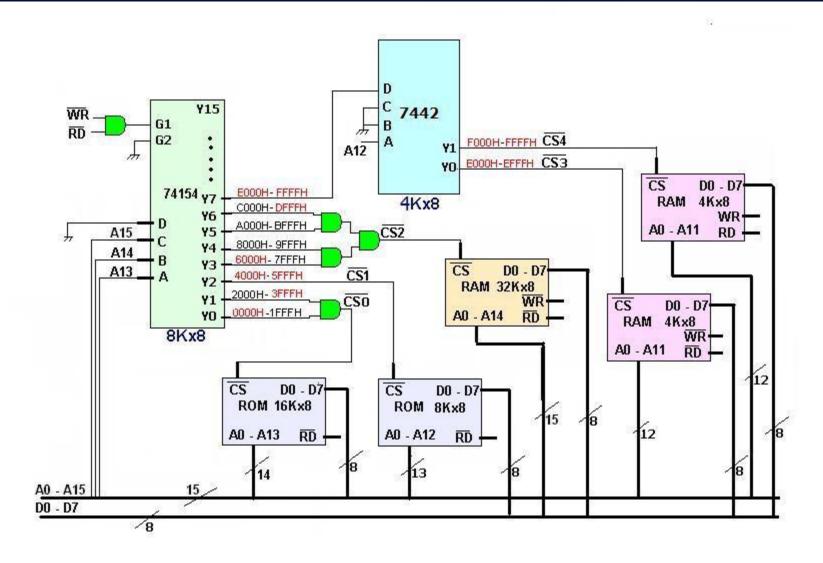

Para o circuito de seleção da figura 2 é determinada a faixa de endereço associada a cada saída de seleção CSi (tabela 2 e 3)

No espaço de 64K bytes são mapeadas as memórias e os dispositivos de I/O

RAM I/O

**EPROM**

Figura 2 - Exemplo de lógica de seleção absoluta, mapeamento em memória

Tabela 2 - Faixa de endereços para cada saída de seleção

|                  | A15    | A14    | A13    | A12    | A11             | A10    | А9     | A8     | Α7         | A6     | A5     | A4     | АЗ         | A2     | A1     | Α0     |

|------------------|--------|--------|--------|--------|-----------------|--------|--------|--------|------------|--------|--------|--------|------------|--------|--------|--------|

| CS0<br>(32k x 8) | 0      | 0<br>1 | 0<br>1 | 0<br>1 | 0               | 0<br>1 | 0<br>1 | 0<br>1 | 0 1        | 0<br>1 | 0<br>1 | 0<br>1 | 0 1        | 0<br>1 | 0<br>1 | 0<br>1 |

| CS1              | 1      | 0      | 0      | 1      | 0 1             | 0<br>1 | 0<br>1 | 0<br>1 | 0          | 0<br>1 | 0<br>1 | 0<br>1 | 0          | 0<br>1 | 0<br>1 | 0      |

| CS2              | 1      | 1      | 0      | 1      | 1<br>1 1<br>1 1 | 0<br>1 | 0<br>1 | 0<br>1 | 1 0<br>1 1 | 0<br>1 | 0<br>1 | 0<br>1 | 1 0<br>1 1 | 0<br>1 | 0<br>1 | 0      |

| CS3              | 1<br>1 | 1      | 1      | 1<br>1 | 0 0             | 0      | 0<br>1 | 0<br>1 | 0 1        | 0<br>1 | 0<br>1 | 0<br>1 | 0 1 1      | 0<br>1 | 0<br>1 | 0<br>1 |

| CS4              | 1<br>1 | 1      | 0      | 1      | 1<br>1 1<br>1 1 | 0      | 1      | 0      | 1 1        | 0      | 1      | 1      | 1 1 1      | 1      | 0<br>1 | 0      |

```

■ CS0: 0000 -> 7FFFH ; 32k \times 8

```

```

□ CS1: 9000H -> 9FFFH ; 4k x 8

```

```

\square CS2: D800H -> DFFFH ; 2k \times 8

```

□ CS3: F000H -> F3FFH ; 1k x 8

$\square$  CS4: DABCH -> DABFH ;  $4 \times 8$

**Tabela 3** - Faixa de endereços em hexadecimal, referentes à tabela 2

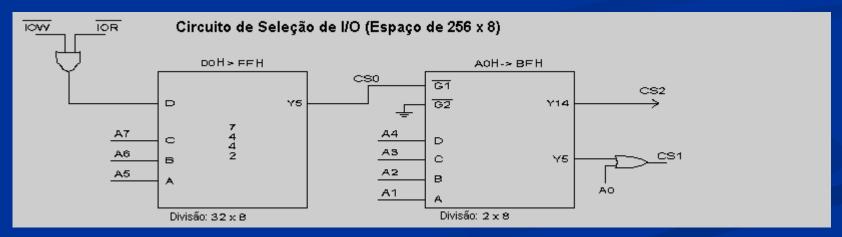

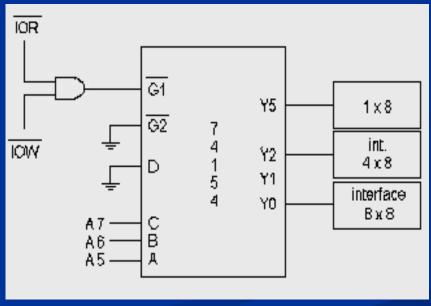

### 3.1.b Exemplos de lógica de seleção absoluta, Mapeamento em I/O Isolado

Para o circuito de seleção da figura 3 é determinada a faixa de endereço associada a cada saída de seleção CSi (tabela 4).

Os dispositivos de I/O são mapeados num espaço de I/O de 256 bytes, separado do espaço de memória.

Figura 3 - exemplo de lógica de seleção absoluta, mapeamento em I/O isolado 72

| CS0 1 0 1 0 0 0 0 1 0 0 0 0 1 0 1 1 1 1 1 | 0      |

|-------------------------------------------|--------|

|                                           |        |

|                                           | 0      |

| CS2 1 0 1 1 1 1 0 1 1 1 0                 | 0<br>1 |

```

CS0: A0H -> BFH -> espaço: 32 x 8

CS1: AAH -> espaço: 1 x 8

CS2: BCH -> BDH -> espaço: 2 x 8

```

Tabela 4 : mapa de endereços para o circuito de seleção de I/O da figura 3

### 3.2 Lógica de Seleção NÃO Absoluta

- Usa-se parte dos bits de seleção, na lógica de seleção

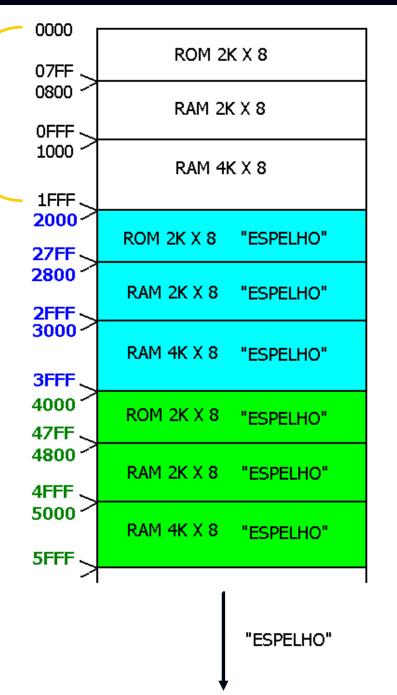

- os bits de seleção não usados geram espaços de endereço extra, associados ao dispositvo, denominados espaços de endereço fantasma;

- esse hardware de seleção é inadequado para área de dados seqüenciais;

- os endereços fantasmas não podem ser usados por outros chips, pois não são espaços livres.

3.2.a Lógica de Seleção NÃO Absoluta, mapeamento em memória

Figura 4 - Exemplo de lógica de seleção não absoluta, mapeamento em memória

#### Faixas de endereço para a figura 4

a)Y0: 0000H -> 0FFF H(4k x 8)

b) Y2 : 2000H -> 2FFFH (4k x 8)

A memória conectada a Y2 é de 2k x 8 , organização menor do que o espaço gerado pela lógica de seleção.

O bit de endereço A11 não está presente na lógica de seleção para a memória de 2k x 8, o que leva essa memória a ter dois espaços de endereço associados a ela

Faixa de endereço para a memória RAM de 2Kx8

```

Se X = 0 a faixa de endereço = 2000H a 27FFH

Se X = 1 a faixa de endereço = 2800H a 2FFFH

```

- Um dos espaços de 2k x 8 é denominado de espaço fantasma (espelho).

- Qualquer uma das duas faixas de endereço pode ser escolhida como a fantasma.

- endereço 2000H e 2800H endereçam a mesma posição física do CHIP

- •(linhas de endereçamento do chip são iguais a zero para esses dois endereços).

c. Faixa de endereço para interface de 4 x 8

```

Y14: E000H -> EFFFH (4Kx8)

```

- 1ª. Faixa de endereço da interface: E000 -> E003H

- 2ª. Faixa de endereço da interface: E004 -> E007H

Quantas faixas de endereço estarão associadas a essa interface?

## 3.2.b. - Exemplo de lógica de seleção não absoluta, mapeamento I/O isolado

Determine a faixa de endereço para cada saída de seleção, e os endereços fantasmas

79

## Exemplos

#### Exercício 1 da Lista nº9

Faça o projeto da lógica de seleção para dividir o espaço de endereço do microprocessador em blocos de 4Kbytes, especificando endereço inicial e final de cada bloco. Divida o bloco que inicia no endereço 4000H, em blocos de 1Kbytes e o bloco que inicia no endereço A000H em blocos de 512 bytes. Usando lógica de seleção absoluta, ligue uma memória de 2kbytes, a partir do endereço 1000H, outra a partir do endereço 4000H e outraa partir do endereço A000H, determinando o endereço final de cada memória. Repita o mesmo para lógica de seleção não absoluta, determinando os endereços fantasmas. Justifique quando a lógica de seleção absoluta não se aplicar.

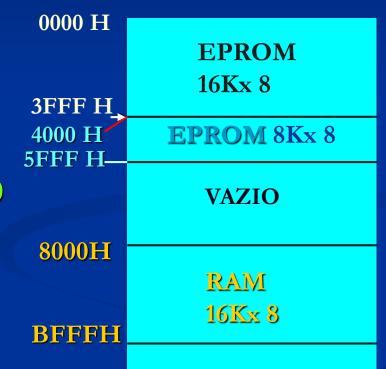

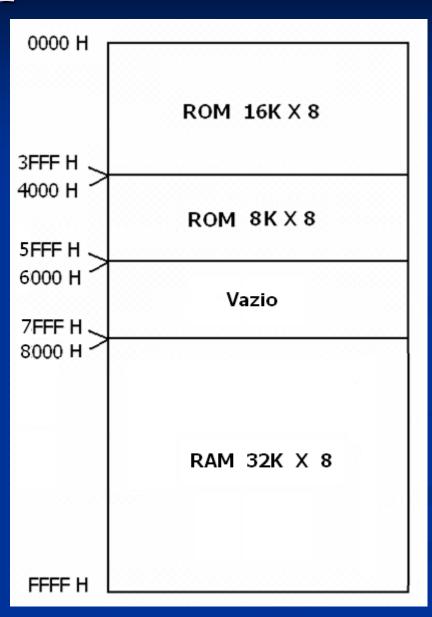

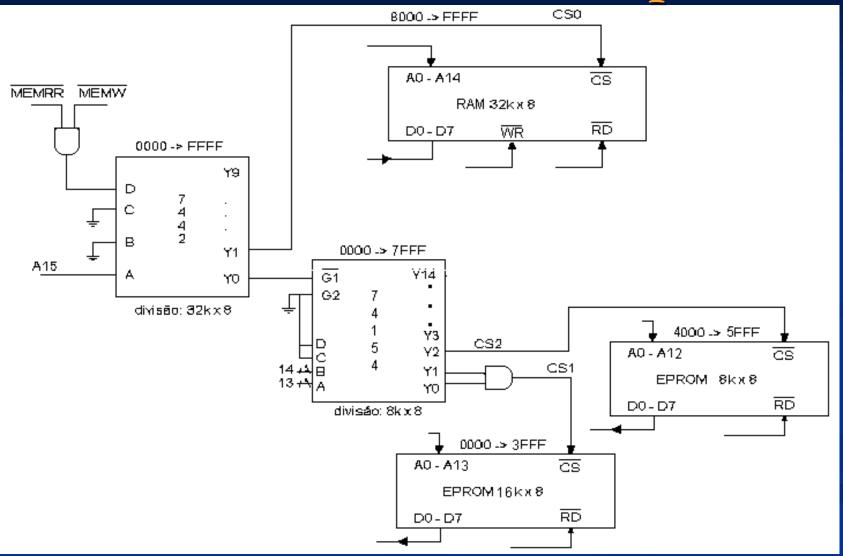

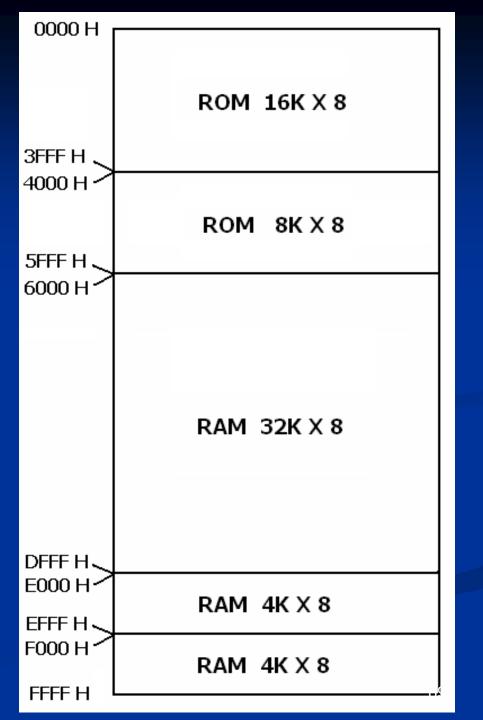

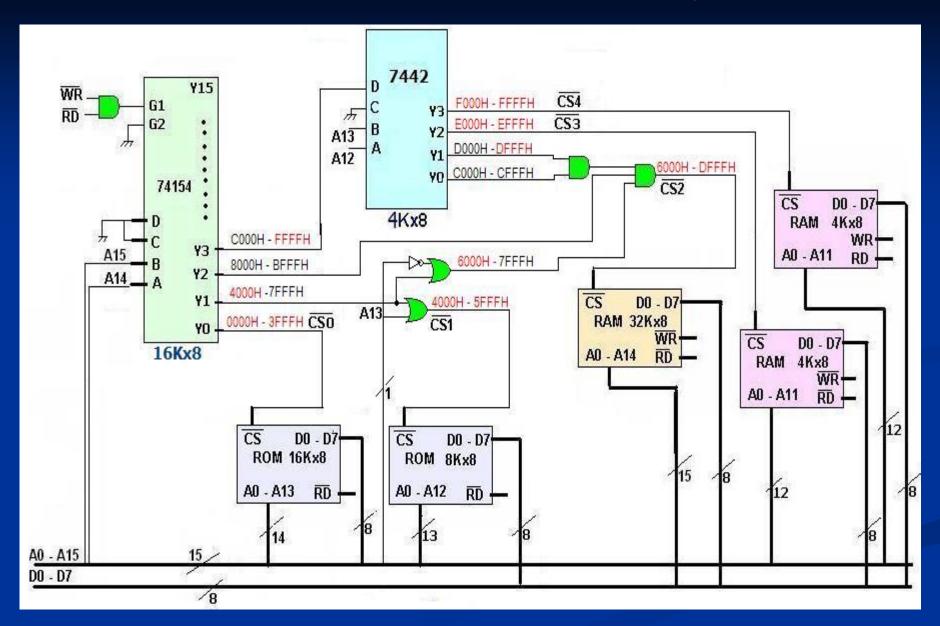

#### Ex. 3: Endereçamento de um bloco de memórias utilizando

Decodificação Absoluta

3 Memórias na seqüência

**Com** alinhamento dos CIs

- ROM 16 k x 8

- ROM 8 k x 8

- RAM 32 k x 8

# Lógica de Seleção – Decodif. Absoluta com alinhamento das memórias

| Lógic | ea d | le E | nd  | ere | çan         | nen | to c      | do p      | ιP -      | - <b>E</b> : | nde       | ereç      | o d       | le d      | ado       | OS        | M          | lemór | ia      |

|-------|------|------|-----|-----|-------------|-----|-----------|-----------|-----------|--------------|-----------|-----------|-----------|-----------|-----------|-----------|------------|-------|---------|

| Tipo  | A15  | A14  | A13 | A12 | <b>A</b> 11 | A10 | <b>A9</b> | <b>A8</b> | <b>A7</b> | <b>A6</b>    | <b>A5</b> | <b>A4</b> | <b>A3</b> | <b>A2</b> | <b>A1</b> | <b>A0</b> | Início (H) |       | Fim (H) |

| ROM   | 0    | 0    | 0   | 0   | 0           | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 0000       | 16k   |         |

| KOWI  | 0    | 0    | 1   | 1   | 1           | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1         | 1         | 1         |            | TOK   | 3FFF    |

| ROM   | 0    | 1    | 0   | 0   | 0           | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 4000       | 8 k   |         |

| KOWI  | 0    | 1    | 0   | 1   | 1           | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1         | 1         | 1         |            | OK    | 5FFF    |

| RAM   | 1    | 0    | 0   | 0   | 0           | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 8000       | 32 k  |         |

| KAWI  | 1    | 1    | 1   | 1   | 1           | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1         | 1         | 1         |            | 32 K  | FFFF    |

| Vazio | 0    | 1    | 1   | 0   | 0           | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0         | 0         | 0         | 6000       | 8 k   |         |

| vazio | 0    | 1    | 1   | 1   | 1           | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1         | 1         | 1         |            | O K   | 7FFF    |

### Mapeamento da Memória

### Circuito Final - Exemplo 1

## Circuito Final - Exemplo 2

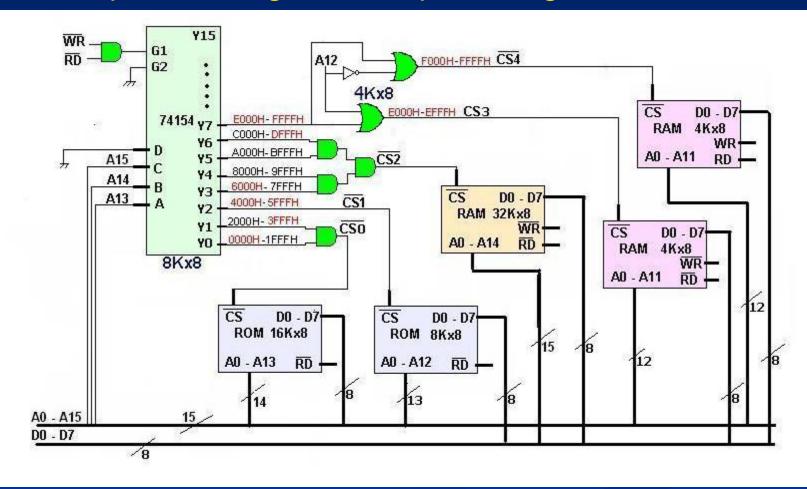

#### Ex. 4: Endereçamento de um bloco de memórias utilizando

Decodificação Absoluta:

5 Memórias na seqüência

Sem o alinhamento dos Cls

- ROM 16 k x 8

- ROM 8 k x 8

- RAM 32 k x 8

- 2 x RAM 4 k x 8

### Lógica de Seleção – Decodif. Absoluta

| Lógic  | ea d | le E | nd  | ere | çan        | nen | to c      | do p      | ιP -      | – <b>E</b> i | nde       | ereç      | o d       | e d | ado        | )S        | Memória     |      |         |  |

|--------|------|------|-----|-----|------------|-----|-----------|-----------|-----------|--------------|-----------|-----------|-----------|-----|------------|-----------|-------------|------|---------|--|

| Tipo   | A15  | A14  | A13 | A12 | <b>A11</b> | A10 | <b>A9</b> | <b>A8</b> | <b>A7</b> | <b>A6</b>    | <b>A5</b> | <b>A4</b> | <b>A3</b> | A2  | <b>A</b> 1 | <b>A0</b> | Início (H)  |      | Fim (H) |  |

| DOM    | 0    | 0    | 0   | 0   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0   | 0          | 0         | 0000        | 16k  |         |  |

| ROM    | 0    | 0    | 1   | 1   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1   | 1          | 1         |             | TOK  | 3FFF    |  |

| ROM    | 0    | 1    | 0   | 0   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0   | 0          | 0         | 4000        | 8 k  |         |  |

| KOM    | 0    | 1    | 0   | 1   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1   | 1          | 1         |             | 0 K  | 5FFF    |  |

| RAM    | 0    | 1    | 1   | 0   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0   | 0          | 0         | 6000        | 32k  |         |  |

|        | 1    | 1    | 0   | 1   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1   | 1          | 1         |             |      | DFFF    |  |

| RAM    | 1    | 1    | 1   | 0   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0   | 0          | 0         | <b>E000</b> | 4 k  |         |  |

|        | 1    | 1    | 1   | 0   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1   | 1          | 1         |             | 1 1  | EFFF    |  |

| RAM    | 1    | 1    | 1   | 1   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0         | 0   | 0          | 0         | F000        | 4 k  |         |  |

| 201111 | 1    | 1    | 1   | 1   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1         | 1   | 1          | 1         |             | T IX | FFFF    |  |

O CI de memória RAM 32K x 8, nesse caso, não será endereçado na seqüência normal (0000h – 7FFFh). Mesmo assim, TODOS os seus endereços serão utilizados.<sub>88</sub>

# Mapeamento da Memória

## Decodificação Absoluta

Obs: Memória de 32Kx8 não alinhada

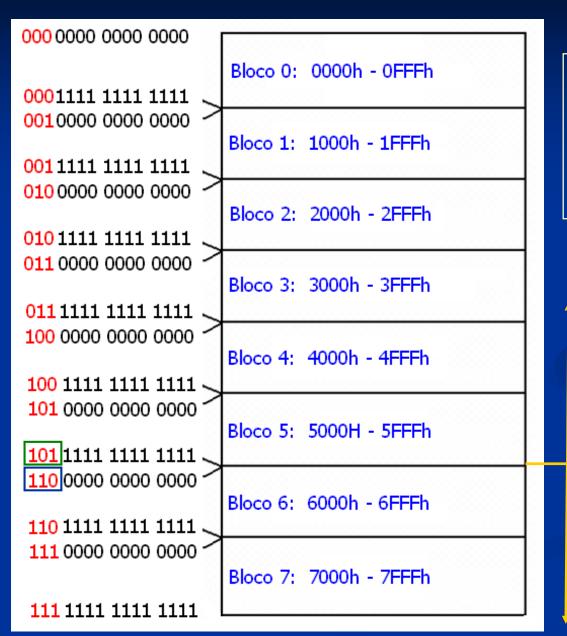

### Como é endereçada a Memória RAM 32K x 8 não alinhada?

A sequência de seleção da memória RAM 32K x 8 nesse caso será:

Blocos:

$$6 \rightarrow 7 \rightarrow 0 \rightarrow 1 \rightarrow 2 \rightarrow 3 \rightarrow 4 \rightarrow 5$$

$\begin{array}{ccccc} A_{15} A_{14} A_{13} A_{12} \\ 1 & 1 & 0 & 1 \end{array}$

Bloco 5 será o último a ser selecionado

$A_{15} A_{14} A_{13} A_{12}$

0 1 1 0

Bloco 6 será o primeiro a ser selecionado

90

## Decodificação Absoluta

| Lógic | a d | le E | nd  | ere | çan | nen | to c       | do į      | ιP-        | – <b>E</b> i | nde        | ereç      | o d        | e d | ado | OS | M          | lemór        | ia      |

|-------|-----|------|-----|-----|-----|-----|------------|-----------|------------|--------------|------------|-----------|------------|-----|-----|----|------------|--------------|---------|

| Tipo  | A15 | A14  | A13 | A12 | A11 | A10 | <b>A</b> 9 | <b>A8</b> | <b>A</b> 7 | A6           | <b>A</b> 5 | <b>A4</b> | <b>A</b> 3 | A2  | A1  | A0 | Início (H) |              | Fim (H) |

| DOM   | 0   | 0    | 0   | 0   | 0   | 0   | 0          | 0         | 0          | 0            | 0          | 0         | 0          | 0   | 0   | 0  | 0000       | 1.01-        |         |

| ROM   | 0   | 0    | 1   | 1   | 1   | 1   | 1          | 1         | 1          | 1            | 1          | 1         | 1          | 1   | 1   | 1  |            | 16k          | 3FFF    |

| ROM   | 0   | 1    | 0   | 0   | 0   | 0   | 0          | 0         | 0          | 0            | 0          | 0         | 0          | 0   | 0   | 0  | 4000       | 8 k          |         |

|       | 0   | 1    | 0   | 1   | 1   | 1   | 1          | 1         | 1          | 1            | 1          | 1         | 1          | 1   | 1   | 1  |            | O K          | 5FFF    |

| RAM   | 0   | 1    | 1   | 0   | 0   | 0   | 0          | 0         | 0          | 0            | 0          | 0         | 0          | 0   | 0   | 0  | 6000       | 32k          |         |

|       | 1   | 1    | 0   | 1   | 1   | 1   | 1          | 1         | 1          | 1            | 1          | 1         | 1          | 1   | 1   | 1  |            | <i>52</i> 11 | DFFF    |

| RAM   | 1   | 1    | 1   | 0   | 0   | 0   | 0          | 0         | 0          | 0            | 0          | 0         | 0          | 0   | 0   | 0  | E000       | 4 k          |         |

|       | 1   | 1    | 1   | 0   | 1   | 1   | 1          | 1         | 1          | 1            | 1          | 1         | 1          | 1   | 1   | 1  |            | ı K          | EFFF    |

| RAM   | 1   | 1    | 1   | 1   | 0   | 0   | 0          | 0         | 0          | 0            | 0          | 0         | 0          | 0   | 0   | 0  | F000       | 4 k          |         |

|       | 1   | 1    | 1   | 1   | 1   | 1   | 1          | 1         | 1          | 1            | 1          | 1         | 1          | 1   | 1   | 1  |            | I IX         | FFFF    |

#### 1º Exemplo de Implementação:

## Como é endereçada a Memória RAM 32K x 8 não alinhada para o exemplo 1?

0110 0000 0000 0000

**0111** 1111 1111 1111 **1000** 0000 0000

1101 1111 1111 1111

Bloco 3: 6000 -7FFFF

Bloco 0: 8000 -9FFFF

Bloco 1: A000 -BFFFF

Bloco 2: C000 -DFFFF

A sequência de seleção da memória RAM 32K x 8 nesse caso será:

Blocos:  $1 \rightarrow 2 \rightarrow 3 \rightarrow 0$

#### Memória de 32Kx8

Bloco 0: (A14,A13) = (0,0)

Bloco 1: (A14,A13) = (0,1)

Bloco 2: (A14,A13) = (1,0)

Bloco 3: (A14,A13) = (1,1)

### 2º Exemplo de Implementação:

#### Exemplo de Implementação INCORRETA:

Obs: a lógica de seleção deve ser feita com decodificadores e não com uma quantidade grande de portas lógicas OR e AND

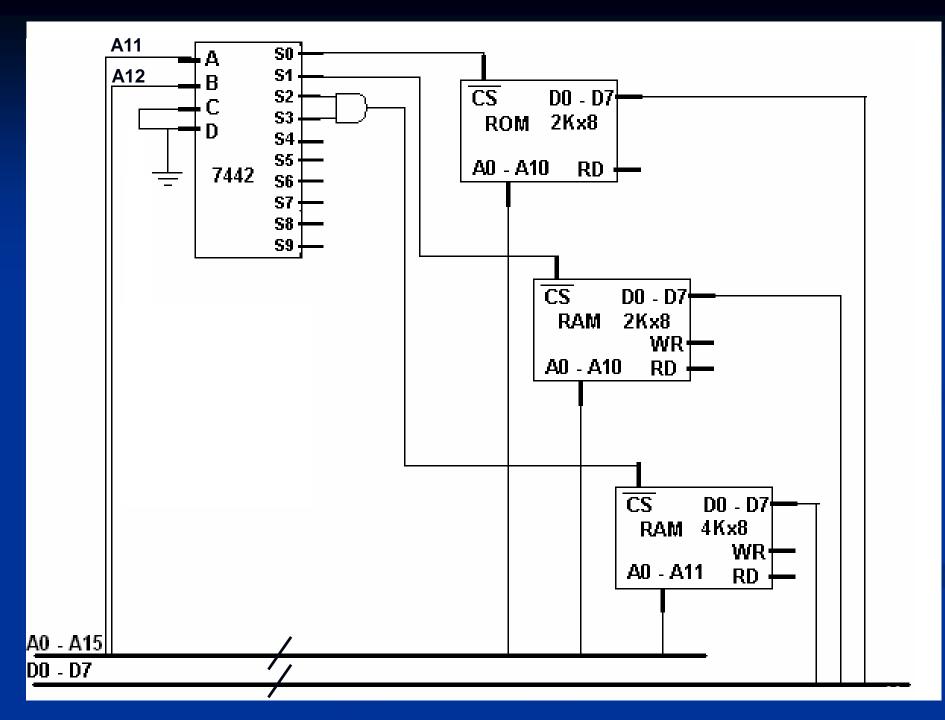

#### Ex. 5: Endereçamento de um bloco de memórias utilizando

Decodificação Não-Absoluta:

3 Memórias na seqüência

**Com** alinhamento dos Cls

- ROM 2 k x 8

- RAM 2 k x 8

- RAM 4 k x 8

## Lógica de Seleção – Decodif. Não-Absoluta

| Lógic  | ea d | le E | Cnd         | ere | çan        | nen | to c      | do į      | μP -      | – <b>E</b> : | nde       | ereç      | o d        | le d      | ado       | OS        | Memória    |             |             |  |

|--------|------|------|-------------|-----|------------|-----|-----------|-----------|-----------|--------------|-----------|-----------|------------|-----------|-----------|-----------|------------|-------------|-------------|--|

| Tipo   | A15  | A14  | <b>A</b> 13 | A12 | <b>A11</b> | A10 | <b>A9</b> | <b>A8</b> | <b>A7</b> | <b>A6</b>    | <b>A5</b> | <b>A4</b> | <b>A</b> 3 | <b>A2</b> | <b>A1</b> | <b>A0</b> | Início (H) |             | Fim (H)     |  |

|        | •    |      |             |     | 0          | 0   | 0         | 0         |           |              | 0         | 0         | 0          |           |           |           | 0000       |             |             |  |

| ROM    | U    | U    | U           | U   | U          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0          | 0         | 0         | 0         | 0000       | 2 k         |             |  |

| ROM    | 0    | 0    | 0           | 0   | 0          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1          | 1         | 1         | 1         |            | <b>2</b> 11 | <b>07FF</b> |  |

| RAM    | 0    | 0    | 0           | 0   | 1          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0          | 0         | 0         | 0         | 0800       | 2 k         |             |  |

|        | 0    | 0    | 0           | 0   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1          | 1         | 1         | 1         |            | 2 K         | <b>OFFF</b> |  |

| RAM    | 0    | 0    | 0           | 1   | 0          | 0   | 0         | 0         | 0         | 0            | 0         | 0         | 0          | 0         | 0         | 0         | 1000       | 4 k         |             |  |

| IVAIVI | 0    | 0    | 0           | 1   | 1          | 1   | 1         | 1         | 1         | 1            | 1         | 1         | 1          | 1         | 1         | 1         |            | T K         | 1FFF        |  |

## Decodificação Não-Absoluta

| Lógic  | ca d     | le E | End | ere | çan         | nen | to c      | do į      | μP -       | – <b>E</b> i | nde        | ereç | go d | le d      | ado        | OS | Memória    |     |             |  |

|--------|----------|------|-----|-----|-------------|-----|-----------|-----------|------------|--------------|------------|------|------|-----------|------------|----|------------|-----|-------------|--|

| Tipo   | A15      | A14  | A13 | A12 | <b>A</b> 11 | A10 | <b>A9</b> | <b>A8</b> | <b>A</b> 7 | <b>A</b> 6   | <b>A</b> 5 | A4   | А3   | <b>A2</b> | <b>A</b> 1 | A0 | Início (H) |     | Fim (H)     |  |

|        | 0        | 0    | 0   | 0   | 0           | 0   | 0         | 0         | 0          | 0            | 0          | 0    | 0    | 0         | 0          | 0  | 0000       |     |             |  |

| ROM    |          | 0    | 0   | 0   | 0           | 1   | 1         | 1         | 1          | 1            | 1          | 1    | 1    | 1         | 1          | 1  | 0000       | 2 k | 07FF        |  |

|        | $0 \\ 0$ | 0    | 0   | 0   | 1           | 0   | 0         | 0         | 0          | 0            | 0          | 0    | 0    | 0         | 0          | 0  | 0800       |     | U/II        |  |

| RAM    |          | U    | U   | U   | 1           | 0   | U         | U         |            | U            | U          | U    | 0    | U         | U          | U  | 0000       | 2 k |             |  |

|        | 0        | 0    | 0   | 0   | 1           | 1   | 1         | 1         | 1          | 1            | 1          | 1    | 1    | 1         | 1          | 1  |            |     | <b>OFFF</b> |  |

| RAM    | 0        | 0    | 0   | 1   | 0           | 0   | 0         | 0         | 0          | 0            | 0          | 0    | 0    | 0         | 0          | 0  | 1000       | 4 k |             |  |

| IVAIVI | 0        | 0    | 0   | 1   | 1           | 1   | 1         | 1         | 1          | 1            | 1          | 1    | 1    | 1         | 1          | 1  |            | T K | 1FFF        |  |

Esse bloco é "espelhado" mais 8 vezes até o endereço final (FFFFh)

# Mapeamento da Memória

## **FIM**