### Configurações das Portas Lógicas

#### Aula 3

Profa. Luiza Maria Romeiro Codá Profa. Dra. Maria Stela Veludo de Paiva

#### sistemas digitais x sistemas analógicos

Sistemas digitais: as variáveis estão limitadas a um número finito de valores (variação discreta)

Sistemas analógicos: as variáveis podem assumir um número infinito de valores (variação contínua)

#### Em termos simplificados, os transístores:

- · nos circuitos analógicos funcionam em modo linear

- nos circuitos digitais funcionam em modo de comutação ( corte e saturação)

#### Portas Lógicas TTL (ou CMOS)

- Utilizam transistor bipolar (ou MOSFET) como elemento principal na fabricação;

- Transistor é uma junção de semicondutores

NPN ou PNP

- A análise do funcionamento das portas será baseado no funcionamento do transistor que se comportam como chave eletrônica:

- estão em condução ("1")

- ou estão ao corte ("0")

#### Estágio da Saída de Portas Lógicas

- Há três tipos de circuito de saída usados em portas lógicas :

- totem pole

- coletor aberto

- *3– state*

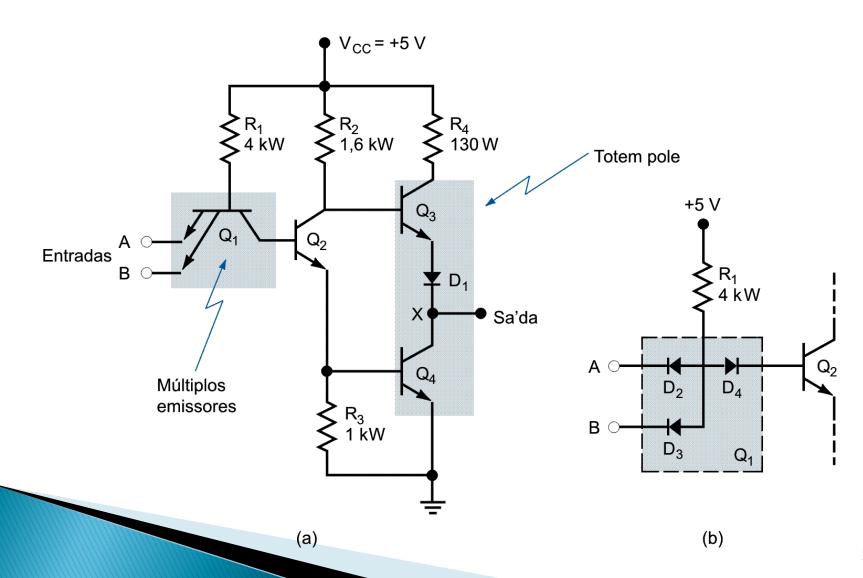

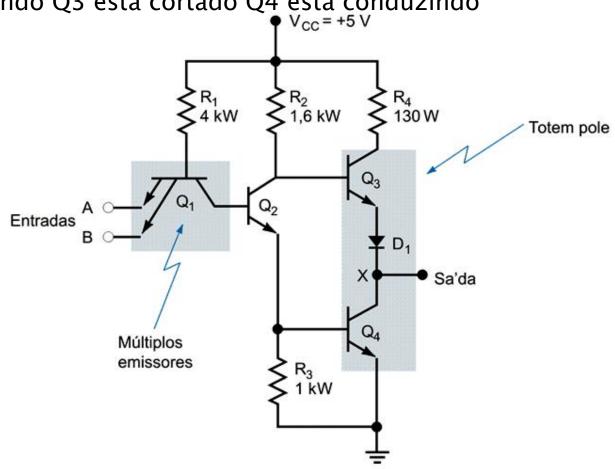

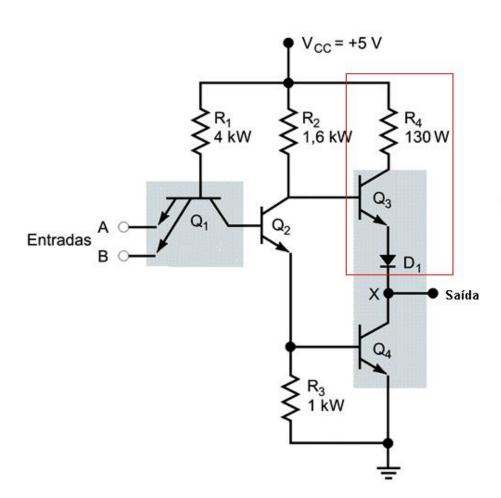

### Porta NAND TTL (totem pole)

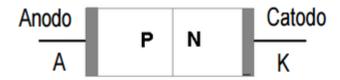

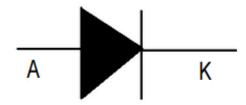

#### Diodo

Diodo: junção de dois semicondutores PN

Semicondutor tipo P ( excesso de lacunas);

Semicondutor tipo N (excesso de elétrons);

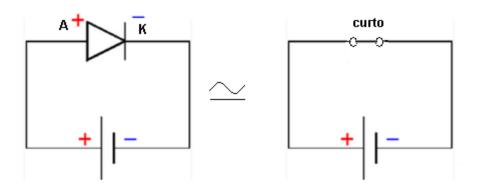

### Funcionamento do diodo: Modelo simplificado

Polarizado diretamente: conduz

### Funcionamento do diodo: Modelo simplificado

Polarizado reversamente: cortado

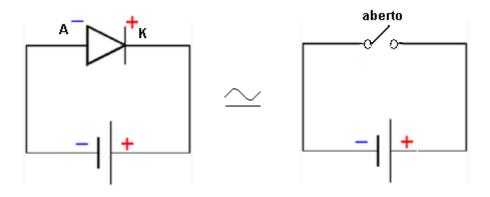

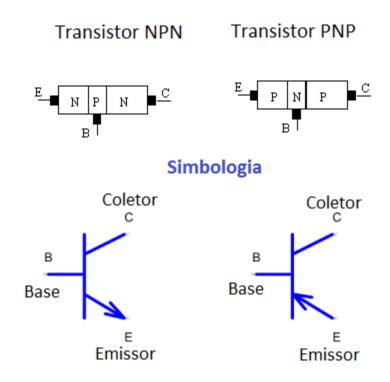

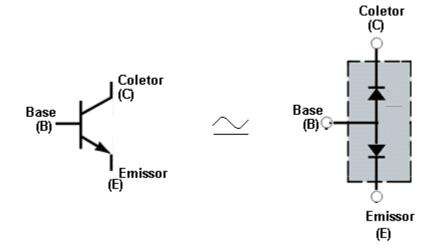

#### Transistor de junção bipolar

### de junção bipolar NPN e PNP http://www.arvm.org/exames/trasistor. htm

Ref Fig https://www.google.com.br/search?q=tens%C3%B5es+e+Correntes+nos+Trans%C3%ADstores+NPN+e+PNP&source=Inms&tbm=isch&sa=X&ved=0ahUK-5u-zOAhWCIZAKHf2FAGqQ\_AUICSqC&biw=1024&bih=623#imqrc=vLhIFeTn3SbhbM%3A

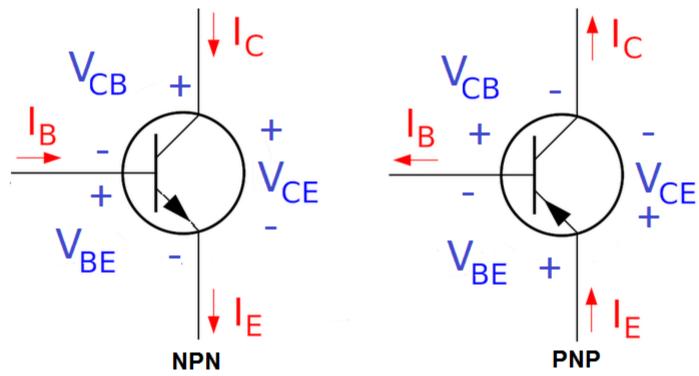

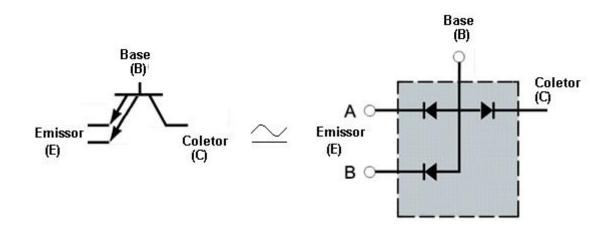

#### Modelo simplificado do transistor

### Modelo simplificado do transistor com 2 emissores

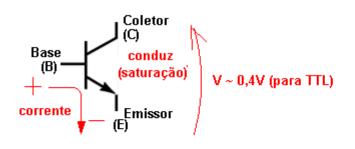

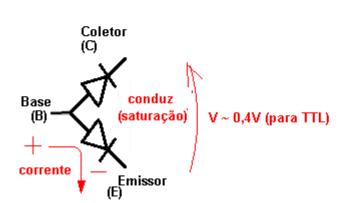

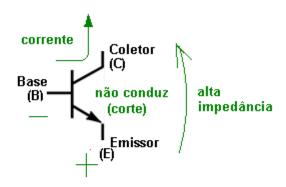

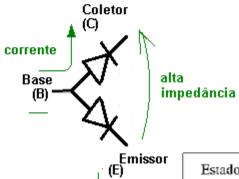

# Modelo simplificado do funcionamento do transistor no corte e saturação http://www.arvm.org/exames/trasistor.htm

Transistor na saturação

Transistor no corte

| Estado   | Polarização     | Circuito equivalente |

|----------|-----------------|----------------------|

| Condução | <del>-</del>    |                      |

| Bloqueio | <del>-</del> >+ | ~~~                  |

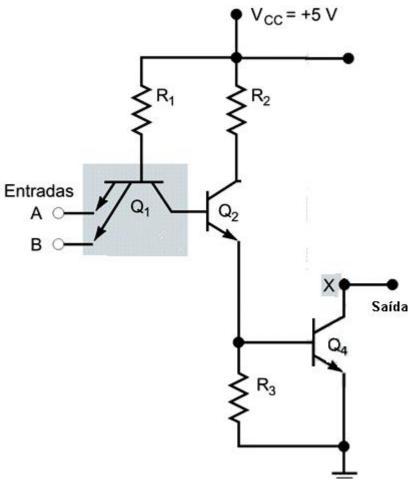

#### Porta NAND TTL (totem pole)

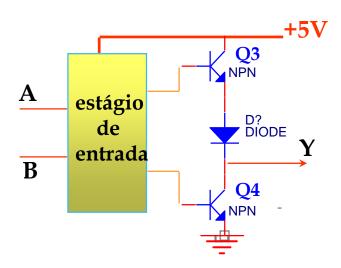

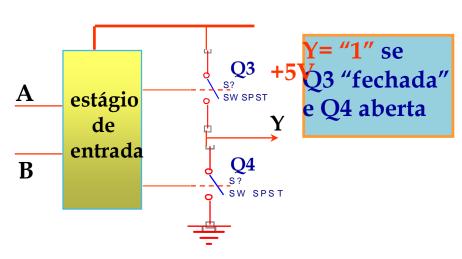

Na configuração Totem Pole:

quando o transistor Q3 está conduzindo Q4 está cortado e quando Q3 está cortado Q4 está conduzindo

### Porta NAND TTL - estágio de saída (Totem Pole) representado por chaves

A 1 U?A

2 7400 Y

Computação

Departamento de Engenharia Elétrica e de

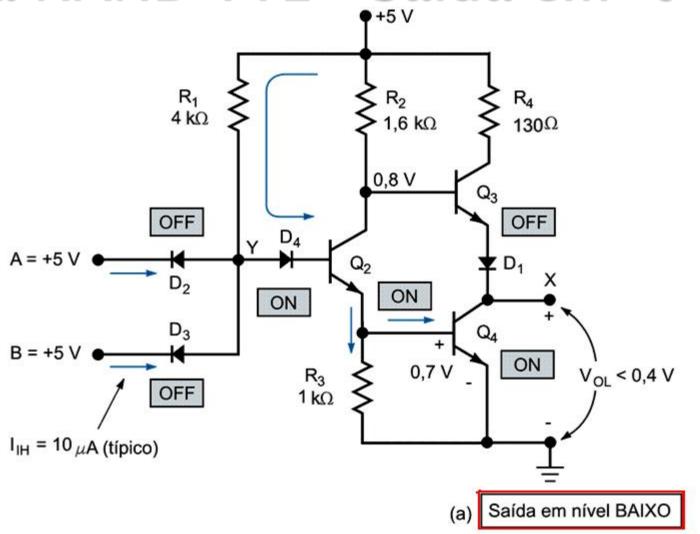

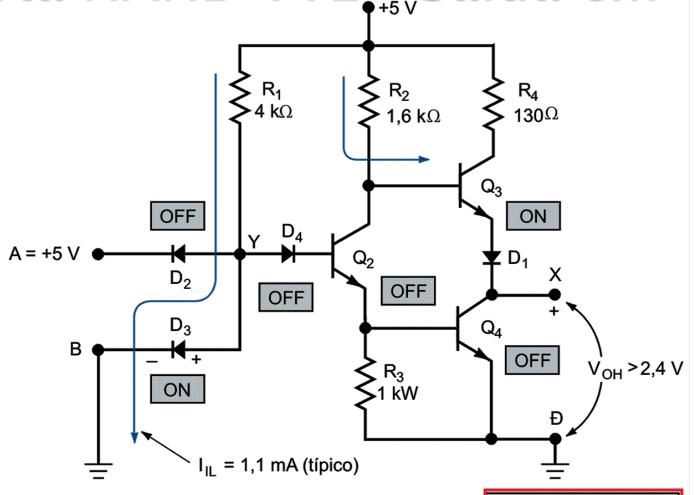

Na fig. a., Q3 e Q4 operam em oposição, nas regiões de corte e saturação

Na fig. b. se Q3 ou Q4 estão na saturação, a chave está fechada.

fig. a - estágio de saída da porta padrão - configuração "totem pole"

fig. b - representação do circuito da fig a.1 por chaves.

#### Porta NAND TTL - Saída em "0"

Departamento de Engenharia Elétrica e de Computação

(b) Saída em nível ALTO

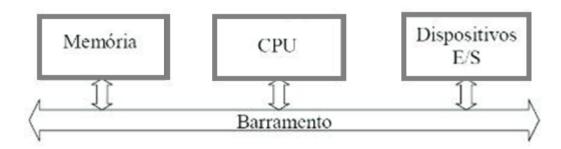

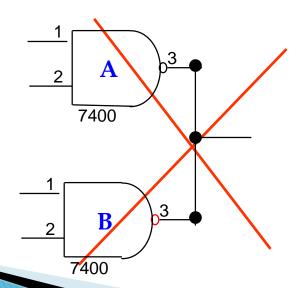

### Ligação de Portas lógicas

Ex: sistemas microprocessados:

- Necessidade de compartilhamento de duto (fio)

- Uma saída em alto e outra em baixo conectadas juntas ⇒ PROBLEMA

Departamento de Engenharia Elétrica e de

### Ligação de Portas lógicas TTL

- Necessidade de comparti-Ihamento de duto (fio) Computação

- Uma saída em alto e outra em baixo conectadas juntas

- → PROBLEMA

Computação

Departamento de Engenharia Elétrica e de

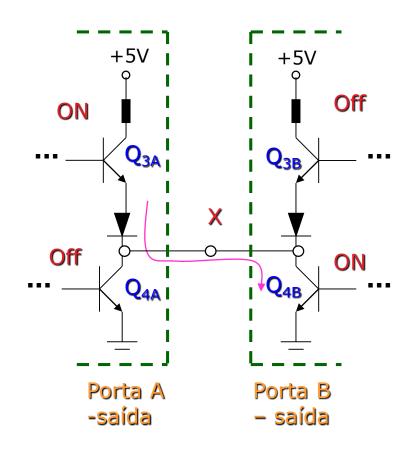

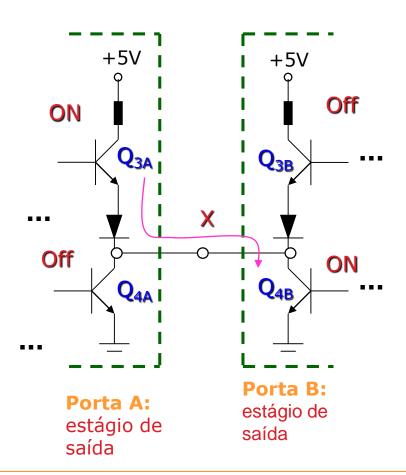

Se a saída de A = '1' (alto) ⇒

$Q_{3A}$  conduz e  $Q_{4A}$  cortado

Se a saída de B = 0' (baixo)  $\Rightarrow$ Q<sub>3B</sub> cortado e Q<sub>4B</sub> conduz

Q<sub>4B</sub> drenará uma corrente muito alta(representará uma resistência muito baixa comparada a Q<sub>3A</sub>)

**SOLUÇÃO DO FABRICANTE** → remover o transistor ativo (Q3) do circuito deixando Q4 com coletor (dreno)

aberto

#### CIRCUITO COM SAÍDA EM TOTEM POLE

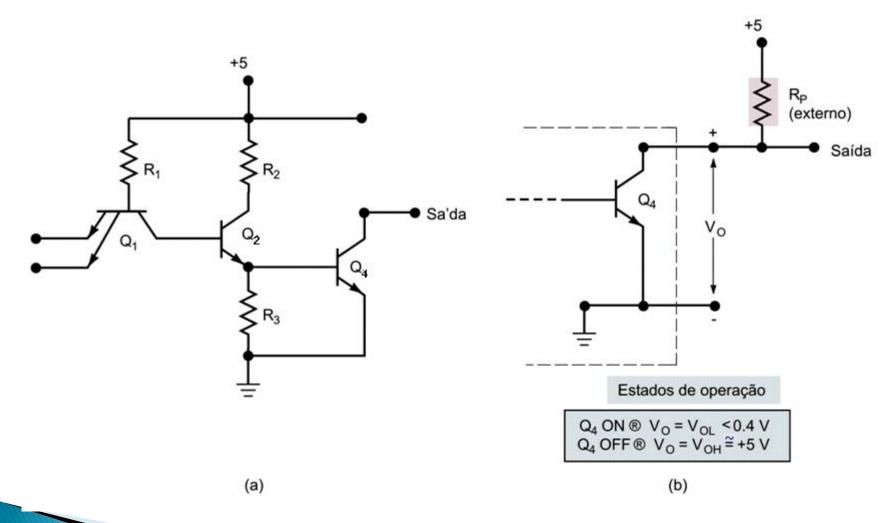

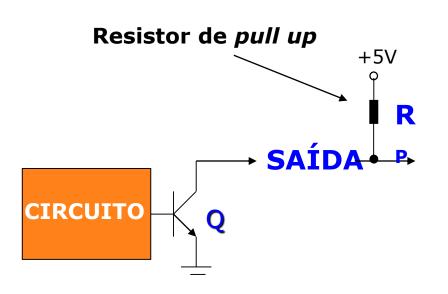

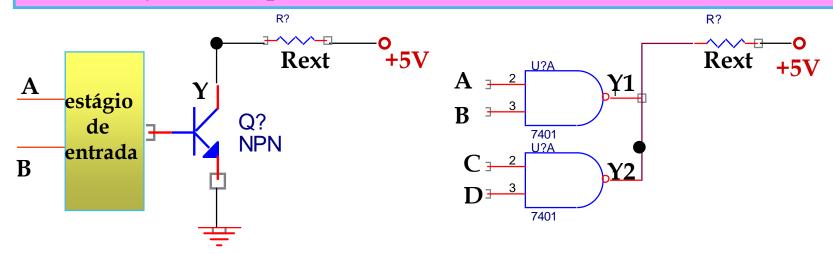

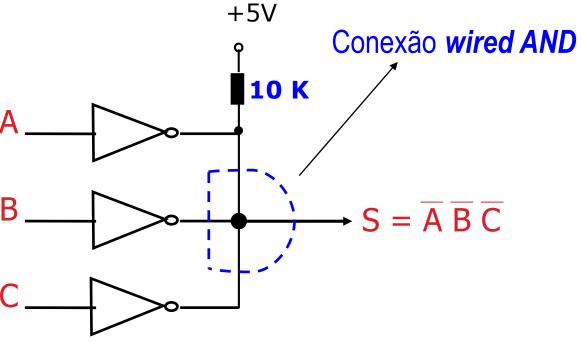

### CIRCUITOS DE SAÍDA EM COLETOR ABERTO

### CIRCUITOS DE SAÍDA EM COLETOR ABERTO

- ⇒ Se Q conduz ("ligado")

- $\rightarrow$  S = 0

- ⇒ Se Q cortado ("aberto")

- → S = 1\*

- Com saída em 0 (baixo) → Q conduzindo

- Com saída em 1 (alto) → Q cortado → CIRCUITO ABERTO → necessidade de R<sub>p</sub>

\* sem R<sub>p</sub> → V<sub>o</sub> seria indeterminada (flutuante)

#### Portas de coletor aberto:

- □ são portas cujo <u>estágio de saída</u> tem somente <mark>um transistor.</mark>

- ☐ Como o coletor do transistor está aberto a porta funcionará corretamente somente quando for conectado um resistor "elevador" ("pul up") externo, Rext.

Essas portas podem ter suas saídas conectadas juntas e ligadas a um resistor comum, cujo valor depende do número de saídas

fig.a. - Estágio de saída de uma porta coletor aberto

fig.b. - Portas NAND, 7401, saída coletor aberto, com saídas Y1 eY2 conectadas

- $\Rightarrow$  Se uma ou mais saídas  $\rightarrow$  0  $\Rightarrow$  S = 0 (o zero "vence")

- ⇒ S = 1 apenas se todas as saídas = 1

- Mais lento e maior dissipação de potência do que o TTL normal

- EX. DE APLICAÇÕES:

- → Drivers

- *→ 7407 30V/40mA*

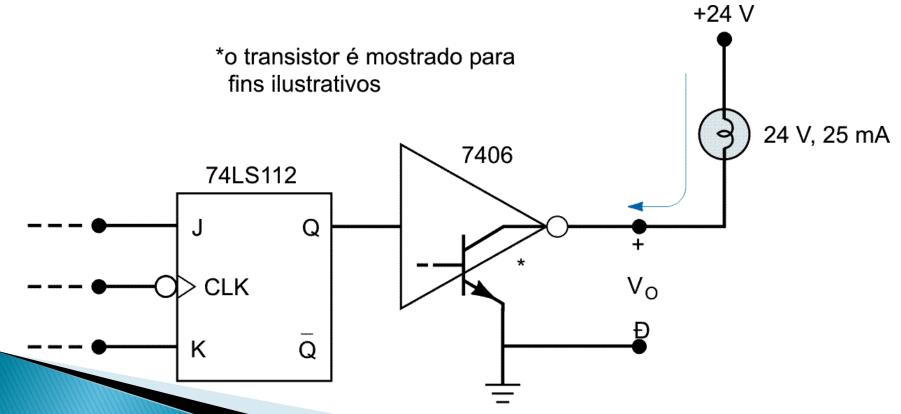

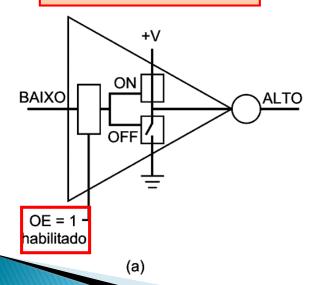

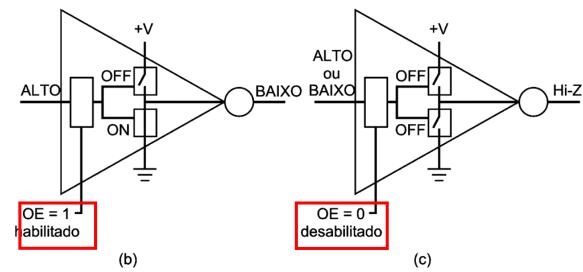

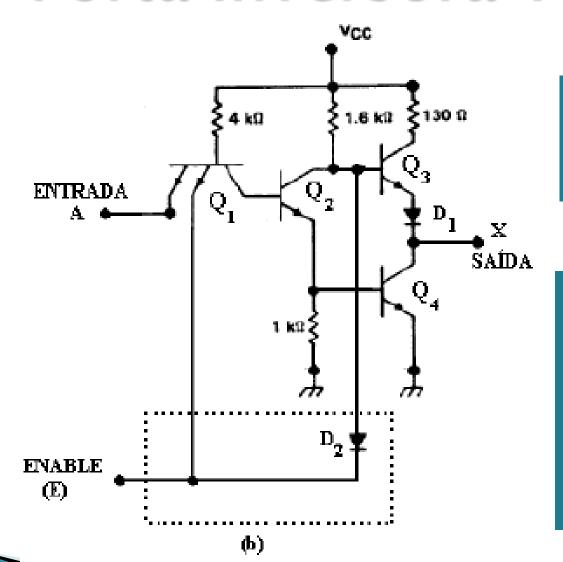

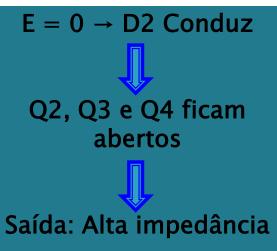

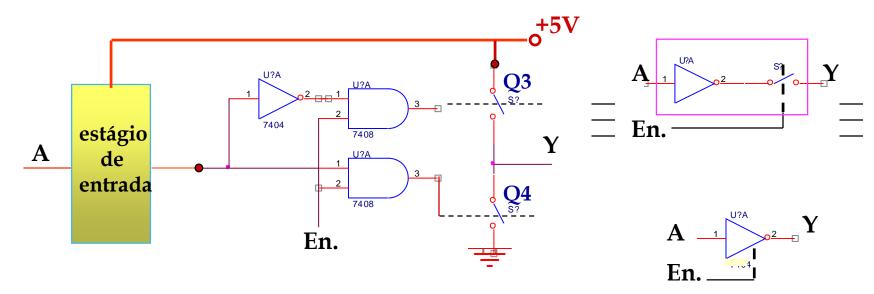

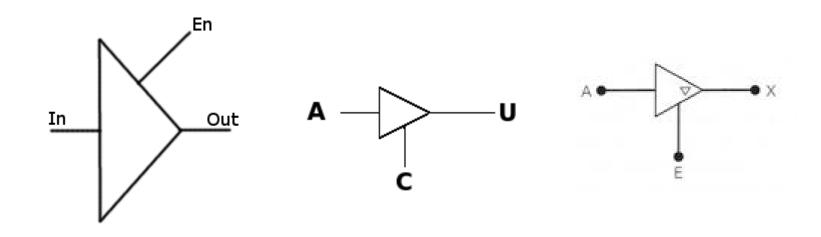

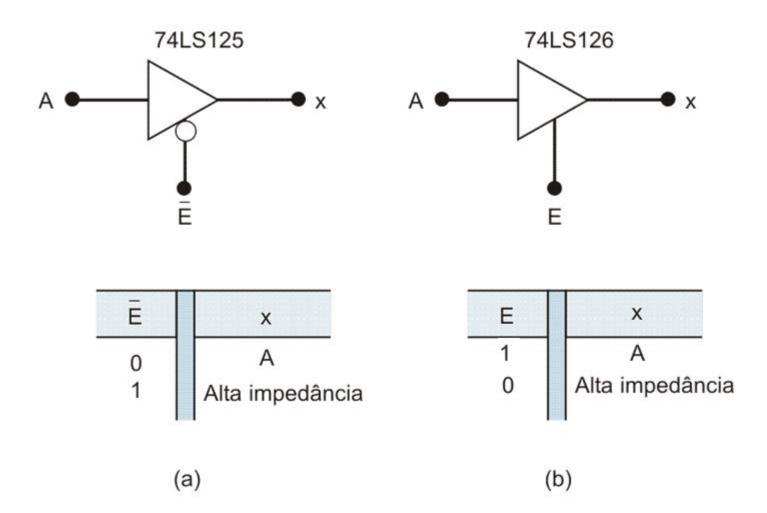

### CIRCUITOS COM SAÍDA 3-STATE

- Necessidade também de compartilhamento de duto

- Característica ⇒ S em Alto

- Baixo

- Alta impedância

**OE** é a entrada de controle do 3-state

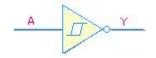

### Porta Inversora Tri-State

#### Saídas 3-State

#### Estágio de saída de uma porta 3-state

fig. a.3.1 - Estágio de saída de uma porta inversora, representado por chaves

Se En = "0", Q1 e Q2 permanecem abertos e a saída Y fica em alta impedância, estado esse representado pela letra  $\mathbb{Z}$ .

#### Saídas 3-State

- Saídas de CIs com *3-state* podem ser conectadas juntas sem causar problemas à velocidade de chaveamento (mesma velocidade dos TTL comuns)

- Quando várias portas *3-state* são ligadas juntas, apenas uma deve ser habilitada por vez! (pode danificar o dispositivo, pois se torna um totem-pole quando

habilitado)

| A  | 74126    |         |

|----|----------|---------|

| G1 |          |         |

| В  | 74126    | SAÍDA S |

| G2 | <u> </u> |         |

| С  | 74126    |         |

| G3 | 7/       | •       |

| G1 | G2 | G3 | S |

|----|----|----|---|

| 1  | 0  | 0  | Α |

| 0  | 1  | 0  | В |

| 0  | 0  | 1  | С |

# Símbolos de Buffers tristate (não inversores)

#### Buffers tristate não inversores

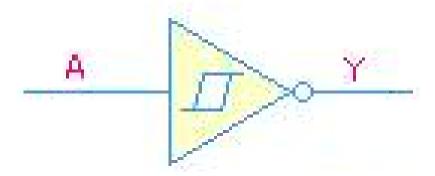

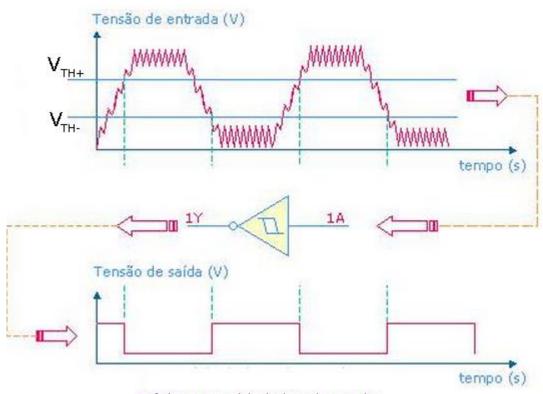

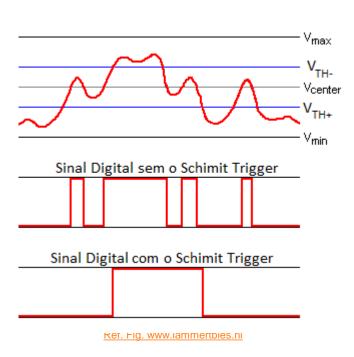

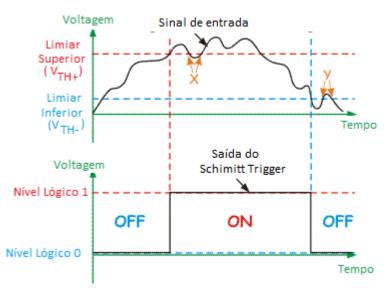

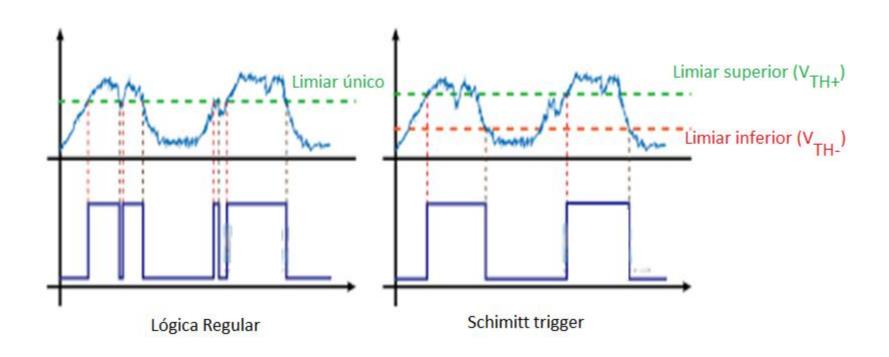

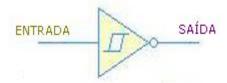

Em muitas aplicações práticas o sinal de entrada de um circuito digital (clock) pode não ser perfeito, prejudicando consideravelmente o funcionamento do circuito que dele dependem. Esse sinais podem apresentar:

- ✓ transição lenta do nível baixo para o nível alto ou vice versa;

- ✓ Ruído ("bounce"), comuns em circuito de comutação

#### **Funcionamento:**

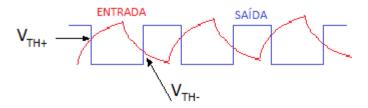

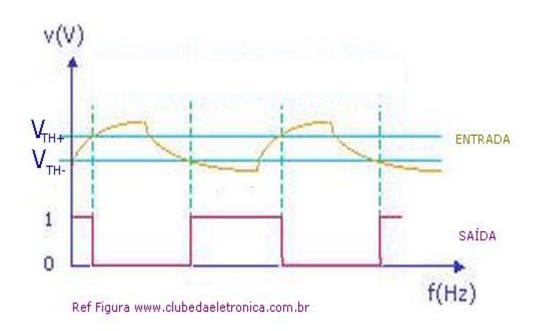

A porta inversora ShimiTT Trigger opera com duas tensões de referência, uma inferior  $V_{TH-}$  e outra superior  $V_{TH+}$ . Quando o sinal de entrada A atinge  $V_{TH+}$  (referência superior), a saída Y comuta de nível lógico alto para nível lógico baixo, permanecendo neste estado até que o sinal de entrada alcance  $V_{TH-}$  (referência inferior).

Aplicação em sinais de entrada com ruído ("bounce")

Ref Figura www.clubedaeletronica.com.br

Aplicação em sinais de entrada com ruído ("bounce")

Aplicação em sinais de entrada com ruído ("bounce")

Aplicação em sinais de entrada com Transição lenta

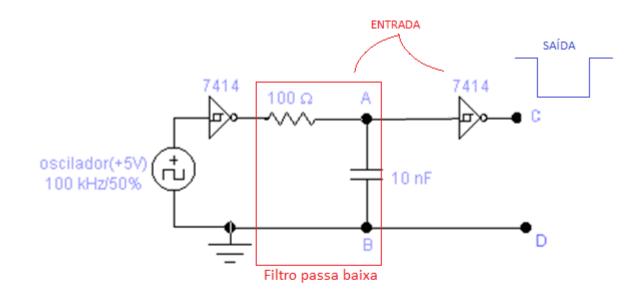

# Medida de $V_{TH+}$ e $V_{TH-}$ de uma porta SCHIMITT TRIGGER:

#### Medida no Osciloscópio