# Departamento de Engenharia Elétrica e de Computação/EESC-USP SEL 323 – Laboratório de Sistemas Digitais II Cronômetro

"Dispositivos de Lógica Programável Complexa CPLDs ("Complex Programmable Logic Devices")- "

### 1. Objetivos:

Utilização do programa QUARTUSII da empresa ALTERA no projeto, simulação e teste de circuitos seqüenciais em dispositivos "CPLDs"

### 2. Material utilizado:

- CPLD: EPM7128SLC84-7

- Kit de programação de CPLD da ALTERA.

- Multímetro.

## 3. Procedimento Experimental:

Utilizando o dispositivo CPLD EPM7128, projete, simule e teste os seguintes circuitos:

- **3.1** Projetar e programar um circuito que transforme a freqüência de relógio da placa de testes de 25,175MHz para uma freqüência de 10 Hz e visualize, utilizando os dez "LEDs" da placa, de tal maneira que um LED acenda a cada décimo de segundos.

- **3.2** Projete e implemente um cronômetro que conte 60 segundos. Mostrar a contagem nos displays de 7 segmentos da placa. Utilizar uma chave Push Botton (PB) para iniciar e parar a contagem, e uma outra zerar o cronômetro.

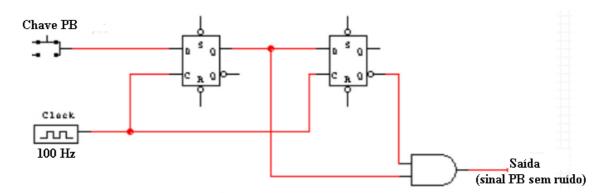

- **3.3** Para utilizar a chave PB, Implementar um eliminador de ruído de chave PB, mostrado na Figura 1, e ligar a chave PB à ele. O clock deve ter aproximadamente 100Hz. Explique como funciona o circuito da Figura 1 para eliminar o ruído da chave PB.

Figura 1

# 4. Bibliografia:

- Site da ALTERA

- Fregni, E. & Saraiva, A.M., "Engenharia do Projeto Lógico Digital", Ed. Edgard Blücher Ltda.

- Tocci, J. R., "Sistemas Digitais- Princípios e Aplicações